---

E C O L E

P O L Y T E C H N I Q U E

D E T U N I S I E

---

## MEMOIRE DE MASTERE SERC

Option: Communication et électronique

Réalisé par

**Mouna BAKLOUTI**

---

**Etude des modèles haut niveau d'architectures logicielles/matérielles pour la conception et l'évaluation des systèmes multiprocesseurs monopuces**

---

Préparé au: Laboratoire TIMA – Groupe SLS

Jury: **M. Adel GHAZEL** – Maître de Conférences à SUPCOM (Président)

**M. Abderrazek JEMAI** – Maître-assistant à l'INSAT (Membre)

**M. Adel BENZINA** – Maître-assistant à l'EPT (Encadrant)

**M. Ahmed Amine JERRAYA** – Directeur de Recherche TIMA (Invité)

*A ma mère et mon père,

A mes deux sœurs,

A tous ceux qui me sont chers.*

## Remerciements

Au terme de ce travail, je tiens tout d'abord à remercier chaleureusement les membres du jury: Mr. Adel GHAZEL, Maître de conférences à SUPCOM, de m'avoir fait l'honneur de présider le jury de mon mémoire de mastère, Mr. Abderrazek JEMAI, Maître-assistant à l'INSAT, d'avoir participé au jury et Mr Adel BENZINA, Maître-assistant à l'Ecole Polytechnique de Tunisie, qui m'a encadré tout au long de ce mémoire.

Je voudrais adresser de même mes sincères remerciements à mes deux autres encadrants: Mr Ahmed Amine JERRAYA, directeur de recherche au CNRS et qui était responsable du groupe SLS du laboratoire TIMA, de m'avoir accueilli dans le groupe et d'avoir encadré ce travail de mastère et Mr Aimen BOUCHHIMA, Docteur en Post-Doc au laboratoire TIMA, de m'avoir guidé et orienté dans mon travail, je les remercie aussi pour leurs conseils pertinents.

J'exprime finalement ma gratitude à tous ceux qui m'ont aidé et soutenu durant ce stage de recherche; et j'exprime ma profonde reconnaissance à tous mes collègues et à tous les membres de l'équipe SLS pour leur active collaboration et pour leur sympathie.

## Résumé

Dans les systèmes embarqués, le logiciel prend une place de plus en plus importante, et sa complexité augmente d'autant. Ces systèmes étant très largement utilisés dans les applications récentes, il est important de pouvoir les développer rapidement.

L'accroissement de la complexité de ces systèmes fait de la maîtrise de leurs conceptions un défi à relever par les concepteurs.

En effet, la tendance à améliorer la productivité et réduire le temps de mise sur le marché (*time-to-market*), fait que le niveau transfert de registres (RTL) devient insatisfaisant pour la conception et le flot de vérification.

Pour dépasser ce défi, les nouvelles méthodes de conception sont basées sur des concepts d'abstraction de haut niveau. Une voie pour surmonter la complexité consiste donc à éléver le plus possible le niveau d'abstraction des descriptions des systèmes à concevoir, à savoir le niveau de modélisation transactionnel (TLM).

Dans ce travail, nous proposons d'étendre le niveau TLM – vu comme le haut niveau d'abstraction du niveau RTL – pour faciliter la conception et la validation du logiciel embarqué.

Nous visons à présenter les nouveaux concepts du TLM conçu pour le logiciel (***SW TLM***) permettant le raffinement de la communication logicielle.

La méthodologie proposée permet aux concepteurs de décider conjointement à propos de l'architecture logicielle ainsi que matérielle, afin d'assurer une performance maximale dans leurs conceptions. Ainsi, l'hétérogénéité des systèmes multiprocesseurs monopuces serait considérée plus efficacement de point de vue communication.

Le premier chapitre de ce document présentera brièvement notre travail.

Le deuxième chapitre abordera quelques généralités sur la conception des systèmes multiprocesseurs monopuces et présentera le flot de conception et de validation des systèmes hétérogènes monopuces proposé par le groupe SLS sur lequel nous avons travaillé.

Plus spécifiquement, le niveau auquel nous nous sommes intéressés est le niveau Architecture Virtuelle qui sera décrit dans le troisième chapitre. A ce stade, un nouveau flot de conception sera présenté parallèlement à la

description de la nouvelle méthodologie SW TLM. Son implémentation ainsi que ses différents concepts de base seront détaillés dans le chapitre d'après.

Le cinquième chapitre présentera la validation de ces concepts sur l'application MJPEG. Le dernier chapitre conclura et soulignera des perspectives de ce travail.

### ***Mots clés***

Systèmes multiprocesseurs monopuces, logiciel embarqué, flot de conception, niveaux d'abstraction, Architecture Virtuelle, niveau de modélisation transactionnel TLM, SW TLM.

## Abstract

Embedded software takes an important place in embedded systems and its complexity increases more and more. These systems are largely used in recent applications so it is important to be able to develop them quickly.

With the increasing complexity of embedded systems, mastering their designs is a challenge faced by the designers.

Indeed, the tendency to improve the productivity and to reduce the time to market makes Register Transfer Level (RTL) insufficient for the design and verification flow.

To deal with this challenge, the new design methods are based on high-level abstraction concepts. So, one way to overcome complexity consists at raising the abstraction level when designing embedded systems; the transactional level modeling TLM is emerging.

In this work, we propose to extend TLM approach – initially intended as a higher level abstraction of RTL hardware design – to cope with embedded software (SW) design and validation. We aim at introducing new SW TLM concepts which will enable refinement of communication at the SW side.

The proposed methodology allows system designers to decide about HW and SW communication architecture jointly, so as to ensure maximum performance efficiency for their designs. As such, multiprocessor systems on chip (MPSoC) heterogeneity would be addressed more efficiently from communication viewpoint.

The first chapter will briefly present our work. The second chapter will give a general overview of MPSoC design flow and will present the design and validation flow proposed by the SLS group. More specifically, we concentrate on Virtual Architecture level which will be described in the third chapter. At this stage, a typical design flow involving the VA level will be presented and the new SW TLM methodology will be described. Its implementation as well as its basic concepts will be detailed in the following chapter.

The fifth chapter will present the validation of these concepts on an MJPEG application. The final chapter will conclude and give prospects to this work.

***Key words***

MPSoC, embedded software design, design flow, abstraction levels, Virtual Architecture, Transaction Level Modeling, SW TLM.

# Table des matières

|                                                                                                  |           |

|--------------------------------------------------------------------------------------------------|-----------|

| <b>Chapitre 1</b>                                                                                |           |

| <b>Introduction</b>                                                                              | <b>11</b> |

| 1.1 Contexte: les systèmes multiprocesseurs monopuces .....                                      | 11        |

| 1.2 Problématique: la complexité et les difficultés de la conception<br>des systèmes MPSoC ..... | 13        |

| 1.3 Objectifs et solutions proposées par le groupe TIMA-SLS .....                                | 14        |

| 1.4 Contributions .....                                                                          | 17        |

| 1.5 Plan de ce document .....                                                                    | 17        |

| <b>Chapitre 2</b>                                                                                |           |

| <b>Conception des systèmes multiprocesseurs monopuces</b>                                        | <b>19</b> |

| 2.1 Introduction.....                                                                            | 19        |

| 2.2 Architectures logicielles/matérielles des systèmes multiprocesseurs<br>monopuces.....        | 19        |

| 2.2.1 Architectures matérielles.....                                                             | 20        |

| 2.2.2 Architectures logicielles.....                                                             | 21        |

| 2.2.2.1 La couche applicative .....                                                              | 21        |

| 2.2.2.2 La couche Système d'exploitation-Communication .....                                     | 21        |

| 2.2.2.3 La couche abstraction du matériel (HAL).....                                             | 21        |

| 2.3 Niveaux de modélisation .....                                                                | 24        |

| 2.3.1 Niveau RTL .....                                                                           | 25        |

| 2.3.2 Niveau TLM.....                                                                            | 25        |

| 2.4 Discontinuités du flot classique .....                                                       | 26        |

| 2.5 Nouveau flot de conception proposé dans le groupe TIMA-SLS                                   | 27        |

| 2.5.1 Présentation du flot de conception du groupe SLS.....                                      | 28        |

| 2.5.2 Description des niveaux intermédiaires du flot.....                                        | 28        |

| 2.6 Conclusion .....                                                                             | 30        |

| <b>Chapitre 3</b>                                                                                |           |

| <b>Niveau Architecture Virtuelle</b>                                                             | <b>31</b> |

| 3.1 Introduction.....                                                                            | 31        |

| 3.2 Définition du niveau Architecture Virtuelle.....                                             | 31        |

| 3.3 Vue d'ensemble d'un système au niveau V.A.....                                               | 35        |

| 3.4 Concepts de base du TLM pour le matériel.....                                                | 38        |

| 3.4.1 Méthodologie TLM.....                                                                      | 38        |

| 3.4.2 Les niveaux TLM PV et PVT .....                                                            | 40        |

| 3.5 Concepts de base du TLM pour le logiciel.....                                                | 42        |

| 3.5.1 Description des composants SW TLM.....                                                     | 42        |

| 3.5.2 Structure du SW TLM.....                                                                   | 43        |

| 3.6 Conclusion .....                                                                             | 44        |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>Chapitre 4</b>                                                  |           |

| <b>Implémentation (SW TLM)</b>                                     | <b>46</b> |

| 4.1    Introduction.....                                           | 46        |

| 4.2    Choix du langage.....                                       | 46        |

| 4.3    Implémentation du TLM pour le logiciel (SW TLM) .....       | 47        |

| 4.3.1    Hiérarchie du SW TLM .....                                | 47        |

| 4.3.2    Les interfaces de base.....                               | 49        |

| 4.4    Conclusion .....                                            | 54        |

| <b>Chapitre 5</b>                                                  |           |

| <b>Etude de cas: Application du SW TLM sur l'application MJPEG</b> | <b>55</b> |

| 5.1    Introduction.....                                           | 55        |

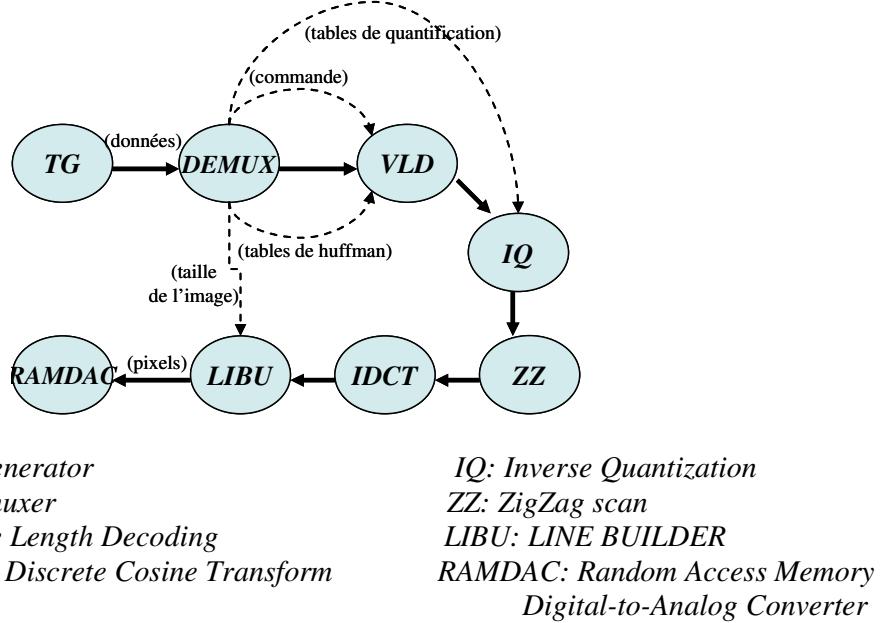

| 5.2    Description de l'application MJPEG .....                    | 55        |

| 5.2.1    L'application MJPEG .....                                 | 55        |

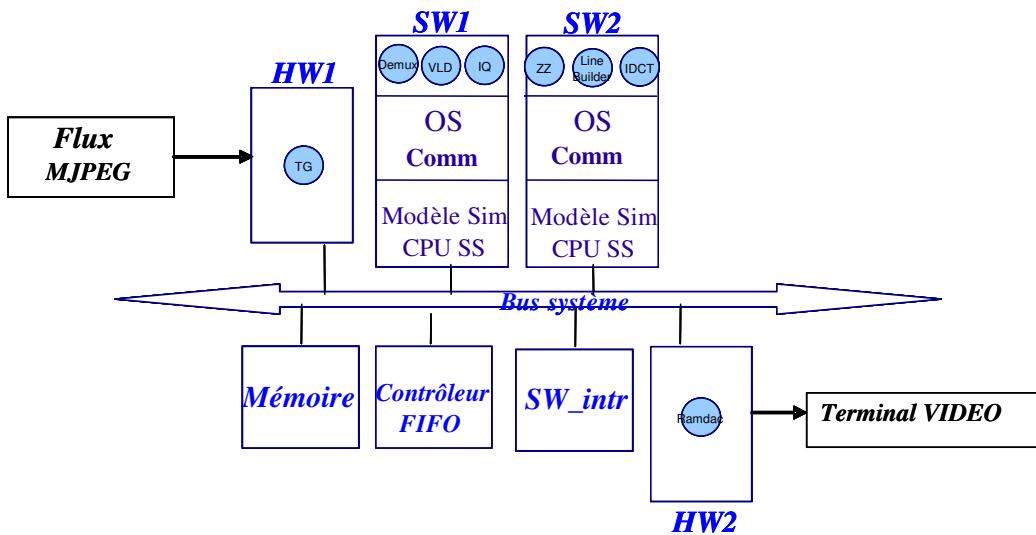

| 5.2.2    Partitionnement logiciel/matériel .....                   | 57        |

| 5.3    Architecture de l'application MJPEG au niveau V.A .....     | 57        |

| 5.4    Analyse expérimentale.....                                  | 61        |

| 5.5    Conclusion .....                                            | 64        |

| <b>Chapitre 6</b>                                                  |           |

| <b>Conclusion</b>                                                  | <b>65</b> |

| <b>Glossaire</b>                                                   | <b>67</b> |

| <b>Références</b>                                                  | <b>69</b> |

## Liste des figures

|     |                                                                                |    |

|-----|--------------------------------------------------------------------------------|----|

| 1.1 | Répartition du nombre et du type de processeurs dans les systèmes actuels..... | 12 |

| 1.2 | Niveaux de validation de l'interface logicielle/matérielle.....                | 15 |

| 1.3 | Flot de conception proposé par le groupe SLS.....                              | 16 |

| 2.1 | Architectures matérielles .....                                                | 20 |

| 2.2 | Architecture logicielle.....                                                   | 21 |

| 2.3 | Etapes et modèle d'un flot de conception classique .....                       | 26 |

| 2.4 | Flot de conception détaillé proposé par le groupe TIMA-SLS....                 | 28 |

| 3.1 | Modèle de simulation au niveau V. A.....                                       | 32 |

| 3.2 | Niveau Architecture Virtuelle .....                                            | 33 |

| 3.3 | Flot de conception typique comportant le niveau V.A.....                       | 34 |

| 3.4 | Modèle conceptuel de l'Architecture Virtuelle .....                            | 36 |

| 3.5 | Architecture TLM .....                                                         | 40 |

| 3.6 | Les couches TLM .....                                                          | 40 |

| 3.7 | Les composants SW TLM .....                                                    | 42 |

| 3.8 | Architecture en couches de la communication logicielle .....                   | 44 |

| 4.1 | Les couches du SW TLM .....                                                    | 48 |

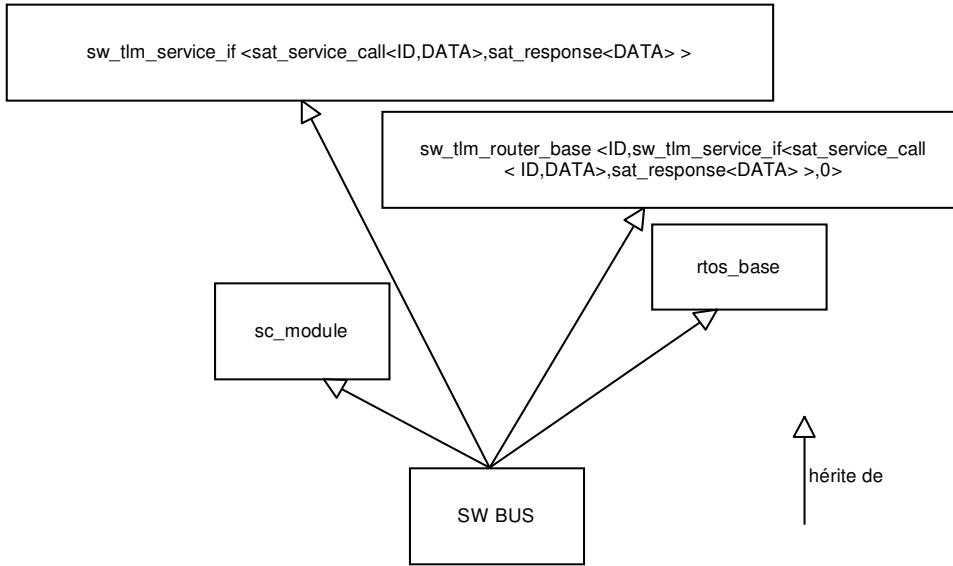

| 4.2 | Hiérarchie de classe du bus logiciel .....                                     | 53 |

| 5.1 | Graphe de tâches de l'application MJPEG .....                                  | 56 |

| 5.2 | Partitionnement logiciel/matériel de l'application MJPEG.....                  | 57 |

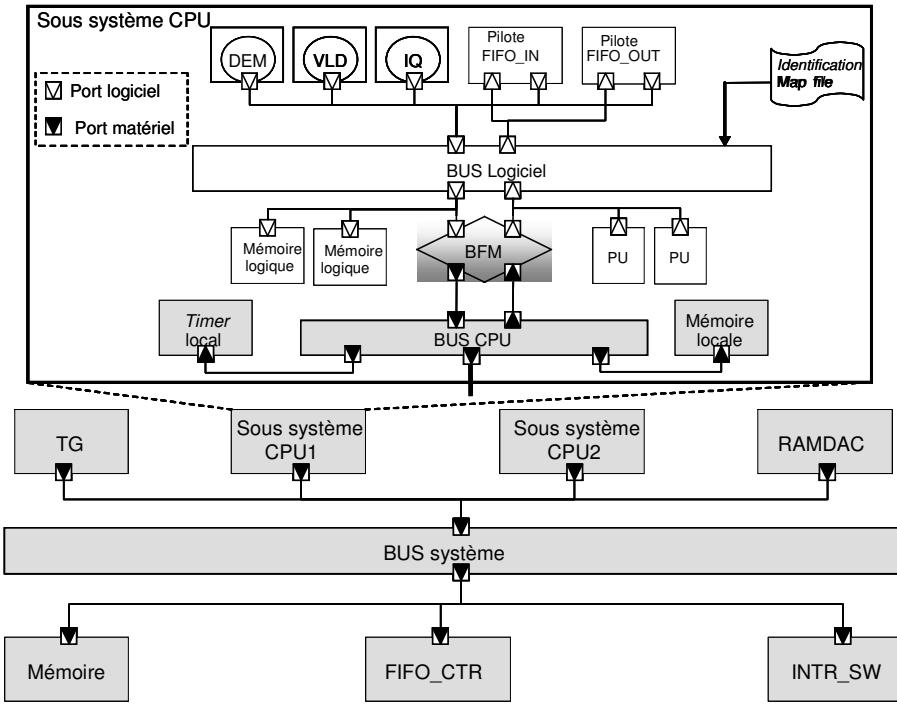

| 5.3 | Modèle MJPEG au niveau Architecture Virtuelle.....                             | 59 |

## Liste des tableaux

|     |                                                                                   |    |

|-----|-----------------------------------------------------------------------------------|----|

| 5.1 | Résultats comparatifs de la simulation aux différents niveaux d'abstraction ..... | 62 |

|-----|-----------------------------------------------------------------------------------|----|

# Chapitre 1

## Introduction

Ce chapitre a pour but de situer le travail de ce mémoire. Pour ce faire, il définit dans une première section les systèmes multiprocesseurs monopuces. Dans la deuxième section, la problématique est exposée. Dans la troisième section, sont présentés les objectifs à atteindre ainsi que les solutions apportées par le groupe SLS pour faire face à ces problèmes.

Notre contribution apportée par ce mémoire sera détaillée dans la section suivante. Enfin, le plan du document sera détaillé.

### 1.1 Contexte: les systèmes multiprocesseurs monopuces

Ce travail s'inscrit dans le domaine de la conception des systèmes embarqués multiprocesseurs monopuces, plus communément appelés *MPSoC*<sup>1</sup>.

Les progrès technologiques constants en terme d'intégration sur silicium ont permis de concevoir des systèmes sur puces de plus en plus complexes afin de répondre à une demande forte du marché pour des applications telles que les systèmes multimédia, la téléphonie mobile ou encore les applications de jeux vidéo. On a ainsi vu naître une nouvelle catégorie de systèmes ces dernières années, incluant un ou plusieurs processeurs, des composants dédiés et des modules d'entrée-sortie, le tout sur une seule puce. Ces systèmes sont appelés *Systèmes sur Puce*, ou *System-on-a-Chip (SoC)* en anglais. Une grande partie de ces systèmes consistent en l'intégration sur une même puce de plusieurs processeurs, DSP, IP matériel, mémoires, bus partagés, etc. On parle alors de systèmes multiprocesseurs monopuces (*MPSoC*). Ces systèmes sont réalisés en interconnectant des noeuds de calcul avec un réseau de communication.

Pour faire face à la complexité de tels systèmes, des méthodes de conception permettant le découplage de la communication et du calcul ont été proposées [14] [27]. La communication prend d'ailleurs une place de plus en plus importante dans la conception de tels systèmes [16].

La conception des systèmes sur puce doit faire face à de nombreuses contraintes de performance, de consommation et de coût, pour lesquelles

---

<sup>1</sup> *Multi Processor System on Chip*

actuellement, seules des plateformes spécifiques<sup>2</sup> à chaque application peuvent répondre [1].

De plus, l'augmentation des performances par la fréquence ou par les techniques « classiques » (pipeline, prédition de branchement,...) ne sont plus significatives en terme de performance et induisent une consommation inacceptable [24]. Une solution pour répondre aux problèmes de performance et de consommation consiste à augmenter le parallélisme dans les systèmes par l'intégration de plusieurs processeurs de type hétérogènes<sup>3</sup> afin de cibler au mieux les applications.

En 2001, les systèmes de prévisions stratégiques du rapport ITRS [12] prévoient que 70% des ASIC (*Application Specific Integrated Circuit*) comporteraient au moins un processeur embarqué à partir de l'année 2005. Aujourd'hui, les SoC peuvent intégrer de nombreux processeurs et cette tendance est confirmée par le rapport ITRS 2005 [13].

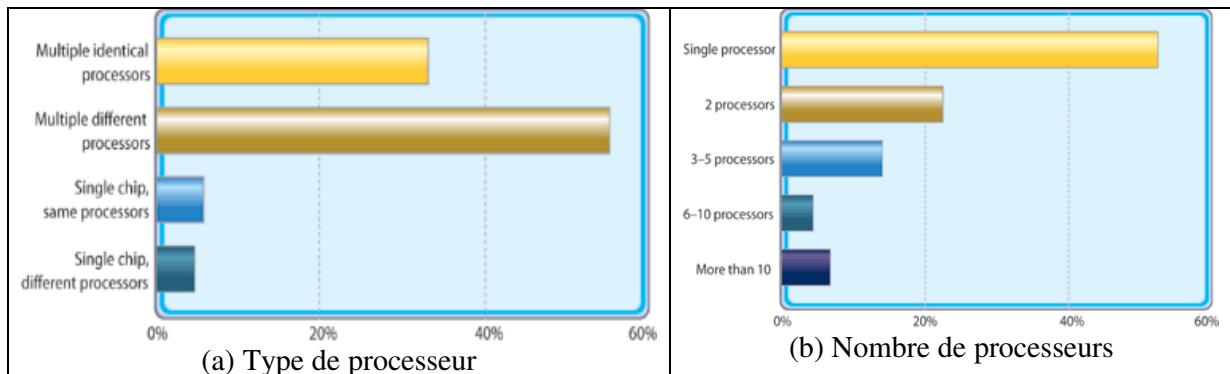

Les figures 1.1(a) et 1.1(b) tirées de [15] montrent que près d'un système sur deux est un système multiprocesseur et que pour une partie importante d'entre eux il s'agit de processeurs hétérogènes.

Figure 1.1 - Répartition du nombre et du type de processeurs dans les systèmes actuels

Il est prévu que ces systèmes monopuces soient les principaux vecteurs d'orientation de toute l'industrie des semi-conducteurs. Il est donc crucial de maîtriser la conception de tels systèmes tout en respectant les contraintes de mise sur le marché et les objectifs de qualité.

Le grand défi en ce moment pour les ingénieurs est de réussir à maîtriser la complexité lors de la conception de ces systèmes et d'arriver à une conception

<sup>2</sup> Par rapport aux plateformes à usage général

<sup>3</sup> Processeurs à usage général, processeurs de traitement de signal, ...

rapide des systèmes monopuces sous de fortes contraintes de qualité et de temps de développement.

Pour dépasser ce défi, les nouvelles méthodes de conception sont basées sur des concepts d'abstraction de haut niveau.

## 1.2 Problématique: la complexité et les difficultés de la conception des systèmes MPSoC

Habituellement, les flots de conception des systèmes embarqués utilisent principalement le modèle RTL (*Register Transfer Level*) pour modéliser le système au niveau des transferts de registres.

Ainsi, à ce niveau d'abstraction, nous devons modéliser tous les signaux passant entre les différentes entités de simulation. Ce niveau est temporisé au cycle d'horloge près. C'est pourquoi les simulations matérielles effectuées au niveau RTL sont relativement longues, ce qui peut allonger le temps de conception du système.

En plus, un modèle global d'une architecture classique logicielle/matérielle est conventionnellement décrit au niveau RTL/ISA<sup>4</sup>. A ce niveau, le logiciel n'est autre qu'une suite d'instructions binaires placée dans une zone mémoire. Le matériel est décrit en utilisant un langage de description de matériel (*HDL*<sup>5</sup>). Ceci inclut l'architecture locale du noeud logiciel (processeur, mémoire, périphériques, etc.) mais aussi les autres parties du système. A ce niveau le processeur est considéré comme l'interface ultime entre le logiciel et le matériel. Il fournit d'un côté au programmeur une vision au niveau ISA de la machine. De l'autre côté, il interagit avec le reste des composants de l'architecture matérielle via des signaux physiques (bus d'adresses, bus de données, signaux de contrôle, signaux d'interruptions, etc.) Cette vision de l'architecture n'est donc valable qu'une fois les deux parties logicielle et matérielle entièrement conçues, c'est-à-dire vers la fin du cycle de conception.

Vu le niveau d'abstraction employé, la vitesse de simulation reste très réduite et constitue ainsi une barrière empêchant l'exploration et la validation des applications les plus exigeantes.

De même, nous notons l'absence de méthodologie et d'outils permettant une transition non brutale de la spécification initiale à l'architecture finale.

---

<sup>4</sup> Instruction Set Architecture

<sup>5</sup> Hardware Description language

Pour faire face à ces défis, la modélisation au niveau transactionnel (TLM) a été récemment favorisée pour la conception matérielle parallèlement à une proposition de nouveau flot de conception graduel.

En effet, une solution suggérée est l'augmentation du niveau d'abstraction des modèles pour améliorer la productivité.

Bien que l'ultime objectif du TLM est de permettre le développement tôt du logiciel embarqué ainsi que de paralléliser le développement du matériel et du logiciel dans le cycle de conception des systèmes sur puce, aucune modélisation TLM n'a été définie pour le logiciel.

Dans les applications TLM classiques, le logiciel est considéré au niveau fonctionnel ou bien complètement raffiné et simulé à un très bas niveau d'abstraction sur un simulateur de jeux d'instructions (*ISS: Instruction Set Simulator*) concurremment avec des simulations matérielles, au niveau transaction ou au niveau cycle.

De même, l'évaluation des sous systèmes logiciels embarqués, tôt dans les étapes de conception n'est plus faisable en employant les approches traditionnelles de simulation, précises au niveau cycle. Le problème vient de la vitesse lente de simulation de l'ISS.

Pour une simulation plus rapide, nous avons pensé à un niveau transactionnel pour le logiciel similaire à celui pour le matériel, ceci sera considéré à un haut niveau d'abstraction. D'où les composants aussi bien logiciels que matériels seront modélisés avec un modèle unique afin d'aborder la conception du système dans une seule et même approche cohérente.

### 1.3 Objectifs et solutions proposées par le groupe TIMA-SLS

Le groupe SLS s'est focalisé sur la conception conjointe du logiciel et du matériel afin de résoudre les problèmes soulevés dans les paragraphes précédents. Cette conception se base sur un raffinement graduel à différents niveaux d'abstraction.

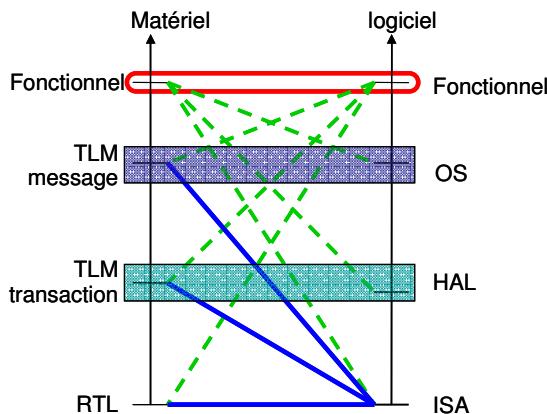

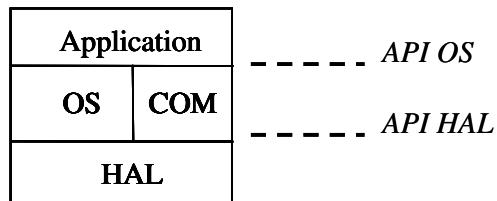

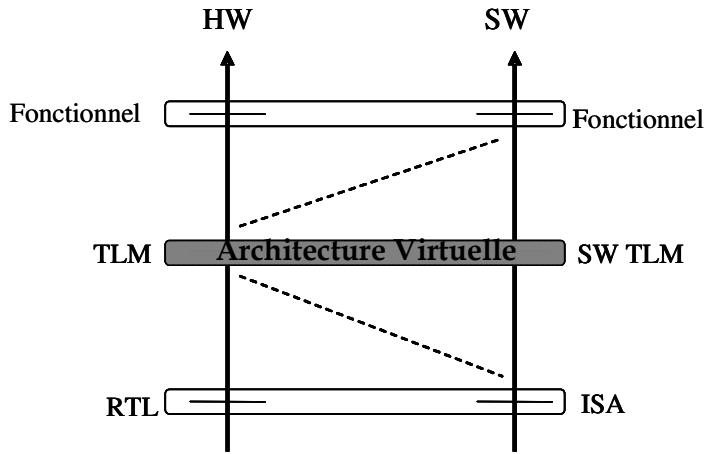

La Figure 1.2 montre les deux niveaux intermédiaires proposés dans le flot de conception des SoC à savoir *Virtual Architecture* (niveau OS du côté logiciel) et *Transaction Accurate* (niveau HAL du côté logiciel).

Les traits continus forts correspondent au cas classiques de co-simulation<sup>6</sup> logicielle/matérielle tels que proposés par les approches conventionnelles. Remarquons que ces approches se basent exclusivement sur le niveau ISA du côté du logiciel. L'utilisation des niveaux TLM pour le matériel est assez récente. Historiquement c'est le niveau RTL qui était utilisé comme niveau de référence pour la co-simulation logicielle/matérielle à côté du niveau ISA.

Figure 1.2 – Niveaux de validation de l’interface logicielle/matérielle

L'utilisation d'un modèle à base d'ISS pour la co-simulation logicielle/matérielle présente toujours l'inconvénient d'intervenir tard dans le cycle de conception, c'est à dire une fois l'architecture logicielle et matérielle du système est fixée et complètement développée. Le besoin croissant de pouvoir effectuer la validation et l'exploration des choix architecturaux plus tôt dans le cycle de conception, a récemment poussé vers la mise au point d'approches qualifiées de « systèmes » -ou encore de « haut niveau »- permettant la co-simulation d'un système logiciel/matériel tôt dans le cycle de conception.

Donc, pour remédier à la discontinuité observée dans les flots classiques de conception et de validation des systèmes MPSoC, le groupe SLS a introduit les concepts de *Virtual Architecture* et de *Transaction Accurate* comme étant des étapes intermédiaires dans le flot de conception permettant la validation, par co-simulation globale, des choix architecturaux résultant du raffinement graduel du système.

Pour bénéficier de l'avantage d'une simulation rapide à ces niveaux intermédiaires, nous utilisons l'exécution native comme mode d'exécution du logiciel embarqué.

<sup>6</sup> Simuler conjointement les diverses parties d'un système hétérogène

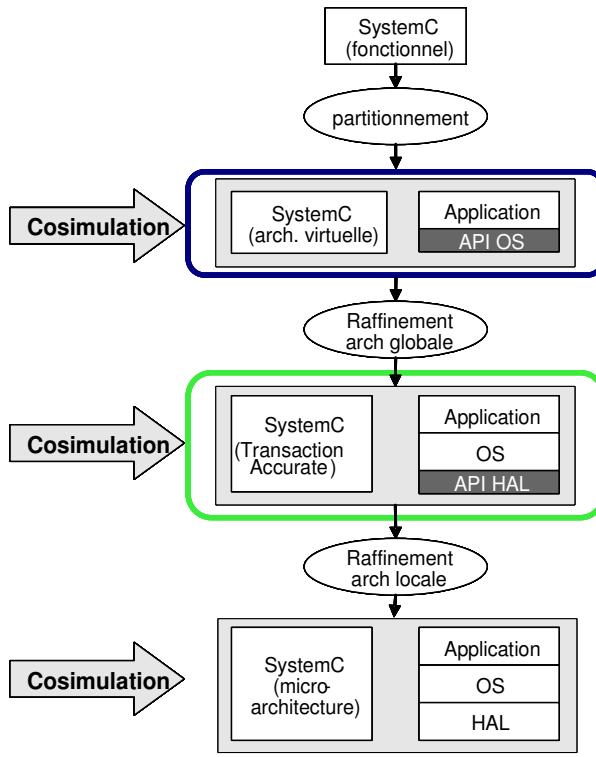

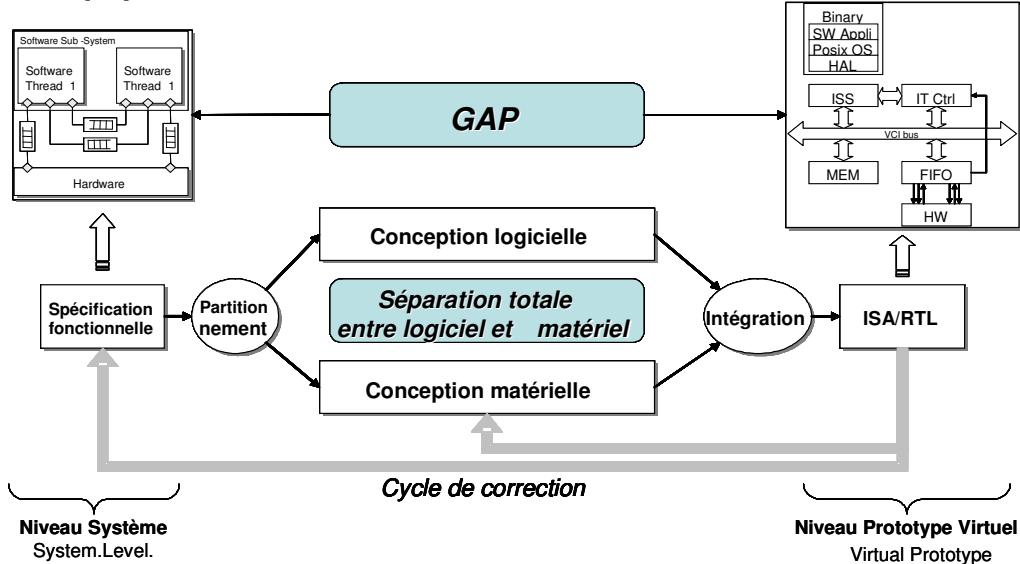

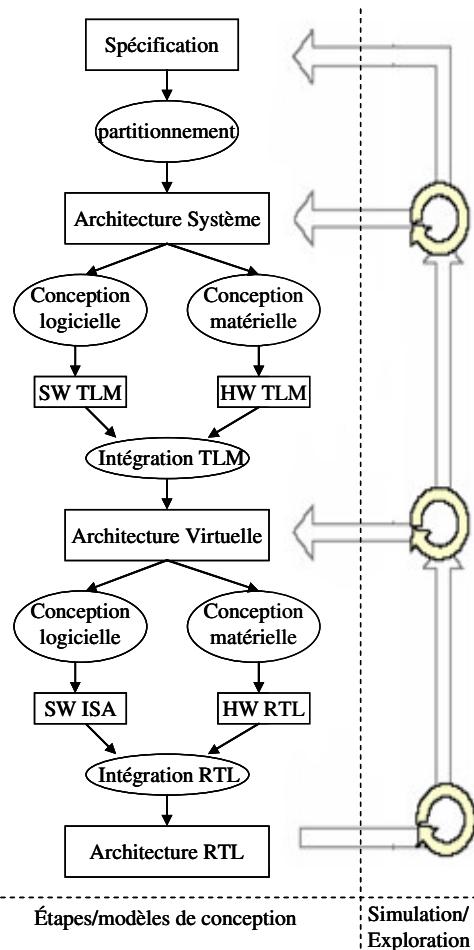

La Figure 1.3 donne une vision simplifiée du flot de conception proposé par le groupe SLS :

Figure 1.3 – Flot de conception proposé par le groupe SLS

Ce flot débute au niveau fonctionnel après que le partitionnement logiciel/matériel ait été décidé. Il se termine au niveau micro-architecture (RTL), où une étape classique de compilation et de synthèse logique permet d'aboutir à la réalisation finale du système. C'est un flot descendant qui permet de simuler à tous les niveaux et éventuellement de revenir en arrière à chaque étape.

Dans ce flot, l'architecture virtuelle résulte d'une première étape de partitionnement de la spécification fonctionnelle initiale. Le partitionnement sépare les parties qui seront implémentées de façon matérielle de celles qui seront implémentées de façon logicielle.

La deuxième étape du flot correspond au raffinement de l'architecture virtuelle en utilisant un modèle plus détaillé de l'architecture: *Transaction Accurate*. Cette étape est caractérisée par la spécification de la nature du protocole de communication entre les sous-systèmes ainsi que du modèle abstrait de l'architecture locale au niveau de chaque sous-système.

Le groupe SLS s'est intéressé aussi à la génération automatique des interfaces logicielles/matérielles.

## 1.4 Contributions

Durant ce travail, nous avons contribué à la définition des niveaux de conception intermédiaires notamment *Virtual Architecture* et *Transaction Accurate* proposés par le groupe TIMA-SLS.

Plus précisément, nos travaux au niveau T.A [20] consistaient à prouver l'intérêt et la faisabilité d'une estimation de performance des systèmes en utilisant ce modèle haut niveau de l'architecture logicielle/matérielle.

Nous avons aussi essayé d'adapter le niveau T.A au niveau TLM de ST-Microelectronics.

Nos travaux au niveau V.A qui est un niveau plus abstrait que T.A consistent à valider l'application logicielle sur un modèle de simulation du système d'exploitation et de l'architecture. En effet, nous avons proposé un modèle d'extension pour le niveau V.A.

Nous voulons pour cela étendre le niveau TLM pour supporter non seulement la partie matérielle mais également la conception et la validation du logiciel embarqué.

La contribution attendue est de proposer alors une méthode permettant d'unifier la présentation du logiciel embarqué. Fort de ce contexte uniifié de modélisation, la conception du logiciel embarqué et de l'architecture sous jacente pourra alors se dérouler en parallèle et d'une manière interactive.

Nous proposons par la suite un modèle transactionnel pour le logiciel embarqué au niveau V.A basé sur TLM OSCI<sup>7</sup>. Les propriétés de ce modèle permettent d'unifier la représentation des composants logiciels et matériels.

L'objectif général à terme étant de développer un environnement complet de simulation d'architectures MPSoC au niveau TLM, basé sur SystemC.

## 1.5 Plan de ce document

Ce document est organisé en six chapitres dont cette introduction.

---

<sup>7</sup> Open SystemC Initiative

Le second chapitre est dédié à la conception des systèmes MPSoC et pause de manière plus précise la problématique et les objectifs de ce travail.

Le chapitre trois définit le niveau d'abstraction intermédiaire: Architecture Virtuelle et présente alors un flot de conception typique introduisant ce niveau. A ce stade, nous expliquons le raffinement de la communication logicielle et nous définissons la terminologie TLM pour le logiciel « **SW TLM** ».

Le chapitre quatre détaille différents aspects nécessaires pour l'implémentation du SW TLM.

Une application de l'approche est ensuite présentée dans le chapitre cinq. Finalement, le dernier chapitre conclut ce document et propose quelques perspectives potentielles à ce travail.

## Chapitre 2

# Conception des systèmes multiprocesseurs monopuces

### 2.1 Introduction

Ce chapitre a pour objet de donner un aperçu de la problématique de la conception des systèmes MPSoC en examinant les flots de conception classiques. Il introduit ensuite le flot de conception proposé par le groupe TIMA SLS.

La première section décrit les architectures logicielles et matérielles des systèmes multiprocesseurs monopuces. Puis, la section suivante introduit les niveaux de modélisation notamment RTL et TLM.

### 2.2 Architectures logicielles/matérielles des systèmes multiprocesseurs monopuces

Avant de détailler la conception des systèmes multiprocesseurs monopuces, il est nécessaire de dresser un bref aperçu des architectures multiprocesseurs.

En effet, il existe principalement deux types d'organisations pour les architectures des systèmes Multiprocesseurs [8]:

- Mémoire partagée: Dans ce type d'organisation, l'architecture matérielle est en général composée de plusieurs processeurs identiques. L'application *Multithread* repose sur une seule pile logicielle. La communication entre les différents processeurs s'effectue par une mémoire partagée globale.

- Passage de messages: Cette organisation repose sur plusieurs piles logicielles s'exécutant sur des sous systèmes hétérogènes, aussi bien en terme de processeurs, qu'en terme d'entrées/sorties. La communication entre les sous-systèmes est réalisée par passage de messages.

Afin d'intégrer un plus grand nombre de processeurs, les architectures MPSoC hétérogènes combinent généralement ces deux modèles [22]. Les futurs MPSoC hétérogènes seront composés de plusieurs sous-systèmes également hétérogènes, chacun pouvant contenir un nombre important de processeurs identiques exécutant une seule pile logicielle [2].

### 2.2.1 Architectures matérielles

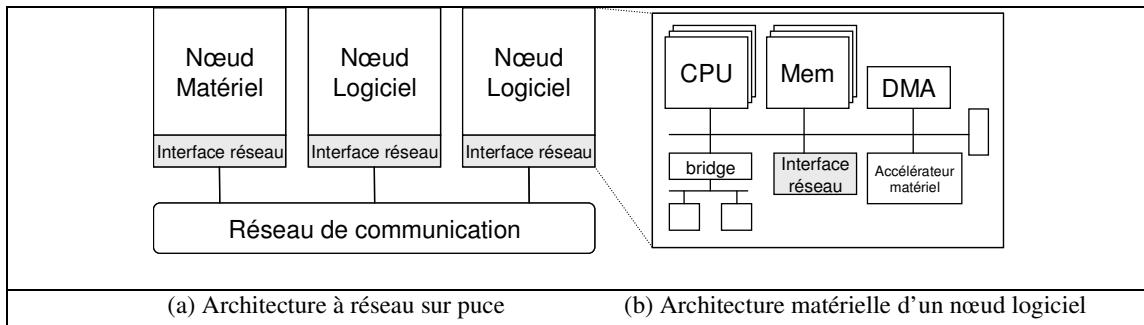

L'architecture matérielle des systèmes multiprocesseurs monopuces peut être représentée d'une manière générale par un ensemble d'unités d'exécution pouvant être logicielles ou matérielles connectées sur un réseau de communication (Figure 2.1(a)). On parlera de nœud logiciel ou de nœud matériel.

L'architecture matérielle des systèmes MPSoC peut être décomposée en quatre blocs de base: (1) processeur ou sous-système processeur pour exécuter le logiciel, (2) modules mémoires ou unités de stockage de données, (3) sous-système de calcul composé de matériel spécifique et (4) un réseau d'interconnexion. Il y a eu un développement et une sophistication continu de chacun de ces blocs de base, mais c'est surtout leur arrangement qui différencie un système MPSoC d'un autre.

Un problème important auquel font face ces architectures concerne la communication qui désormais constitue un goulet d'étranglement vu la quantité importante d'informations qui doit être échangée entre les différents composants de l'architecture.

La communication peut être assurée par des réseaux de communication complexes (bus hiérarchiques, bus avec protocole TDMA, connexion point à point, structure en anneau et même des réseaux de communication par paquets). On trouve aussi les réseaux de communication sur puce (NoC de l'anglais Network on Chip) qui constituent une alternative radicale aux bus partagés.

L'architecture matérielle d'un nœud logiciel (Figure 2.1 (b)), appelée sous-système processeur, est composée d'un ou plusieurs processeurs identiques ainsi que des composants périphériques nécessaires pour leur interfaçage ou pour l'accélération de performance.

Figure 2.1 - Architectures matérielles

### 2.2.2 Architectures logicielles

Parallèlement à l'évolution des architectures matérielles des systèmes monopuces, le logiciel embarqué est passé du simple programme séquentiel, souvent développé en langage assembleur, à un système concurrent implémentant un comportement complexe et bénéficiant d'une architecture à part entière.

Comme dans la plupart des architectures logicielles actuelles, la pile logicielle utilisée est organisée en couches pour des raisons de standardisation et de réutilisation.

Figure 2.2 – Architecture logicielle

Chaque couche fournit à la couche supérieure une interface de programmation propre (API<sup>8</sup>).

#### 2.2.2.1 La couche applicative

La couche applicative constitue la partie fonctionnelle du logiciel embarqué. En effet, le programme applicatif se compose d'un ensemble de tâches communicantes, réalisant le comportement de l'application tel que décrit dans la spécification fonctionnelle.

Cette couche est utilisée par le concepteur du logiciel pour représenter son application sans se préoccuper de l'architecture matérielle.

Généralement *Multithread*, elle est implantée sur une API de modèle de programmation parallèle, permettant d'abstraire les détails de l'architecture logicielle et matérielle sous-jacentes. Cette séparation est nécessaire pour le développement du logiciel et du matériel de manière concurrente.

La couche API représente les appels système de haut niveau invoqués par les tâches logicielles. Ainsi, à ce niveau de description, n'existent que des informations liées aux traitements à réaliser.

---

<sup>8</sup> Application Programming Interface

### 2.2.2.2 La couche Système d'exploitation - Communication

Cette couche permet de gérer localement les ressources disponibles. Ceci inclut par exemple la gestion des tâches, la communication inter tâches et la communication externe, l'ordonnancement (*Scheduling*), etc.

Dans les systèmes embarqués, le système d'exploitation (SE ou *OS*<sup>9</sup>) est vu comme l'entité logicielle qui permet l'accès au matériel en coopération avec le logiciel applicatif. Son rôle principal est de multiplexer l'accès à des ressources limitées en fournissant une abstraction adéquate de ces ressources, tout en garantissant une certaine qualité de service.

L'usage de systèmes d'exploitation est devenu nécessaire dans les systèmes embarqués, du fait de la complexité croissante de ces systèmes, de la présence de fortes contraintes temps réel, de la limitation des ressources disponibles, tant en mémoire qu'en énergie disponible et donc en puissance de calcul, mais également de la pression exercée par le marché sur ces produits. En effet, le temps de développement doit être raisonnable, afin de limiter le temps de mise sur le marché, et ainsi d'assurer le succès du produit. Parmi les exemples des systèmes d'exploitation embarqués nous citons: QNX, eCos, RTLinux, VxWorks, etc.

Brièvement, les fonctions de base d'un système d'exploitation sont:

- gestion de tâches et ordonnancement;

- services d'interruption;

- communication inter tâches et synchronisation;

- gestion de mémoire.

Dans notre travail, nous utilisons un modèle de simulation d'OS fait par l'équipe TIMA-SLS.

Ce modèle se compose de :

**API OS:** regroupe tous les services représentant l'API du système d'exploitation utilisable par l'application logicielle. Cette famille contient trois sous familles:

- IO (*Input/Output*): regroupe tous les services liés aux communications utilisables par l'application logicielle (par exemple le tube (*pipe*));

- Synchronisation: regroupe tous les services liés aux synchronisations utilisables par l'application logicielle (par exemple les sémaphores);

- Autres services de haut niveau.

---

<sup>9</sup> *Operating System*

**Noyau (*Kernel*)**: regroupe tous les services concernant le noyau du système d'exploitation. Il contient les sous familles suivantes:

- L'amorce (*Boot*): regroupe tous les services liés au démarrage du système d'exploitation. Cette sous-famille initialise les registres des processeurs, la table des vecteurs d'interruptions, les espaces de piles, l'espace d'adressage, etc. Elle charge le noyau en mémoire;

- Changement de contexte (*Cxt*): regroupe tous les services liés à la gestion des contextes associés aux tâches. Les éléments fournissant ces services sont toujours spécifiques au processeur cible;

- Ordonnanceur (*Scheduler*): regroupe tous les services liés à l'ordonnancement des tâches. Pour cela il utilise un algorithme de gestion, généralement par priorité ou tourniquet<sup>10</sup>, et gère l'ordre d'exécution des tâches (par exemple la mise en sommeil ou le réveil d'une tâche);

- Tâche (*Task*): regroupe tous les services liés à la gestion des tâches. En pratique, cette famille de services fait le lien entre les autres sous-familles de la famille Noyau (*Kernel*). Elle décrit la structure de la tâche et contient les tables de tâches.

**Synchronisation**: regroupe tous les services liés aux mécanismes de synchronisation internes au système d'exploitation. Le partage des ressources sur différentes entités concurrentes (par exemple tâches de l'application) impose une politique de protection qui permet d'assurer la cohérence de l'information contenue dans ces ressources.

Parmi les primitives de synchronisation nous notons : *Wait* pour attendre un signal par exemple et *Notify* pour en générer un, *Block* met la tâche courante dans l'état endormi et la place dans une file d'attente, *Unblock* réveille une des tâches endormies dans une file d'attente, etc.

Pour fonctionner, cet élément a besoin des services du Noyau.

**Interrupt**: regroupe tous les services liés aux interruptions (par exemple la gestion des fonctions d'interruption, ou des appels système). Ces services ont besoin des primitives de synchronisation.

---

<sup>10</sup> Chaque processus dispose d'un quantum de temps pendant lequel il peut s'exécuter, puis c'est au tour du suivant, en anglais *Round Robin*.

Dans cette même couche nous trouvons la partie COM qui gère principalement la communication de l'application avec le matériel. Ceci est assuré par les pilotes de périphériques.

Un pilote de périphérique fournit un accès aux E/S et sert à les gérer.

#### 2.2.2.3 La couche abstraction du matériel (HAL)

Classiquement, le logiciel embarqué est développé à un niveau d'abstraction très bas en utilisant souvent le langage assembleur. Pour ce faire, les programmeurs sont supposés avoir une connaissance très poussée de l'architecture matérielle sous-jacente dans ses moindres détails. D'un point de vue du logiciel, cette dépendance étroite vis-à-vis de l'architecture matérielle présente plusieurs inconvénients: tout d'abord, ceci implique un long cycle séquentiel de conception, puisque les programmeurs sont obligés d'attendre qu'une architecture matérielle complète soit disponible.

Cette situation s'aggrave encore plus si des modifications à l'architecture initiale s'avèrent nécessaires, entraînant la re-conception d'une majeure partie du logiciel. Ensuite, ceci rend le processus de validation et de débogage du logiciel fastidieux et induit des erreurs à cause de dépendances matérielles subtiles. Enfin, à cause de ces mêmes dépendances, la réutilisation de composants logiciels préconçus se trouve considérablement limitée.

La notion de couche d'abstraction du matériel (*HAL*<sup>11</sup>) est introduite pour palier les inconvénients d'une telle dépendance bas niveau de l'architecture matérielle [3].

Cette couche permet l'accès structuré aux ressources; et aussi de cacher les détails bas niveau de l'architecture matérielle. En effet, la couche HAL est une couche logicielle fine qui est supposée fournir une abstraction de l'accès aux ressources matérielles de l'architecture.

### 2.3 Niveaux de modélisation

L'étude des niveaux d'abstraction de la communication dans les langages de description du matériel n'est pas nouvelle. Dans cette section, nous nous intéressons aux deux niveaux RTL et TLM.

---

<sup>11</sup> *Hardware Abstraction Layer*

### 2.3.1 Niveau RTL

Le niveau RTL est probablement le niveau d'abstraction le plus utilisé pour la modélisation des systèmes matériels [23].

Le niveau RTL est clairement identifié. A ce niveau de conception, la communication interne et externe des composants matériels est réalisée par des fils et des bus physiques. Les données intervenant dans une communication sont sous une forme logique, c'est-à-dire qu'elles sont présentées par des vecteurs de bits.

Dans une communication au niveau RTL, le temps est une grandeur réelle, arbitraire et discrète. La granularité de l'unité de temps est le cycle d'horloge et les primitives de communication sont des lectures et écritures sur des ports et l'attente d'un nouveau cycle d'horloge. Ce niveau d'abstraction est supporté dans la majorité des langages HDL<sup>12</sup> en particulier dans VHDL, Verilog et SystemC.

Cependant, ce niveau est de plus en plus considéré comme trop détaillé en approche système. D'une part, il nécessite un travail important pour le décrire complètement, d'autre part son utilisation pour des vérifications par simulation conduit à des temps excessifs.

L'introduction d'un niveau plus abstrait que RTL s'avère nécessaire: il s'agit du niveau TLM.

### 2.3.2 Niveau TLM

Les modèles transactionnels ont été introduits pour augmenter la productivité des concepteurs de systèmes sur puce. Il s'agit d'un nouveau niveau d'abstraction, plus haut que le niveau RTL qui constitue le point d'entrée des outils de synthèse.

TLM (*Transaction Level Model*) est progressivement adopté par les industriels pour modéliser rapidement et simuler à grande vitesse les architectures de systèmes sur puce (SoC), dans le but notamment de permettre le développement du logiciel embarqué avant de disposer de la description synthétisable complète du matériel, et de procéder à des analyses d'architectures très tôt dans le cycle de conception, ce qui n'était pas possible au niveau RTL, du fait de la lenteur des simulations et de la complexité des modèles manipulés.

---

<sup>12</sup> *Hardware Description Language*

TLM utilise une approche à base de composants, dans laquelle les blocs matériels sont des modules communicants par le biais des transactions, ou les détails inutiles de communication sont omis. Par suite, il permet d'accélérer la simulation et explorer les alternatives d'implémentation tôt dans le cycle de conception (tel que la topologie du bus, les priorités du bus, l'optimisation de la taille de la mémoire, etc.) [17].

TLM sera plus détaillé dans le chapitre trois.

## 2.4 Discontinuités du flot classique

La Figure 2.3 représente un flot de conception classique pour les systèmes embarqués monopuces.

Un tel flot est caractérisé par une séparation franche et prématurée entre la conception de la partie matérielle et de la partie logicielle.

Ce flot débute par une spécification fonctionnelle de l'application dans des langages haut niveaux, généralement exécutables, tels que SystemC [26] ou Simulink [21].

Figure 2.3 – Etapes et modèle d'un flot de conception classique

La seconde étape consiste à répartir les différentes tâches entre le matériel et le logiciel séparant ainsi la conception du système en deux parties complètement autonomes: une dédiée à l'architecture matérielle et l'autre au logiciel embarqué qui va s'exécuter sur cette architecture. L'intégration permettra finalement de regrouper à nouveau les deux parties afin d'obtenir un modèle bas niveau où le matériel est décrit en RTL et le logiciel au niveau instruction binaire.

Dans un tel flot il peut être difficile de développer complètement le logiciel sans que le matériel soit défini. C'est pour cela que son développement devait souvent attendre que la partie matérielle soit décrite pour être achevé.

## 2.5 Nouveau flot de conception proposé dans le groupe TIMA-SLS

L'approche de conception vue précédemment est caractérisée par une discontinuité qui marque le passage de la spécification initiale à l'implémentation finale. Elle constitue comme nous l'avons souligné un handicap dans ce flot classique. Cette discontinuité verticale se traduit également par une autre discontinuité horizontale qui tend à séparer la description du système en deux parties complètement indépendantes, une logicielle et l'autre matérielle qui sont alors conçues et raffinées individuellement d'une manière séparée.

Pour résoudre ce problème, il est clair qu'il faut introduire, dans le flot de raffinement de l'architecture, des étapes supplémentaires permettant l'interaction entre logiciel et matériel.

### 2.5.1 Présentation du flot de conception du groupe SLS

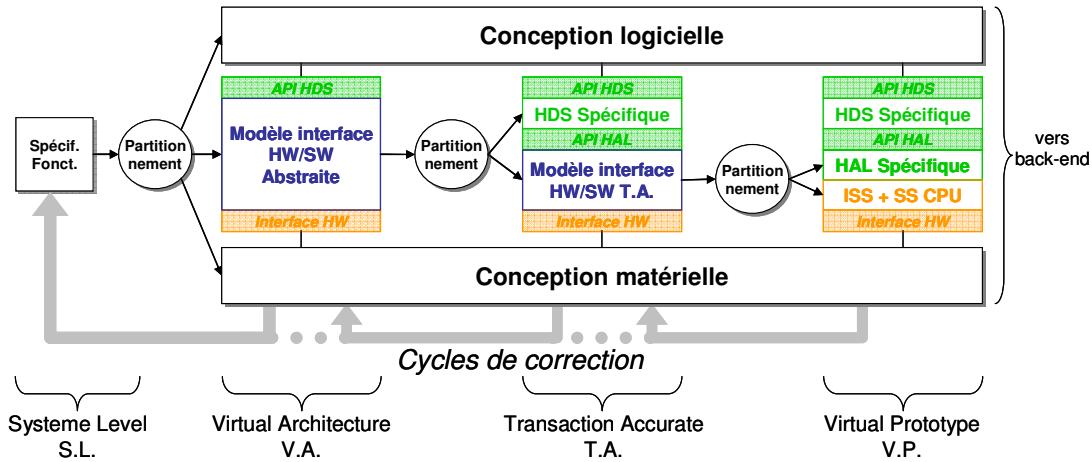

La Figure 2.4 présente la solution apportée par le groupe SLS pour palier aux discontinuités des flots de conception classiques.

Le principe de base de cette approche est de considérer la conception de l'interface logicielle/matérielle comme étant une branche complète du flot. Cette *externalisation* apporte une solution à la discontinuité entre les niveaux d'abstraction sous réserve de la disponibilité de modèles exécutables de l'interface, permettant ainsi de simuler le système complet durant toutes les étapes de la conception conjointe.

La discontinuité dans la conception conjointe du logiciel et du matériel est naturellement solutionnée par cette approche où la conception de l'interface logicielle/matérielle est traitée dans sa globalité.

Figure 2.4 - Flot de conception détaillé proposé par le groupe TIMA-SLS

### 2.5.2 Description des niveaux intermédiaires du *flow*

En plus des deux niveaux déjà existants dans le flot précédent (*System Level* et *Virtual Prototype*), deux niveaux intermédiaires ont été ajoutés : *Virtual Architecture Level* et *Transaction Accurate Level*. Ils seront décrits brièvement dans les paragraphes suivants.

#### ➊ Niveau *Virtual Architecture*

L’architecture virtuelle résulte d’une première étape de partitionnement de la spécification fonctionnelle initiale. Le partitionnement sépare les parties qui seront implémentées de façon matérielle de celles qui seront implémentées de façon logicielle.

Ce modèle permet d’abstraire tout le logiciel dépendant du matériel, le ou les processeurs et le sous-système processeur. Le modèle de programmation sur lequel peut s’appuyer le concepteur de la partie logicielle est une API de *HDS* (*Hardware Dependent Software*), similaire à celle d’un OS, plus des primitives de communication haut niveau.

A ce stade, l’architecture matérielle est globalement décomposée en sous systèmes, sans pour autant exiger que l’architecture matérielle soit raffinée.

Au niveau de l’architecture virtuelle, le concepteur ne dispose pas d’assez d’informations sur l’architecture matérielle cible.

L’objectif de ce modèle est d’apporter aux concepteurs une première estimation plus ou moins grossière des performances en fonction des choix faits sur le système d’exploitation et les primitives de communication haut niveau (gestion des tâches logicielles par exemple).

### ⌚ Niveau *Transaction Accurate*

Au niveau *Transaction Accurate*, la couche logicielle supérieure du modèle précédent est supposée raffinée. On considère donc que le HDS ne fait plus partie du modèle mais de l'application que l'on veut valider.

Cette étape est caractérisée par la spécification de la nature du protocole de communication entre les sous systèmes ainsi que du modèle abstrait de l'architecture locale au niveau de chaque sous système.

Pour un sous système logiciel, ceci correspond à une vision au niveau HAL de la machine d'exécution.

Les communications à ce niveau se font avec des adresses spécifiques par des primitives de type *read/write*. La gestion des ressources matérielles comme l'accès aux différents périphériques partagés ou encore aux processeurs sont modélisés.

L'objectif à ce niveau est d'apporter une plus grande précision quant à l'estimation des performances afin de pouvoir valider les décisions de conception prises en amont de manière plus précise.

Dans les deux niveaux *Virtual Architecture* et *Transaction Accurate*, nous utilisons l'exécution native comme mode d'exécution du logiciel embarqué afin de bénéficier de l'avantage d'une simulation rapide à ces niveaux intermédiaires.

L'exécution native signifie que le logiciel embarqué est compilé pour le processeur de la machine hôte (machine sur laquelle se déroule la simulation) et est exécuté par cette machine. Ceci est à mettre en opposition avec la compilation croisée (*cross compilation*) pour le processeur cible et l'interprétation des instructions binaires via le simulateur du processeur.

### ⌚ Niveau *Virtual Prototype*

A ce niveau, l'architecture logicielle/matérielle est décrite au niveau ISA/RTL. Le logiciel n'est autre qu'une suite d'instructions binaires placée dans une zone mémoire.

Le matériel est décrit en utilisant un langage de description de matériel (*HDL*). Ceci inclut l'architecture locale du nœud logiciel (processeur(s), mémoire(s), périphériques, etc.) mais aussi les autres parties du système.

A ce niveau, les deux parties logicielle et matérielle sont entièrement conçues.

Ici, nous utilisons un modèle de simulation classique qui considère que l'architecture du système est complètement raffinée et connue dans ses moindres détails. Ainsi, le logiciel embarqué doit être entièrement développé avant d'être compilé par le (les) processeur(s) cible(s). L'image binaire obtenue est alors prise en charge par des simulateurs de processeurs qui interprètent séquentiellement les instructions et interagissent avec un modèle entièrement raffiné de l'architecture matérielle.

## 2.6 Conclusion

Ce chapitre a été dédié à la description des systèmes qui font l'objet de ce mémoire, à savoir les systèmes multiprocesseurs monopuces. L'architecture de tels systèmes a été analysée, mettant l'accent sur la complexité aussi bien des parties logicielles que matérielles de ces architectures.

Face à cette complexité, les flots classiques ne semblent pas apporter une solution efficace qui facilite l'exploration et la validation de ces architectures en vue de maîtriser les coûts inhérents à leurs développements. L'approche proposée par le groupe TIMA-SLS propose des modèles de représentation intermédiaires permettant un raffinement graduel des systèmes logiciels/matériels.

Notre travail cible les méthodes et techniques de conception de systèmes. Dans ce travail, nous nous sommes concentrés sur un niveau d'abstraction supérieur dans le flot de conception des systèmes monopuces, nommé Architecture Virtuelle, qui sera décrit dans le chapitre suivant.

# Chapitre 3

## Niveau Architecture Virtuelle

### 3.1 Introduction

Les systèmes embarqués peuvent inclure plusieurs processeurs, qui exécutent des instructions spécifiques implémentées en logiciel pour des besoins de flexibilité. On estime que dans un futur proche, la complexité du code logiciel sera supérieure à celle de la partie matérielle et demandera par conséquent plusieurs hommes-années de durée de conception. Le logiciel ne pourra donc plus être développé en langage assembleur et une approche de conception à un niveau d'abstraction plus élevé est requise.

Dans ce chapitre, nous décrivons le niveau d'abstraction intermédiaire appelé Architecture Virtuelle sur lequel nous avons travaillé.

Pour aborder la conception du système dans une seule et même approche cohérente, les composants aussi bien logiciels que matériels sont modélisés avec un modèle unique. La méthodologie proposée dans le cadre de ce mémoire pour présenter un modèle de simulation du logiciel embarqué à un haut niveau d'abstraction sera alors exposée. Elle se base sur le niveau TLM.

Nous rappelons dans un premier lieu les principes de base de la méthodologie TLM pour le matériel. Dans un deuxième lieu, nous introduisons les concepts du niveau SW TLM; niveau TLM pour modéliser le logiciel embarqué.

### 3.2 Définition du niveau Architecture Virtuelle

Le niveau Architecture Virtuelle est appelé encore niveau système d'exploitation.

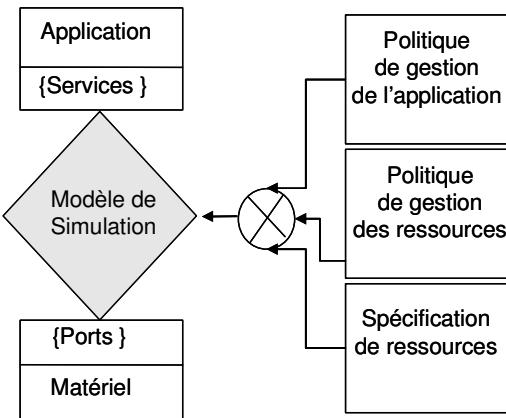

Le rôle de ce niveau est de palier aux imperfections et limites de ressources de l'architecture matérielle en implantant un certain nombre de politiques pour la gestion de ces ressources limitées. Un exemple de gestionnaire de ressources est l'Ordonnanceur qui permet de multiplexer une ressource « rare » sur l'ensemble des tâches logicielles actives à un instant donné.

Le modèle de simulation à ce niveau peut être vu comme suit (Figure 3.1):

Figure 3.1 – Modèle de simulation au niveau V.A

Ce niveau d’abstraction décrit l’architecture du système mais en ne se préoccupant que des objets fonctionnels pour l’application du système, c’est à dire en excluant complètement tous les détails liés à la réalisation. Le système est réalisé sous la forme de composants pouvant implémenter un ensemble de tâches logicielles ou une fonction matérielle mais sans aucune caractéristique précise pour le type du composant ou de sa structure interne.

La description du système au niveau Architecture Virtuelle est un ensemble de tels composants travaillant concurremment qui communiquent par des canaux de communication abstraits. Ces canaux seront détaillés plus tard.

Les canaux de communication utilisent des primitives transactionnelles définies par la norme TLM [5], pour représenter seulement le transfert ou le processus de synchronisation de données entre les composants sans aucune information sur l’implémentation du protocole de communication.

Le modèle du système au niveau V.A –niveau transactionnel- est toutefois exploitable en utilisant des outils et des méthodes pour l’analyse de performances. Ils explorent les différentes solutions possibles pour le partitionnement des tâches afin de définir une architecture optimale du système.

La Figure 3.2 montre les différents niveaux d’abstraction des deux parties matérielle et logicielle. Les lignes interrompues joignant un niveau d’abstraction donné du matériel avec un autre niveau du logiciel définit des niveaux d’intégration possibles permettant la conception et la simulation des systèmes logiciels/matériels.

En toute rigueur, au niveau fonctionnel, la notion de logiciel/matériel ne doit pas exister, car il s'agit d'une notion relative à l'implémentation. Cependant, pour la clarté de la représentation, nous dupliquons le niveau fonctionnel d'un côté comme de l'autre dans la figure [3].

Dans ce travail, nous nous intéressons par un nouveau niveau intermédiaire d'intégration Architecture Virtuelle (en anglais *Virtual Architecture V.A*). Il associe *HW TLM* à un niveau équivalent pour le logiciel qu'on appelle *SW TLM*.

Figure 3.2 – Niveau Architecture Virtuelle

Le niveau SW TLM correspond à une abstraction du niveau bas classique pour le logiciel (ISA). Au niveau SW TLM le logiciel est décrit comme un ensemble d'objets communicants ensemble et qui sont gérés par un environnement d'exécution correspondant au système d'exploitation.

La définition du niveau SW TLM est largement inspirée des recherches récentes sur la conception du logiciel embarqué. En effet, beaucoup de recherches se sont concentrées sur l'abstraction du niveau classique de modélisation RTL utilisé en tant que modèle d'intégration logiciel/matériel. La plupart de ces travaux ont adressé le côté matériel ou le côté logiciel du problème, mais aucun d'eux n'a fourni un modèle flexible et unifié de la plateforme logicielle/matérielle à un niveau d'abstraction plus élevé.

Du côté matériel, le niveau de modélisation transactionnel (TLM) a été identifié en tant que candidat approprié pour l'abstraction du niveau RTL. Dans tous ces travaux, le logiciel est considéré à un bas niveau d'abstraction ou simplement au niveau fonctionnel.

Du côté logiciel, beaucoup de travaux [4] [9] s'étaient concentrés sur la génération automatique des systèmes d'exploitation temps réel et du code pour le logiciel embarqué. Cependant, dans les travaux [4] et [9], l'interaction du modèle de simulation du système d'exploitation avec le matériel n'est pas clairement expliquée. De même dans [27], un raffinement logiciel/matériel a été proposé cependant ce travail se base sur un modèle fixe de l'interface matérielle.

La principale contribution de ce travail est de formaliser ces efforts, en utilisant le niveau TLM pour définir une plateforme de modélisation TLM pour le matériel et le logiciel. Ceci permet le développement d'un modèle unifié pour l'interface logicielle/matérielle pour faire face aux discontinuités de conception entre le matériel et le logiciel et permettre l'exploration rapide et efficace de l'espace des solutions architecturales.

Figure 3.3 – Flot de conception typique comportant le niveau V.A

La Figure 3.3 présente un flot de conception typique comportant le niveau V.A. Comme les flots de conception classiques, le flot proposé part d'une spécification (non exécutable) qui subit une première étape de partitionnement permettant le raffinement du logiciel et du matériel.

Dans la figure, le résultat de cette étape s'appelle «Architecture Système». Ceci correspond à une forme exécutable de la spécification (en utilisant SystemC par exemple) où des annotations sont simplement introduites pour distinguer les parties de l'application qui vont être mappées en matériel ou en logiciel respectivement. Le résultat final du flot est une architecture RTL qui peut servir comme entrée des outils conventionnels de synthèse physique.

Cependant contrairement aux flots de conception classiques, le flot proposé présente une étape intermédiaire de conception basée sur le concept V.A. L'architecture virtuelle résulte de l'intégration des parties logicielles et matérielles raffinées jusqu'au niveau TLM.

Au niveau V.A, le logiciel est modélisé au niveau OS comme un ensemble d'objets SW TLM qui coexistent et interagissent avec le reste des composants HW TLM.

Cette étape intermédiaire du flot permet de:

- palier aux discontinuités des flots de conception classiques et remédier aux problèmes liés à l'intégration tardive des architectures logicielles et matérielles d'un système MPSoC en proposant un niveau intermédiaire pour l'intégration logicielle/matérielle permettant une conception logicielle/matérielle graduelle;

- rompre la longue boucle d'exploration qui sépare classiquement le niveau système du niveau RTL final. Ceci facilite une exploration d'architecture rapide et efficace bénéficiant de la rapidité de simulation du TLM comparé à RTL.

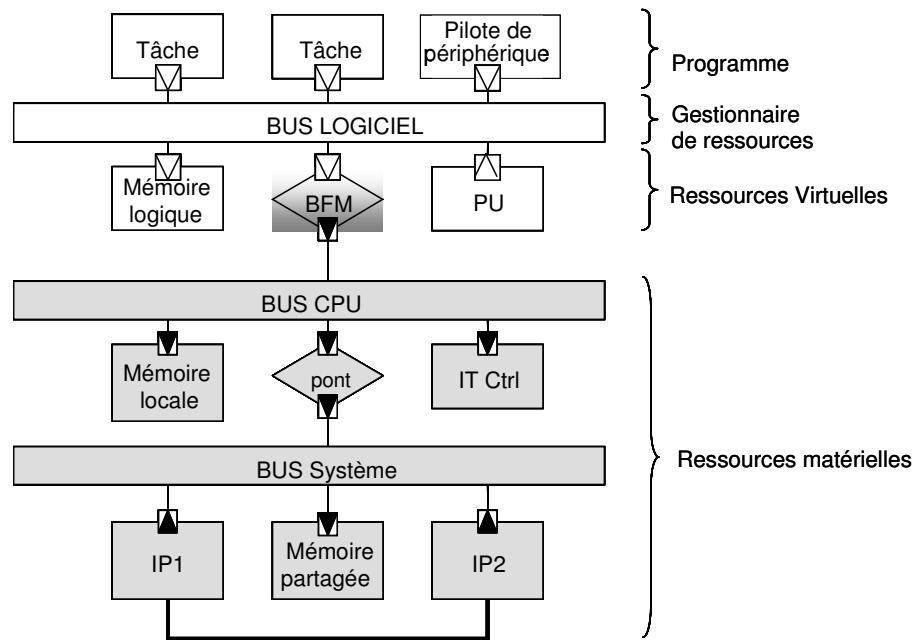

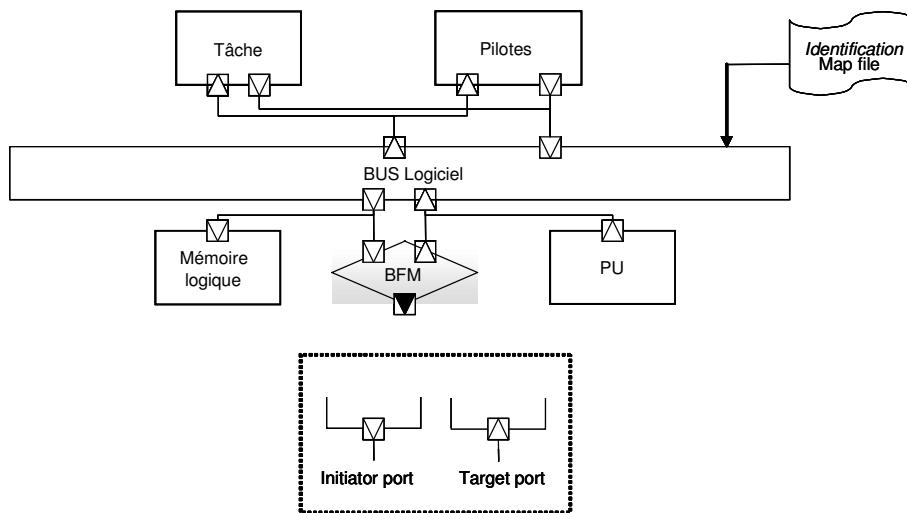

### 3.3 Vue d'ensemble d'un système au niveau V.A

La Figure 3.4 donne une vue d'ensemble d'un modèle conceptuel de l'interface logicielle/matérielle au niveau d'abstraction intermédiaire V.A. Les parties grises de la figure correspondent aux objets conventionnels du HW TLM.

Dans cette figure, l'exemple de conception est construit autour d'une architecture hiérarchique de bus composée d'un bus système auquel est connecté un bus CPU local via un pont (en anglais *bridge*).

A la différence de la conception TLM conventionnelle, le logiciel n'est ni exécuté sur un simulateur de jeux d'instructions, ni entièrement abstrait au niveau fonctionnel. Au niveau V.A le logiciel est modélisé au niveau OS comme un ensemble d'objets qui co-existent et interagissent avec le reste des composants HW TLM.

Figure 3.4 – Modèle conceptuel de l'Architecture Virtuelle

Dans une description *SW TLM*, nous identifions principalement trois couches conceptuelles :

- La couche Programme (*Program layer*) qui correspond au logiciel conçu par des programmeurs de logiciel. Ceci se compose des tâches de l'application ainsi que des pilotes de périphériques qui permettent la communication extérieure avec le matériel.

- La couche de gestion des ressources (*resource management layer*) correspond à ce qu'on appelle le bus logiciel (*SW bus*). Cette entité abstrait le vrai système d'exploitation et permet la coordination et l'arbitrage des composants. Cette couche gère de même la communication entre les différents composants logiciels.

La communication logicielle est abstraite au niveau service. En effet, la communication est représentée comme une combinaison de requêtes et de services. Les différents modules communiquent par des requêtes de services,

via le bus logiciel qui garantit le routage et la synchronisation des connexions établies.

Les services offerts par le bus logiciel dépendent largement du système d'exploitation. On peut classer certains services dans des catégories tels que les services de communication et de synchronisation inter tâches, les services de communication externes via les pilotes de périphériques et les services d'allocation des ressources.

- La couche des ressources virtuelles (*virtual resource layer*) qui spécifie, d'un point de vue programmeur, quel type de ressources disponibles dans le sous système logiciel (le nœud logiciel de la Figure 2.1).

Cette couche fournit une abstraction de l'ensemble des ressources disponibles au niveau du nœud logiciel. En effet, l'application dispose d'un certain nombre de tâches qui vont être exécutées sur différentes ressources de calcul (*Processing Elements*), elles ont besoin pour cela d'allouer les ressources de stockage nécessaires à leur exécution. Les mémoires sont utiles pour la mémorisation des données ou des instructions, et sont aussi un passage fréquent pour les communications.

Dans notre cas, nous distinguons deux types de ressources virtuelles : mémoire logique et unité virtuelle de traitement (*Processing Unit*).

Un objet important qui pourrait être qualifié comme un objet TLM hybride logiciel/matériel est le modèle fonctionnel du bus (en anglais *BFM: Bus Functional Model*). Un BFM est un pont spécial qui permet de relier le bus logiciel avec le bus matériel (le bus CPU). Son rôle principal est de transmettre les accès externes du logiciel au matériel. Il est également responsable de transférer les interruptions matérielles venant du côté matériel aux composants appropriés du côté logiciel.

Cette description a nécessité une bonne compréhension du niveau transactionnel d'un point de vue théorique.

Dans les sections suivantes, nous rappelons donc les concepts de base pour le HW TLM ensuite ceux pour le SW TLM sont décrits et leur application pour le raffinement du logiciel est expliquée.

### 3.4 Concepts de base du TLM pour le matériel

Dans cette section, la méthodologie conventionnelle HW TLM est présentée. Nous cherchons à donner de même un aperçu sur la structure TLM et nous décrivons brièvement les niveaux TLM.

#### 3.4.1 Méthodologie TLM

TLM est un niveau plus abstrait que RTL. Ceci est dû à la réduction de la quantité de détails que le concepteur doit manipuler facilitant donc la modélisation.

Ce niveau, moins détaillé que le niveau RTL, représente uniquement ce qui se passe au niveau système, en terme d'échange de données et de synchronisation système, sans se soucier de la micro-architecture des blocs.

TLM est décrit et expliqué par beaucoup de travaux [6] [7] [10]. Il est construit comme un niveau élevé d'API qui définit comment les composants matériels communiquent entre eux.

Un modèle TLM se base uniquement sur des appels de fonctions et des transferts de paquets de données. L'idée est de représenter au plus près l'intention du concepteur quant au comportement global du circuit, sans rentrer dans les détails de la description des signaux réalisés au niveau RTL.

L'objectif de ce niveau est de développer du logiciel embarqué et de faire des études d'architectures à un haut niveau d'abstraction. Il permet de même d'accélérer le temps de simulation.

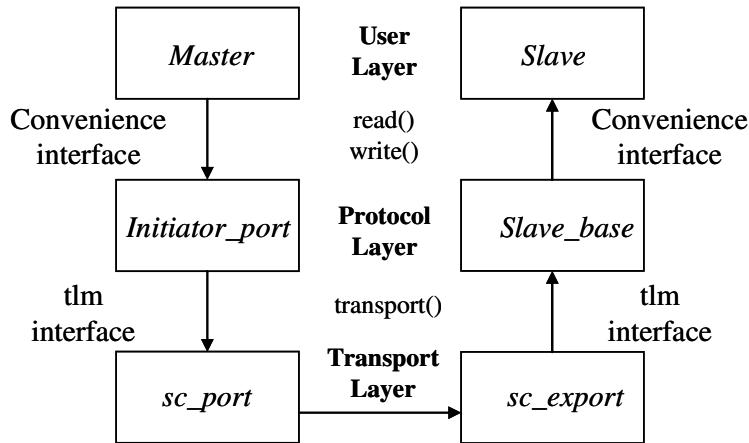

L'API OSCI TLM est construite comme un ensemble d'interfaces qui définissent comment les modules communiquent entre eux.

En effet, l'interface de protocole définit la sémantique pour transférer une transaction entre deux points différents d'un même système tel que *tac\_if*, *basic\_if*, *synchro\_if*, etc.

TLM définit un ensemble d'interfaces génériques et réutilisables (bloquantes/non bloquantes, unidirectionnelles/bidirectionnelles) par une approche en couches tel que *tlm\_transport\_if<req,resp>*, *tlm\_put\_if<req>*, *tlm\_get\_if<req>*, etc. (voir Figure 3.5):

- Couche Utilisateur (*User layer*) :

Dans le jargon TLM, cette interface s'appelle en anglais « *convenience interface* ». Elle se compose typiquement de méthodes qui donnent un sens aux

utilisateurs du protocole en question par exemple *read*, *write*, *burst read* et *burst write*. L'utilisateur va utiliser les ports initiateurs qui fournissent les moyens d'implémenter ces interfaces et définit des modules cibles (*target*) qui héritent de ces interfaces [6]. Les transactions sont envoyées par le module initiateur par le biais de *initiator\_port* et sont reçues et traitées par le module target selon l'implémentation de l'utilisateur.

Ces implémentations sont visibles au module target grâce à *sc\_export* de SystemC qui est reliée au module target et qui donne accès à ces implémentations.

A ce niveau, la couche protocole est transparente pour l'utilisateur.

- Couche Protocole (*Protocol layer*) :

La couche protocole se compose de [6] :

- classes de requête et de réponse qui encapsulent le protocole. Principalement ceci correspond à la définition d'échange des transactions (l'information à échanger entre l'initiateur et le target: adresse, données, statut, longueur, etc.);

- port initiateur qui hérite de *sc\_port* ;

- classe *slave\_base* qui implémente les interfaces TLM.

Le module target doit hériter de la classe *slave\_base*.

L'utilisateur pourra après utiliser les classes *initiator\_port* et *slave\_base*. Il faut noter que ce mécanisme de communication est efficace de point de vue temps d'exécution. En effet grâce à la liaison «*port-to-export*» (introduite par SystemC-2.1.v1) l'appel à l'API du protocole résulte à l'exécution de l'implémentation dans le côté du target mais dans le même contexte du *thread*<sup>13</sup> initiateur. Ainsi, la communication entre un maître et un esclave n'implique pas un changement de contexte (*context switch*) (coûteux en temps de simulation).

- Couche Transport (*Transport layer*):

La couche Transport forme la couche de base pour la couche protocole et la couche utilisateur. Elle donne l'accès aux interfaces TLM virtuelles par la liaison SystemC *sc\_port* à *sc\_export*, à savoir *initiator\_port* à *target\_port*.

L'interface TLM hérite de la classe *sc\_interface* de SystemC. Elle sert comme une base commune pour faciliter l'interopérabilité de divers modèles TLM définis par différentes compagnies.

---

<sup>13</sup> Processus léger

Figure 3.5 – Architecture TLM [6]

La société ST-Microelectronics; qui a adopté le niveau TLM dans la conception; a construit un ensemble de protocoles qui sont conformes à OSCI TLM à savoir les protocoles TAC et Synchro.

*TAC* acronyme de *Transaction Accurate Communication* est construit sur la base du standard TLM OSCI. Il se base sur l'interface *tlm\_transport\_if* (interface bloquante bidirectionnelle) qui comporte la requête et la réponse dans un même transfert TAC, *status* fait aussi partie d'une réponse TAC.

Le protocole Synchro est construit sur la base de l'interface *put* de TLM et représente la synchronisation entre plusieurs composants. Il se base sur l'interface *tlm\_blocking\_put\_if* (interface bloquante unidirectionnelle).

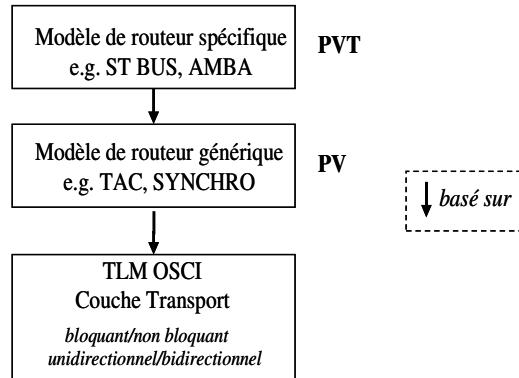

### 3.4.2 Les niveaux TLM PV et PVT

Il existe de nombreuses variantes dans le niveau d'abstraction TLM. Néanmoins, nous pouvons distinguer deux grands types de modèles TLM (voir Figure 3.6) tels que définis dans la littérature.

Figure 3.6 – Les couches TLM

Le premier, appelé « *Programmer View* » (PV), est une représentation purement fonctionnelle du circuit sans référence à aucune notion temporelle. A ce niveau, le modèle contient toutes les informations nécessaires (et pas plus) pour que les équipes de développement logiciel puissent travailler, c'est-à-dire faire tourner le logiciel embarqué final, système d'exploitation compris. Le protocole utilisé à ce niveau est générique (tel est l'exemple de TAC) et la synchronisation reflète la dépendance causale entre les différentes unités de calcul et n'est pas basée sur les contraintes de temps.

Le second type, appelé « *Programmer View + Timing* » (PVT), intègre des informations sur les délais (*timing*) qui permettent notamment de travailler sur l'analyse des performances du circuit, sans trop pénaliser les temps de simulation.

Une plateforme au niveau PVT est une plateforme au niveau PV avec son inter connecteur non temporisé, à qui on a ajouté un modèle temporisé du bus qui correspond à un bus spécifique (par exemple *STBus, AMBA*).

Dans une plateforme PVT, on a les différents composants PV individuels (*PV IP<sup>14</sup>*) et leurs modules temporisés correspondants; un ou plusieurs routeurs non temporisés et leurs correspondants temporisés, par exemple *TAC router* et *STbus router* en se référant à la plateforme PVT de ST. Dans une plateforme PVT, l'annotation du temps est effectuée dans le module temporisé de chaque composant et dans le routeur temporisé qui simule les délais de transfert pour chaque transaction.

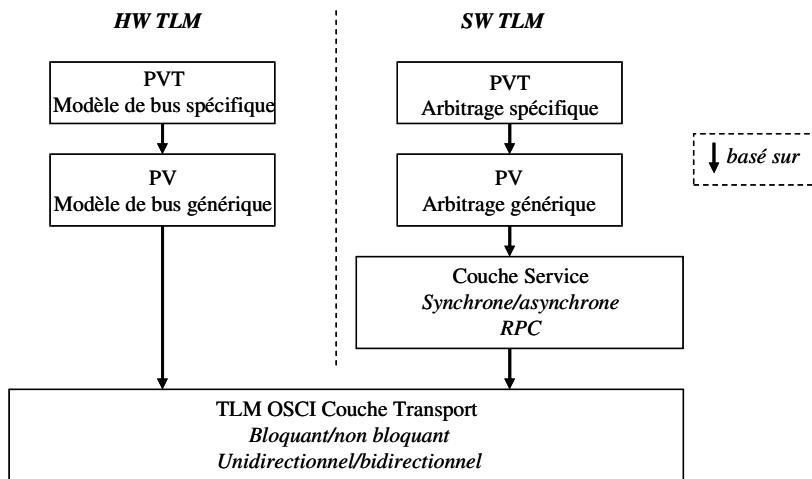

TLM rapproche l'écart entre les modèles fonctionnels de spécifications et les implémentations RTL par une amélioration progressive de l'infrastructure de communication matérielle.

Du côté logiciel, peu de recherches ont abordé la communication logicielle à un niveau conforme à TLM. Le flot de développement logiciel passe brusquement d'un modèle fonctionnel au niveau d'abstraction le plus bas.

D'où le but des chapitres suivants est d'introduire le nouveau concept TLM destiné pour le développement logiciel. Notre méthodologie raffine le logiciel embarqué au niveau Architecture Virtuelle.

---

<sup>14</sup> *Intellectual Property*

### 3.5 Concepts de base du TLM pour le logiciel

Dans cette section, nous présentons l'environnement de conception dans lequel nous avons développé et validé notre méthodologie TLM. Nous allons tout d'abord exposer les concepts de base. Ensuite, nous donnerons une brève présentation de la constitution du niveau SW TLM.

#### 3.5.1 Description des composants SW TLM

La Figure 3.7 illustre les différents composants SW TLM.

Dans une plateforme SW TLM il y a des modules qui requièrent des services (initiateurs en anglais *initiator*), d'autres qui fournissent ces services (cibles en anglais *target*). Ils communiquent en envoyant des requêtes et réponses de part et d'autre. Ces modules sont des composants logiciels qui peuvent être classés comme suit :

- composants de l'application (par exemple tâche applicative);

- ressources abstraites;

- pilotes de périphériques;

- bus logiciel.

Les tâches logicielles peuvent communiquer entre elles ou avec des tâches matérielles. Elles appellent les services du système d'exploitation et les services de communication et peuvent être des modules maîtres ou esclaves.

Figure 3.7 – Les composants SW TLM

Les ressources abstraites se composent des mémoires logiques et des unités de traitement (en anglais *Processing units*).

Dans le processus de raffinement de la communication, les zones de stockage matérielles apparaissent dans l'architecture matérielle. Ces zones sont partagées et permettent l'échange de données. Elles pourraient être mappées aux mémoires matérielles locales ou externes.

Au niveau application, le programmeur n'est pas censé savoir le mapping matériel. C'est pourquoi, il adresse habituellement la mémoire logique. Le processus de raffinement est alors responsable de mapper ces adresses logiques une fois que l'architecture est fixe.

Les unités de traitement sont des composants virtuels responsables de l'exécution du logiciel embarqué. Ils appellent le service d'initialisation (*BOOT service*).

Les pilotes de périphériques permettent aux composants de l'application de réagir avec les périphériques matériels. Les pilotes TLM adressent une ou plusieurs mémoires logiques qui connaissent le mapping de la mémoire physique. Ils ont besoin également des services du système d'exploitation pour accéder aux périphériques matériels correspondants.

Le bus logiciel est le conducteur de tout le noyau logiciel. Il pourrait être défini comme étant le chemin logique qui sert des tâches logicielles multiples ou des unités logicielles de calcul et de communication à travers un modèle d'OS. Son rôle principal est:

- assurer l'ordonnancement des tâches et le partage du temps;

- intercepter les transactions logiques et les traiter;

- acheminer ces transactions logiques au *BFM*.

Le bus logiciel a deux mécanismes importants à savoir routage et arbitrage. Le premier est responsable d'acheminer les transactions aux différents modules logiciels, tandis que le deuxième résout les requêtes concurrentes de services.

Dans la section suivante, nous allons décrire la structure du niveau SW TLM.

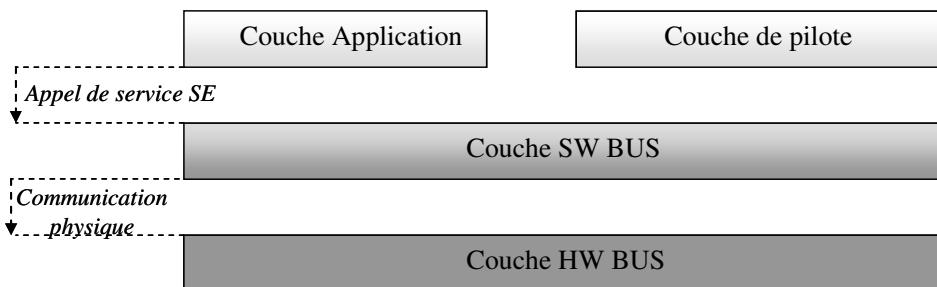

### 3.5.2 Structure du SW TLM

Comme dans le HW TLM, nous définissons un mécanisme de passage de transactions dans l'architecture de communication logicielle. Cette architecture serait structurée autour de différentes couches (voir la Figure 3.8):

- Couche Application « *Application layer* »:

Cette couche peut être définie comme la couche de calcul. En effet, elle se compose des tâches de l'application. À ce niveau, nous supposons que le programmeur n'a aucune idée sur l'architecture de communication. Au niveau de cette couche, l'application requiert des services d'OS et des services de communication.

- Couche de pilote « *communication driver layer* »:

Cette couche inclut les pilotes TLM et les mémoires logiques. Ces deux genres d'éléments SW TLM coopèrent – par la communication logique avec la couche du bus logiciel – pour contrôler le processus de communication. En fait, chaque pilote TLM adresserait une ou plusieurs mémoires logiques.

Cette couche est également responsable de répondre aux demandes d'interruptions destinées à la couche application.

- Couche du bus logiciel « *SW BUS layer* »:

Elle est le conducteur de tout le nœud logiciel. Elle abstrait le système d'exploitation.

Généralement un système d'exploitation peut être vu comme un ensemble de couches de services: une couche API, une couche des services de base du système d'exploitation et une couche d'abstraction du matériel.

- Couche du bus matériel « *HW BUS layer* »:

C'est le bus physique, le réseau de communication matérielle. Il peut être un bus CPU local ou un bus système.

Figure 3.8 – Architecture en couches de la communication logicielle

## 3.6 Conclusion

Dans ce chapitre, nous avons défini le niveau Architecture Virtuelle, un niveau qui abstrait le système d'exploitation ainsi que l'architecture matérielle.

Puis, dans un deuxième temps, nous avons présenté la méthodologie SW TLM conçue pour unifier la modélisation du logiciel embarqué au niveau V.A.

# Chapitre 4

## Implémentation (SW TLM)

### 4.1 Introduction

Cette partie du rapport expose l'implémentation du SW TLM. En premier lieu, elle présente la hiérarchie du SW TLM. En second lieu, elle décrit ses différentes interfaces de base.

### 4.2 Choix du langage

Le choix de travailler avec un langage de conception au niveau système (*SLDL : System Level Design Language*) (tel que SystemC ou SpecC) est important pour assurer la portabilité du modèle.

La description des fonctionnalités du modèle doit être donc faite dans un langage de description de haut niveau. Ceci permet de valider rapidement le modèle et de profiter d'un environnement de simulation efficace. Pour cela nous avons utilisé la bibliothèque SystemC.

Elle permet de profiter des mécanismes d'héritage ou de polymorphisme du C++ pour décrire des ensembles hiérarchiques [18]. Par ailleurs, cette solution offre la possibilité de simuler conjointement des parties logicielles et matérielles. Ceci se révèle très utile dans notre cas puisque le système complet est composé d'éléments hétérogènes logiciels et matériels.

Plus particulièrement, SystemC est considéré d'un point de vue industriel un standard pour la modélisation TLM et la conception au niveau système et à la co-simulation des systèmes logiciels/matériels.

En bref, SystemC est un langage et un noyau de simulation basés sur C++ qui permet la représentation des composants logiciels et matériels et des communications à différents niveaux d'abstraction. Il permet la modélisation et la simulation de systèmes logiciels/matériels globalement synchrones, ou asynchrones avec un modèle à événements. Il convient pour l'augmentation de la complexité de conception des systèmes, en fournissant un modèle exécutable tôt dans le cycle de conception.

Un modèle SystemC est composé des éléments suivants :