## Table des matières

|                                                                                |           |

|--------------------------------------------------------------------------------|-----------|

| <b>TABLE DES MATIERES .....</b>                                                | <b>1</b>  |

| <b>INTRODUCTION GENERALE .....</b>                                             | <b>5</b>  |

| <b>CHAPITRE I: LANGAGE ET ENVIRONNEMENT DE SIMULATION : ETAT DE L'ART.....</b> | <b>10</b> |

| I.1 INTRODUCTION .....                                                         | 10        |

| I.2 LES SYSTEMES ENFOUIS (EMBARQUES).....                                      | 10        |

| I.3 SIMULATEUR ANALOGIQUE.....                                                 | 12        |

| I.4 SIMULATEUR MIXTE (ANALOGIQUES, NUMERIQUES).....                            | 12        |

| I.4.1 SABER.....                                                               | 13        |

| I.4.2 Verilog -AMS.....                                                        | 14        |

| I.4.3 VHDL-AMS .....                                                           | 14        |

| I.5 LA SIMULATION MATERIELLE / LOGICIELLE .....                                | 16        |

| I.5.1 La conception basée sur le langage C.....                                | 16        |

| I.5.2 Les outils de haut-niveau.....                                           | 20        |

| I.6 LES METHODES POUR LA CONCEPTION LOGICIELLE .....                           | 21        |

| I.6.1 SADT et SA/RT des méthodologies à l'origine de la réflexion système..... | 22        |

| I.6.2 UML : le langage uniifié de modélisation.....                            | 22        |

| I.7 AUTRES APPROCHES METIERS ET MIXTES .....                                   | 24        |

| I.8 APPROCHE CLASSIQUE DE LA VALIDATION LOGICIELLE.....                        | 26        |

| I.9 OUTILS EXISTANTS .....                                                     | 30        |

| I.10 CONCLUSION .....                                                          | 31        |

| <b>CHAPITRE II: PLATEFORMES DE SIMULATION .....</b>                            | <b>34</b> |

| II.1 INTRODUCTION .....                                                        | 34        |

| II.2 SIMULATION VHDL (MODELSIM).....                                           | 34        |

| II.3 SIMULATION MATLAB .....                                                   | 37        |

| II.4 XILINX ISE 7.1I.....                                                      | 39        |

| II.5 CHIP SCOPE PRO 7.1I .....                                                 | 43        |

| II.5.1 Flot de conception.....                                                 | 46        |

| II.5.2 Conclusion .....                                                        | 46        |

| II.6 PLANACHEAD 7.1.10 .....                                                   | 47        |

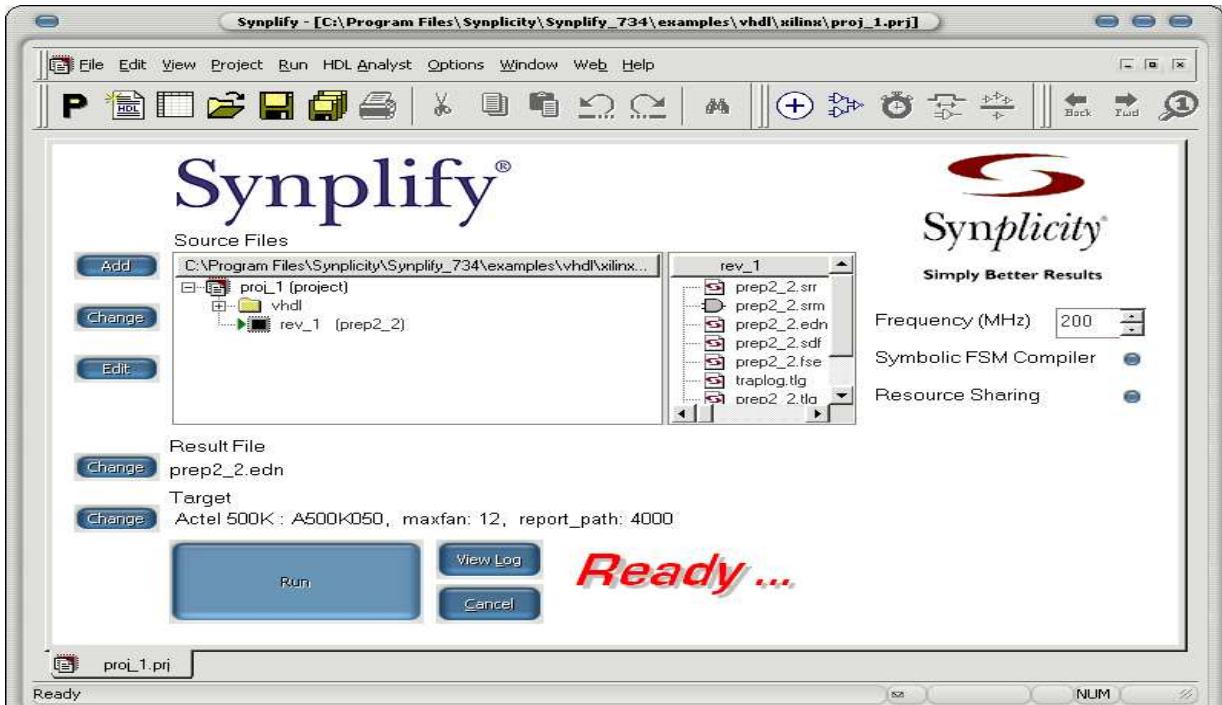

| II.7 SYNPLIFY 7.3.4 .....                                                      | 48        |

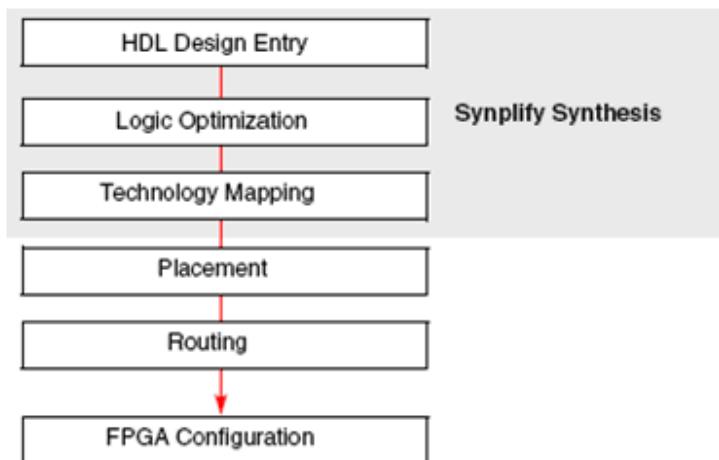

| II.7.1 Entrer de conception VHDL.....                                          | 49        |

| II.7.2 Logique d'optimisation (Compilation).....                               | 50        |

| II.7.3 Technologie de traçage .....                                            | 50        |

| II.7.4 Placement.....                                                          | 50        |

| II.7.5 Routage .....                                                           | 51        |

| II.7.6 Configuration FPGA .....                                                | 51        |

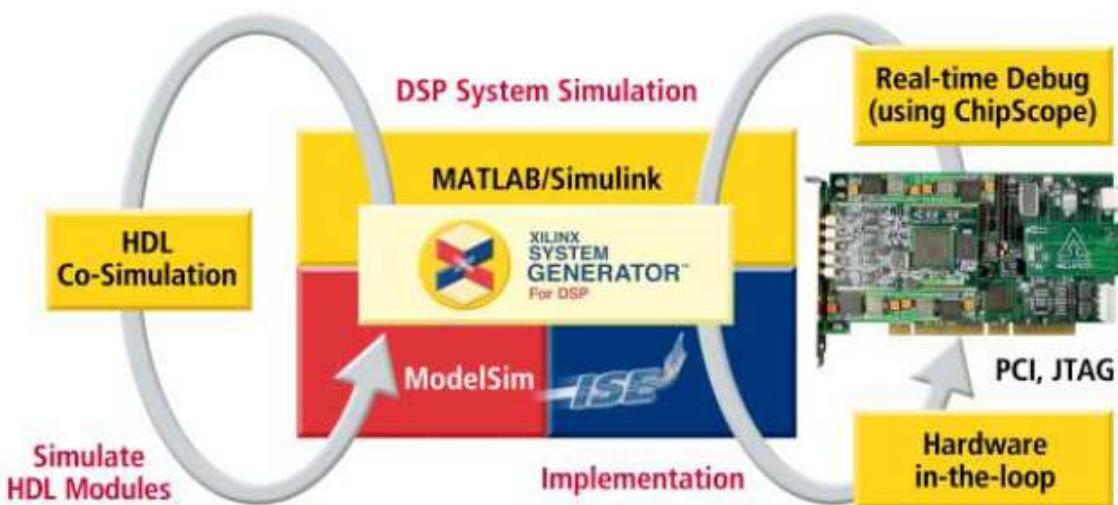

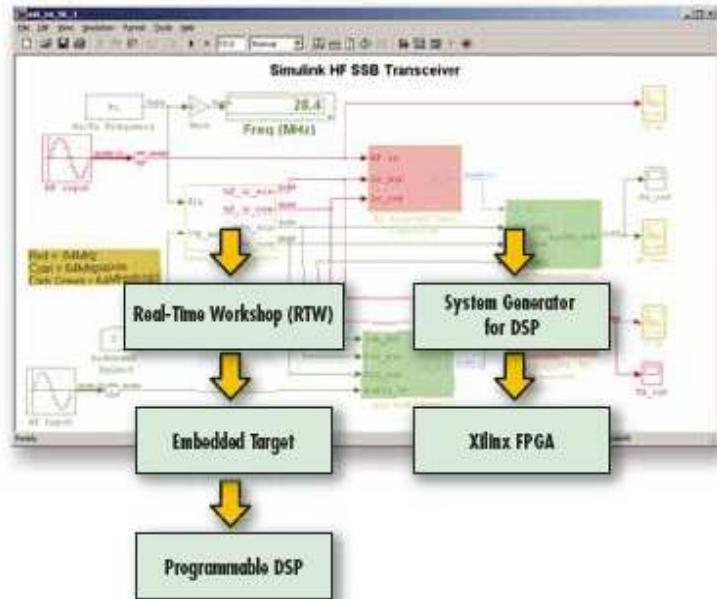

| II.8 SYSTEM GENERATOR FOR DSP.....                                             | 51        |

| Flot de conception du System Generator.....                                    | 51        |

| II.9 SIMULATION FPGA .....                                                     | 53        |

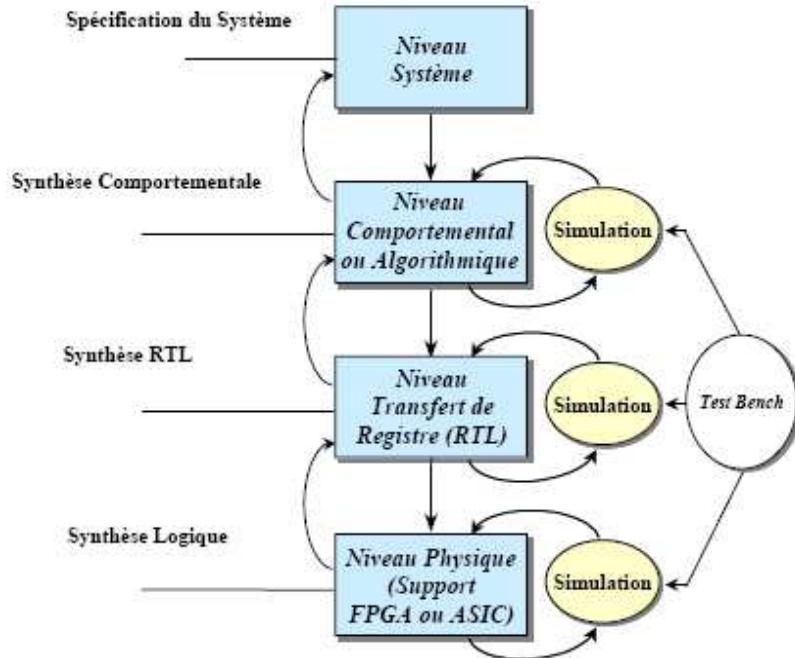

| II.9.1 Les méthodes de conception.....                                         | 53        |

| II.9.2 La méthode descendante « top-down » .....                               | 53        |

| II.9.3 Les contraintes actuelles de conception .....                           | 55        |

| II.10 CONCLUSION .....                                                         | 57        |

| <b>CHAPITRE III: CO-SIMULATION MATLAB / VHDL .....</b>                         | <b>59</b> |

| III.1 INTRODUCTION .....                                                       | 59        |

| III.2 VUE D'ENSEMBLE DE BOÎTE À OUTILS DE CONVERSION .....                     | 59        |

|                                                       |                                                                  |           |

|-------------------------------------------------------|------------------------------------------------------------------|-----------|

| III.3                                                 | LINK FOR MODELSIM .....                                          | 61        |

| III.4                                                 | ENVIRONNEMENT DE CO-SIMULATION .....                             | 62        |

| III.5                                                 | CHOIS DU PORT TCP/IP .....                                       | 65        |

| III.6                                                 | EXEMPLE DE CO-SIMULATION MATLAB/ VHDL .....                      | 65        |

| III.7                                                 | CONCLUSION .....                                                 | 70        |

| <b>CHAPITRE IV: CO-SIMULATION MATLAB / FPGA .....</b> |                                                                  | <b>72</b> |

| IV.1                                                  | INTRODUCTION .....                                               | 72        |

| IV.2                                                  | INTERFACE MATLAB/FPGA .....                                      | 72        |

| IV.3                                                  | MODE DE COMMUNICATION DE LA PLATEFORME .....                     | 74        |

| IV.3.1                                                | <i>Model de conception système .....</i>                         | 76        |

| IV.3.2                                                | <i>Algorithme de développement .....</i>                         | 77        |

| IV.3.3                                                | <i>Simulation et génération VHDL .....</i>                       | 77        |

| IV.3.4                                                | <i>Verification .....</i>                                        | 78        |

| IV.4                                                  | EXPERIMENTATIONS ET RESULTATS .....                              | 79        |

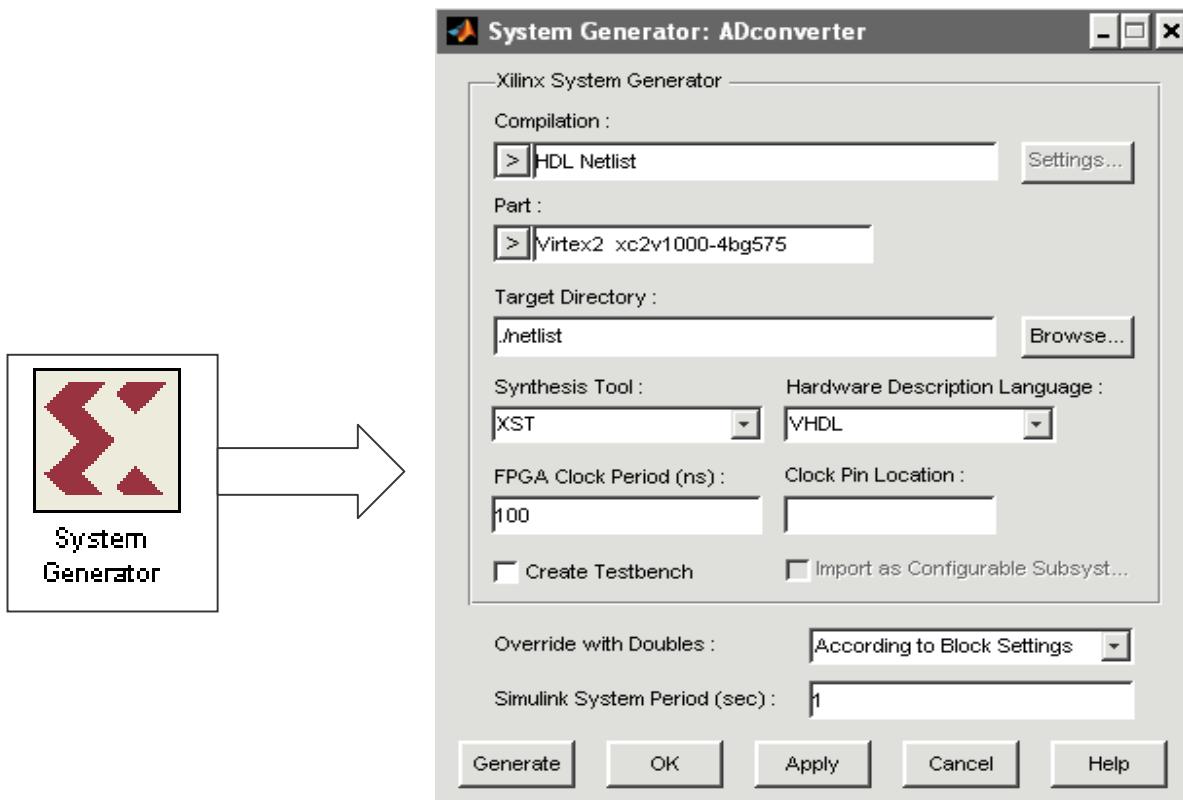

| IV.4.1                                                | <i>Différents types de compilation du System Generator .....</i> | 83        |

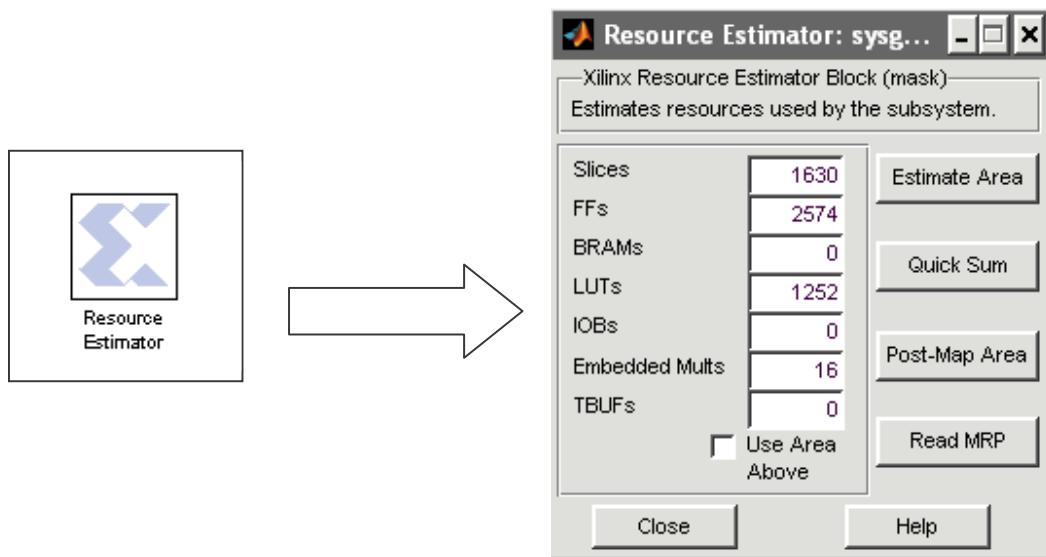

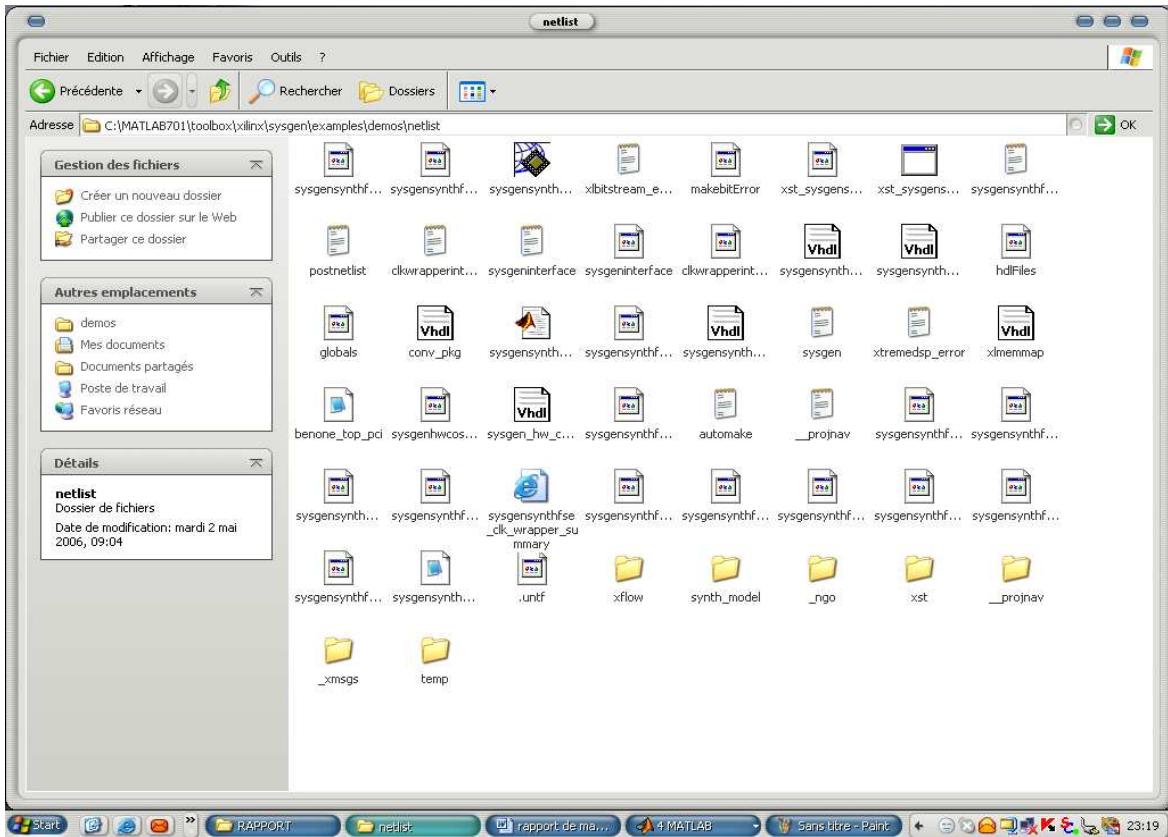

| IV.4.2                                                | <i>Résultats de System Generator .....</i>                       | 84        |

| IV.4.3                                                | <i>Résultats expérimentaux .....</i>                             | 86        |

| IV.5                                                  | CONCLUSION .....                                                 | 90        |

| <b>CONCLUSIONS ET PERSPECTIVES .....</b>              |                                                                  | <b>92</b> |

| <b>BIBLIOGRAPHIE.....</b>                             |                                                                  | <b>94</b> |

# Table des figures

- Figure 1 :** Quelques outils qui supportent System C.

- Figure 2 :** Flow de conception classique.

- Figure 3 :** Interface logiciel-matériel en simulation VHDL.

- Figure 4 :** Étapes pour la validation du logiciel dans un flot classique.

- Figure 5 :** Temps de conception et coût de débogage.

- Figure 6 :** Le simulateur VHDL.

- Figure 7 :** Utilisation du VHDL pour les niveaux de conception.

- Figure 8 :** L'interface de MATLAB 7.

- Figure 9 :** L'interface ISE 7.1i de Xilinx.

- Figure 10 :** ISE Foundation 7.1i de Xilinx.

- Figure 11 :** ISE BaseX 7.1i de Xilinx.

- Figure 12 :** ISE WebPACK 7.1i de Xilinx.

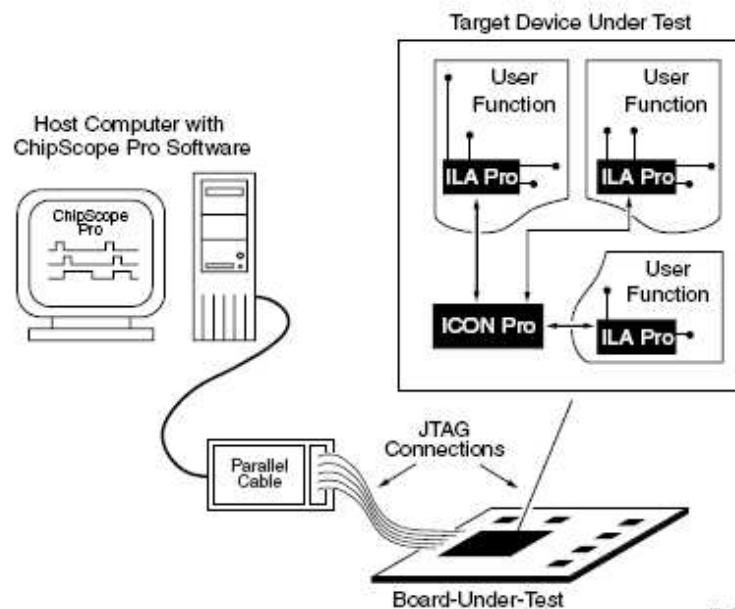

- Figure 13 :** Connections JTAG.

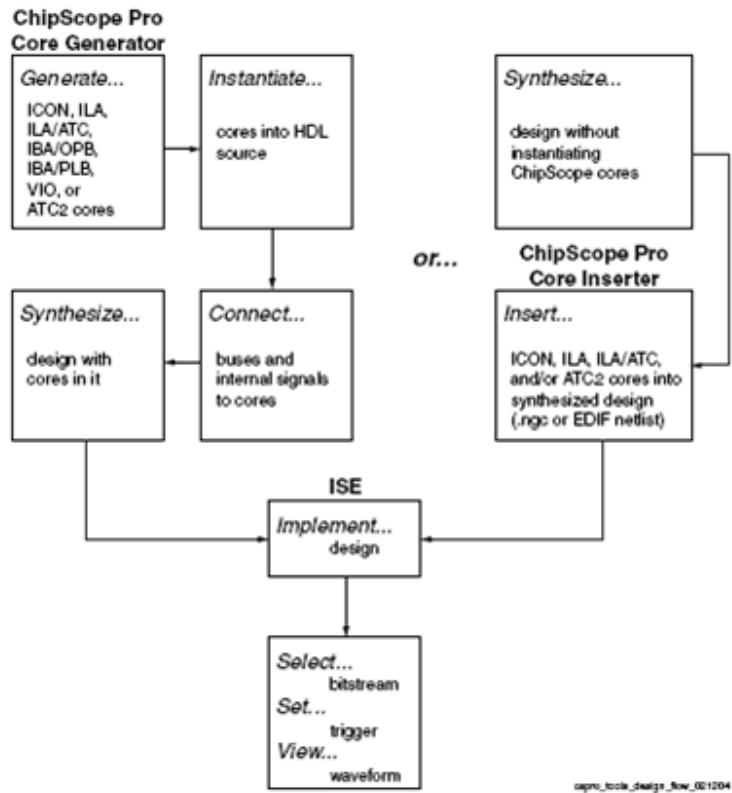

- Figure 14 :** Flot de conception de Chip Scope.

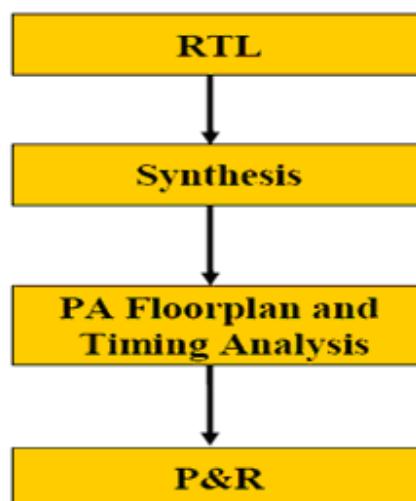

- Figure 15 :** Flot de conception de Plan Ahead pour les FPGAs.

- Figure 16 :** Interface de Synplify 7.3.4.

- Figure 17 :** Les différentes étapes de conception supporter par Synplify.

- Figure 18 :** Communication de System Generator avec la plateforme.

- Figure 19 :** Schéma hiérarchique de la méthode de conception descendante.

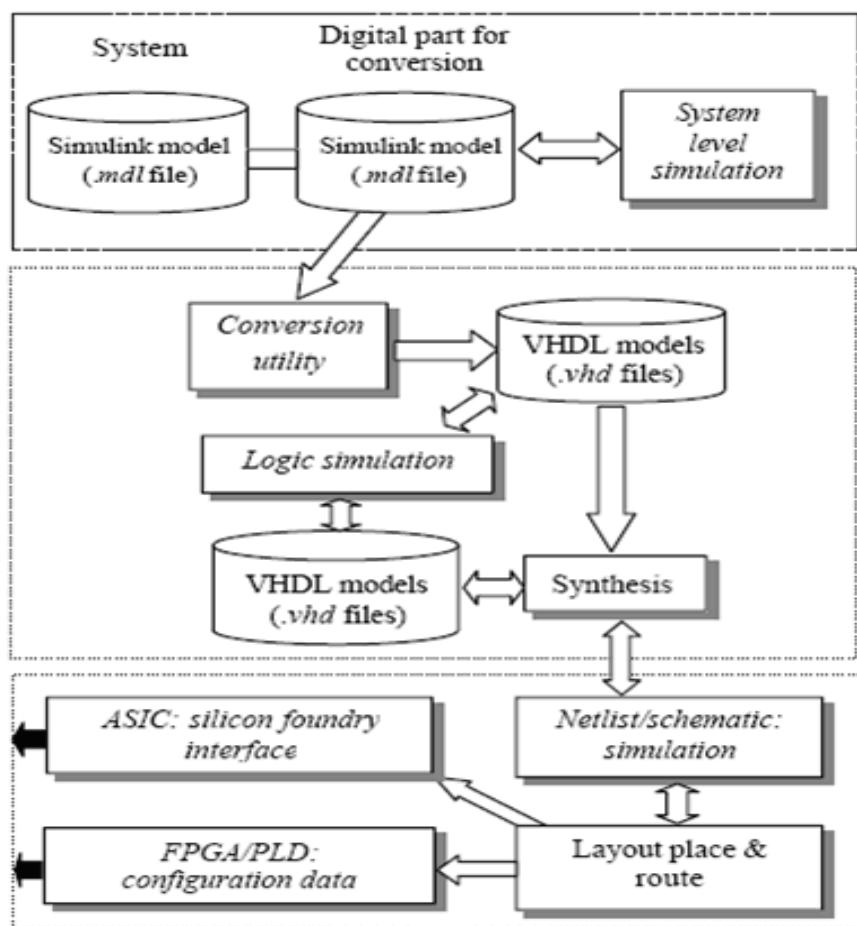

- Figure 20 :** Routine de conversion dans le processus de conception.

- Figure 21 :** interface graphique

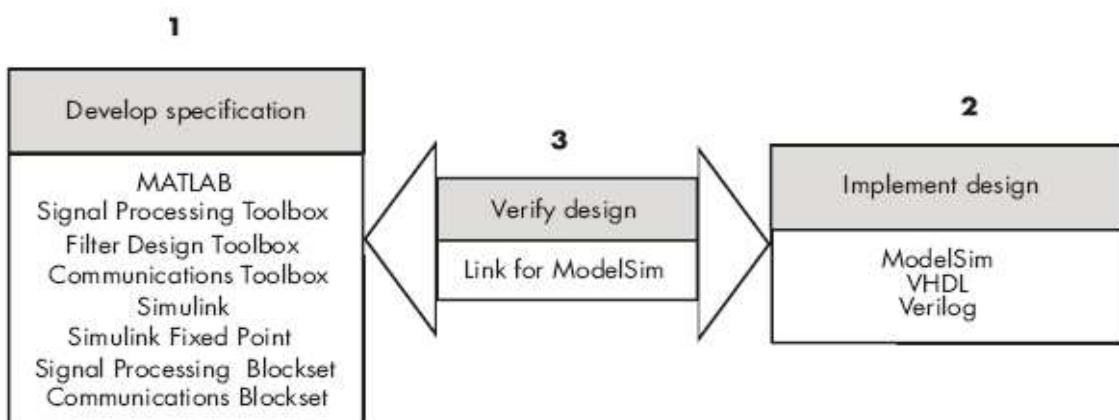

- Figure 22 :** Le rôle de Link for ModelSim pour communiquer MathWorks et ModelSim.

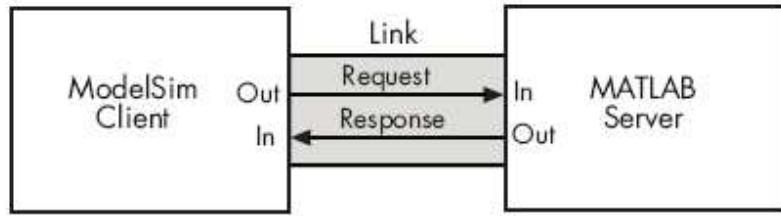

- Figure 23 :** Mode de communication entre MATLAB et ModelSim.

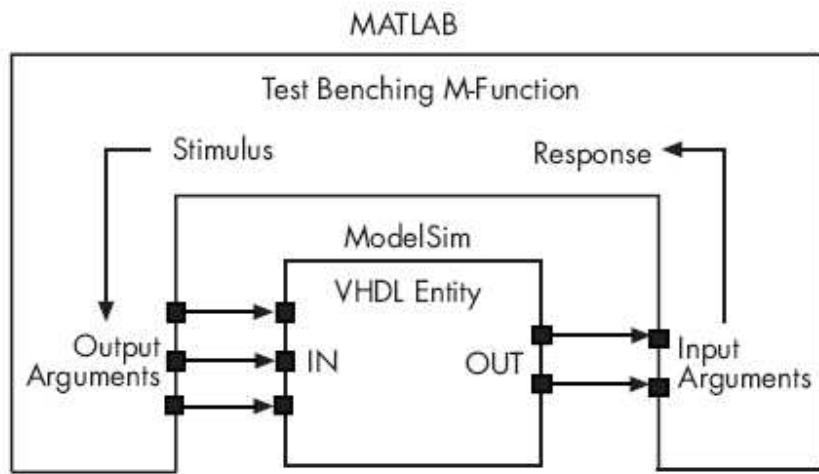

- Figure 24 :** Principe de communication de MATLAB et ModelSim pour la phase de test.

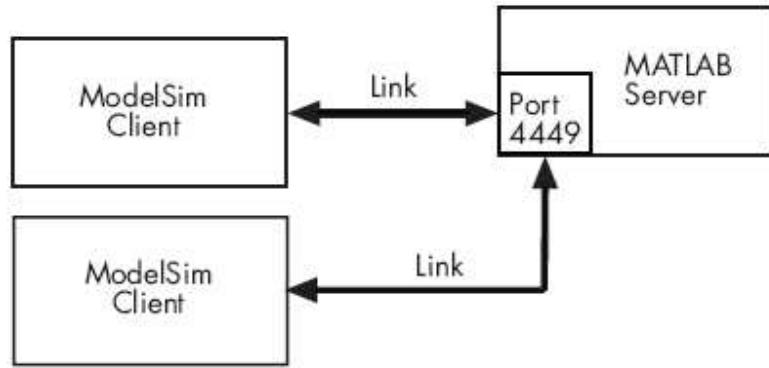

- Figure 25 :** Multiple-client communique avec MATLAB simultanément.

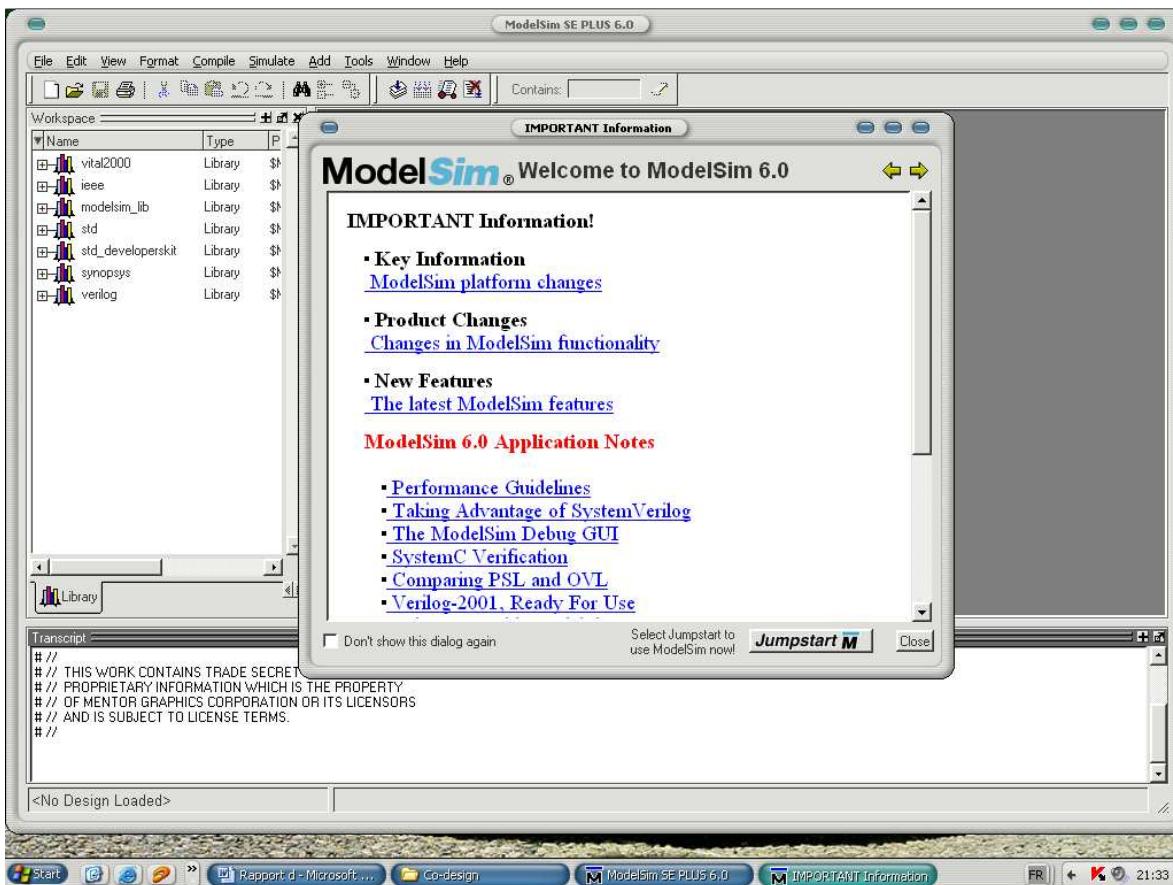

- Figure 26 :** ModelSim 6.0 de Xilinx.

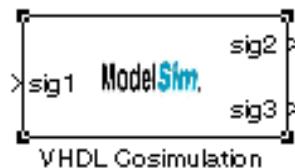

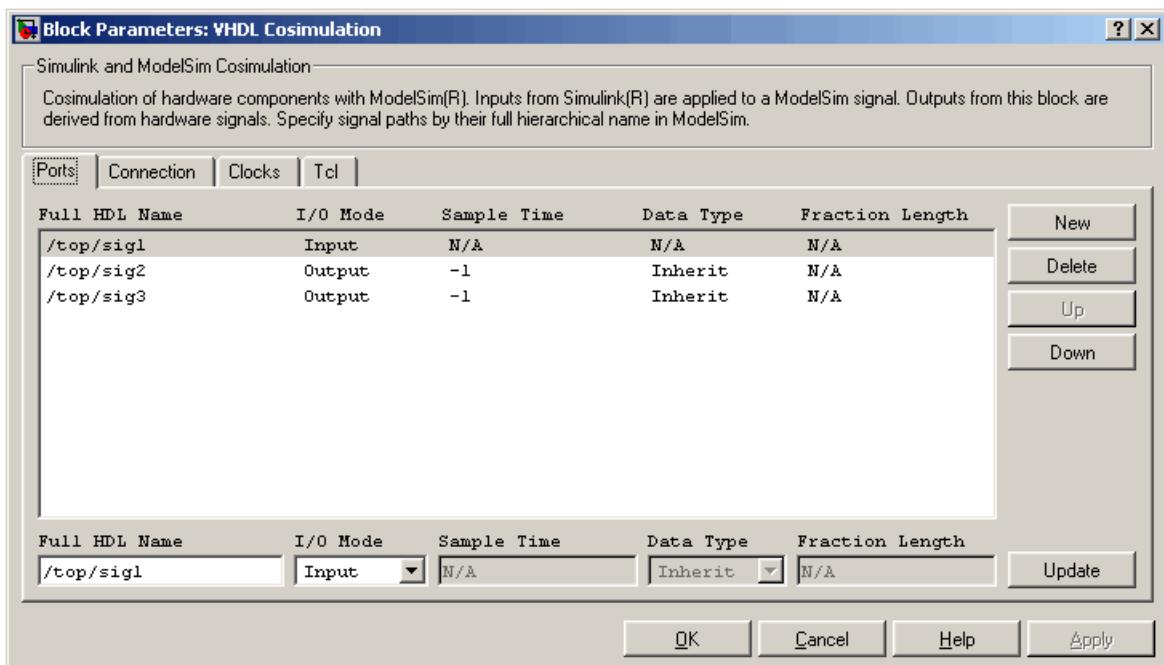

- Figure 27 :** Bloc de Co-Simulation VHDL de MATLAB.

- Figure 28 :** Bloc de Co-Simulation.

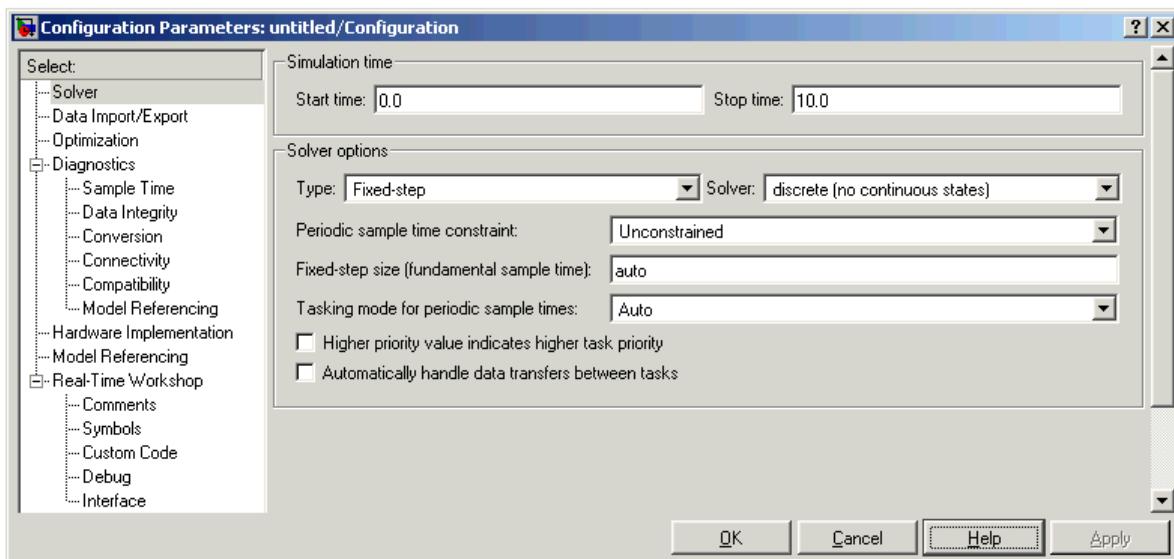

- Figure 29 :** Bloc de Configuration Paramètres de Simulation.

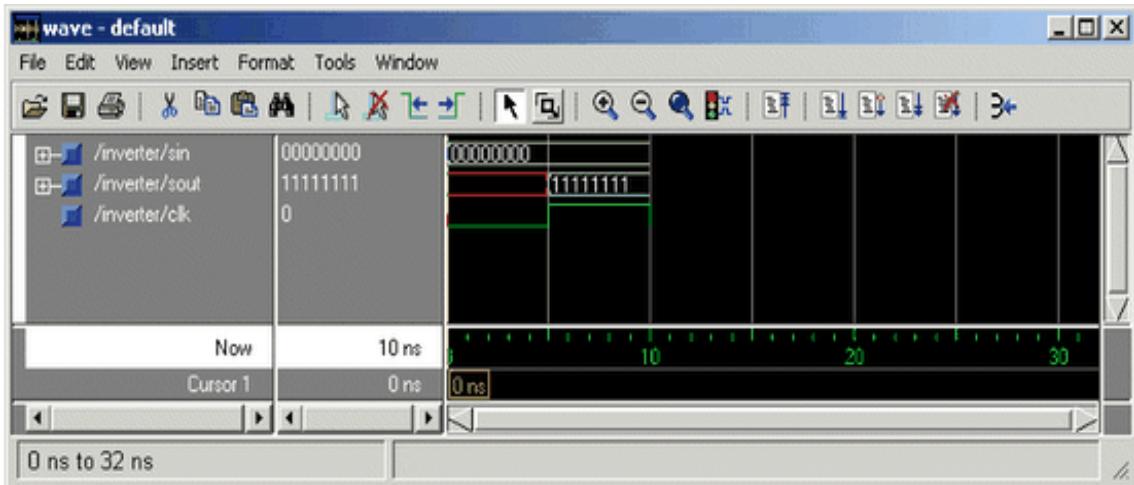

- Figure 30 :** Affichage des pots de l'algorithme a simulé dans ModelSim.

- Figure 31 :** Affichage des résultats sur ModelSim.

- Figure 32 :** ISE 7.1i de Xilinx.

- Figure 33 :** Plateforme installé.

- Figure 34 :** Installation de System Generator.

- Figure 35 :** Ajout des bibliothèques de Xilinx dans le Simulink de MATLAB.

- Figure 36 :** Exemple de Co-Simulation MATLAB/ FPGAs.

- Figure 37 :** Notre exemple pour tester la plateforme.

- Figure 38 :** Configuration du bloc de System Generator.

- Figure 39 :** Présentation des différents champs du bloc Resource Estimator.

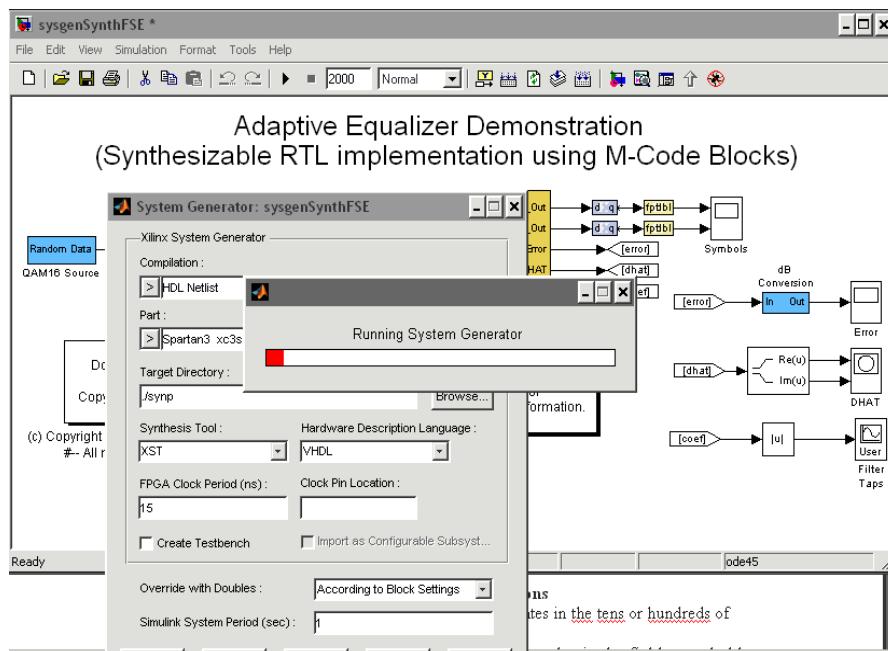

- Figure 40 :** Lancement du System Generator.

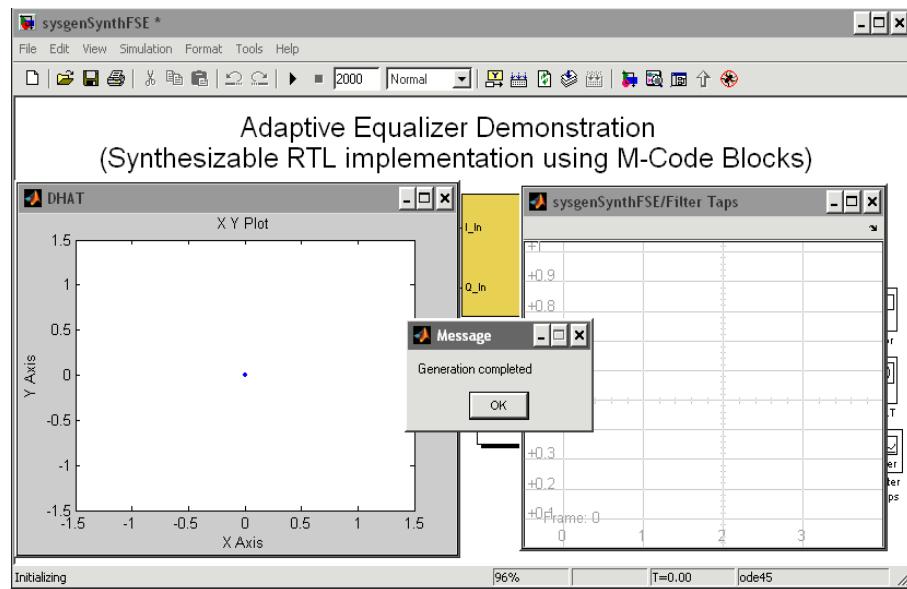

- Figure 41 :** Fin de la génération.

- Figure 42 :** Résultat de Co-Simulation.

## Liste des tableaux

**Tableau 1** : Outils de Chip Scope.

**Tableau 2** : principale information du projet.

**Tableau 3** : Tableau d'estimation de ressources.

**Tableau 4** : Plus d'informations sur le rapport produit par System Generator.

## INTRODUCTION GENERALE

Les concepteurs de systèmes modernes doivent gérer des projets associant plusieurs disciplines et plusieurs technologies. En particulier, depuis des années, les systèmes électroniques ne sont plus conçus isolément : ils intègrent des préoccupations de systèmes et de microsystèmes, dans divers secteurs d'applications scientifiques et industrielles. En raison de la complexité et de l'hétérogénéité de ces systèmes, il est nécessaire de mettre en place des méthodes et des outils facilitant l'intégration de solutions analogiques, numériques, mixtes, matérielles et logicielles. Ce problème et le besoin d'optimiser le processus de conception pour réduire le "time to market", ont conduit au développement de techniques telles que la modélisation et la validation à haut-niveau, la modélisation fonctionnelle, la réutilisation et la génération de modules de propriété intellectuelle (IP)... Ces composantes doivent être considérées dès les premières étapes de la conception. Nos propositions auront à tenir compte de nombreuses exigences, et donc à s'appuyer sur des langages et des procédures standardisés.

Les méthodes actuelles doivent aussi prendre en compte la conception coopérative et la réutilisation des acquis. Elles doivent donc être basées sur des procédures et des langages normalisés ou standardisés facilitant les échanges. Le but est alors de proposer des outils généraux et des méthodes capables de soutenir le travail coopératif entre divers participants d'un projet de conception. Dans une première étape, les méthodes utilisées doivent s'appuyer sur des modèles de haut-niveau, fonctionnels, exécutables, que nous appelons ici des Prototypes Virtuels. Ces prototypes permettent de vérifier, par simulation, leur conformité fondamentale avec le cahier des charges, avant d'entamer les démarches de matérialisation et de réalisation technologique.

Les motivations techniques, commerciales et l'influence de la concurrence créent des intérêts forts chez les industriels, dans le développement, l'utilisation et l'optimisation de technologies permettant d'arriver aussi loin que possible dans les extensions de la conception système [Ham01]. Le développement des prototypes virtuels et la nécessité de valider leur cohérence avec les spécifications, demande l'appui d'outils informatiques permettant de modéliser, dès les niveaux d'abstraction les plus élevés, les aspects suivants:

- Les interactions du système avec son environnement opérationnel.

- L'évaluation et la définition des entrées / sorties.

- L'étude et le développement des modèles comportementaux des constituants.

- La représentation graphique des relations fonctionnelles proposées.

- L'exploration architecturale.

- L'estimation des performances et les états critiques de fonctionnement.

Les exigences générales se situent au niveau de la gestion de ces aspects et de la recherche de techniques permettant de réduire le temps de développement des produits et d'accroître les performances de la conception sur des points essentiels comme la robustesse, la sûreté de fonctionnement et la vérification. Plusieurs axes de réflexion et de développement devront être explorés :

La réutilisation, autant que possible, des acquis et des modèles précédemment validés.

Dans ce contexte, l'extension de l'utilisation des outils de CAO pour l'électronique vers d'autres domaines peut représenter une source de progrès important.

L'utilisation de techniques telles que le co-design, la Co-Simulation, la création et la gestion de modules de propriété intellectuelle ont amené le monde de l'électronique numérique au sommet de ce qu'il est convenu d'appeler l'EDA (Electronic Design Automation) .

La partie analogique qui pourtant reste en retard par rapport à ces techniques à cause de la complexité du problème et de la difficulté à mettre en place une vraie politique de standardisation des méthodes, et des langages : Il n'est pas facile d'y établir une base commune de ressources informatiques et méthodologiques, à l'image de la modélisation VHDL ou de la gestion des IPs dans le domaine de l'électronique numérique.

La plus grande difficulté de l'approche est de généraliser les méthodes et de considérer la conception système comme un tout. De cette manière, en partant des spécifications ou des cahiers des charges, les concepteurs pourraient établir et valider des modèles fonctionnels et proposer des solutions architecturales. Une étape essentielle de cette problématique est la traduction ou l'interprétation des spécifications sous forme de modèles fonctionnels.

En plus, l'approche consiste à utiliser un seul langage pour la spécification complète du fonctionnement du système. Cela suppose qu'il possède une sémantique consistante et assez riche pour qu'il puisse supporter l'hétérogénéité des modules constituant le modèle entier.

L'inconvénient majeur de cette approche réside dans la difficulté de trouver un langage capable de couvrir la plupart des domaines impliqués dans les systèmes actuels. Cela amène à la

définition de nouveaux langages et par suite à des temps d'apprentissage important et à la construction de nouvelles bibliothèques.

Dans ce contexte, nous trouvons pas mal de langages et outils : pour la simulation analogique, nous avons comme exemple PSPICE. Pour la simulation mixte analogique, numérique nous trouvons principalement SABER, Verilog-AMS et VHDL-AMS. Une bonne partie des outils destinés à la conception des systèmes mixte comme Spec C et System C. Dans une autre catégorie, nous citons des outils qui abordent le problème de simulation à un niveau plus élevé que la partition logicielle /matérielle. Parmi eux, nous trouvons POLIS qui permet de créer une méthodologie formelle unifiée. Et nous terminons par des approches généralistes; il s'agit des plus célèbres outils de modélisation qui est MATLAB produit par The MathWorks. Il permet de réaliser une modélisation détaillée des algorithmes de contrôle des systèmes dans des domaines multiples.

Comme nous l'annoncions, le grand défit consiste maintenant à offrir un environnement qui ne soit pas réservé exclusivement à des experts en un seul domaine. Les spécialistes du traitement de données, habitués à manipuler le langage C/C++ ou Simulink trouveraient un intérêt certain à pouvoir accéder directement au matériel. Des bibliothèques de circuits logiques dédiées prêts à être utilisés existent déjà. Des synthétiseurs de circuits logiques, sur base de quelques paramètres, existent également et sont développés par des firmes spécialisées.

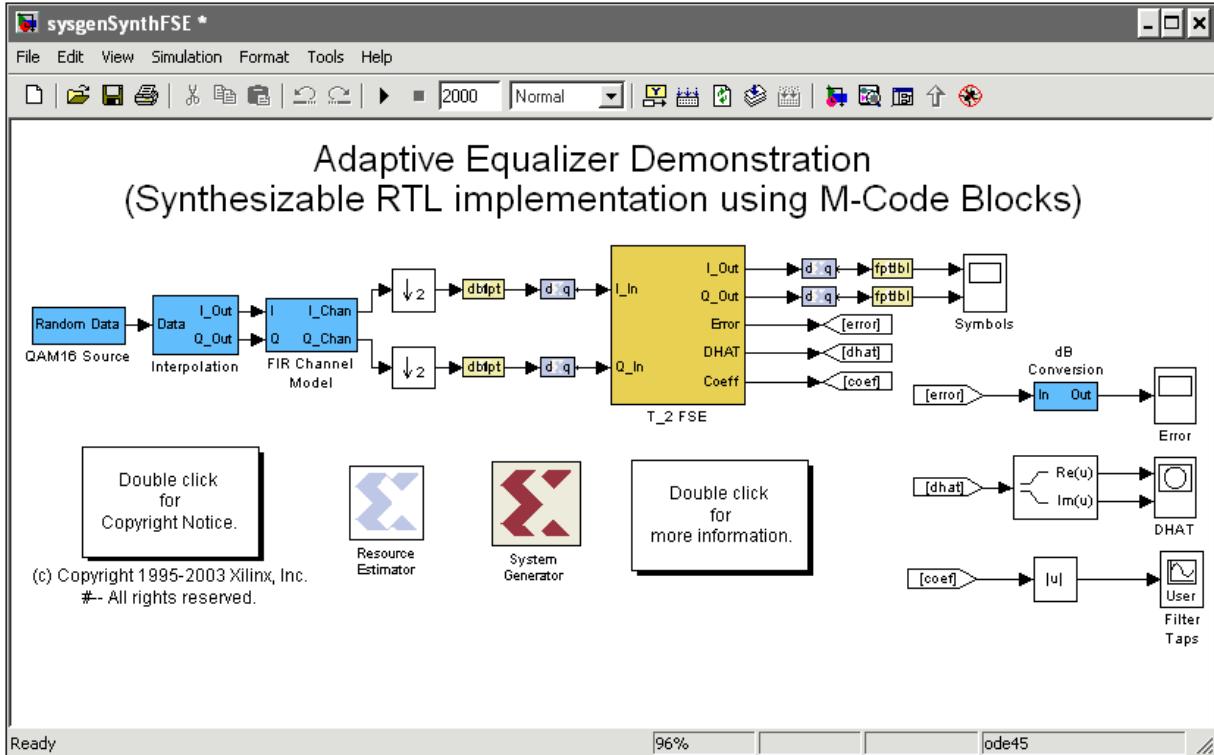

Notre objectif consiste à identifier une méthode efficace de validation fonctionnelle de système embarqué dans son environnement unifié. Il s'agit de mettre en place un environnement de Co-Simulation hétérogène. Nous présentons le travail en deux parties : la première présente la simulation MATLAB/VHDL tandis que la deuxième consiste à envisager la simulation MATLAB/FPGAs. Afin de tester les plateformes mises en place, nous avons considéré l'exemple LMS-based adaptive equalization (Synthesizable RTL implementation using M-code Block). Ce modèle montre qu'a T/2 l'adaptive FSE (Fractionally Spaced Equalizer) fonctionnant sur un point d'émission 16-QAM avec le bruit et filtrer présenté dans le modèle.

Dans le chapitre 1, nous commençons par présenter les systèmes enfouis (embarqués), nous réalisons un bilan des outils et des méthodes existantes pour la conception du système. Les outils de CAO et les méthodes de conception sont en constante évolution et leur développement reflète l'état de l'art des pratiques. Au niveau de la conception des systèmes électroniques, une fois que les différentes approches et méthodes dépassent le niveau purement théorique, et que les

langages sont adoptés, des processus de simulation et de Co-Simulation sont engagés. Au cours de cette étude, nous sommes restés attentifs aux nouveautés provenant des fournisseurs commerciaux, et aux innovations proposées par le monde académique et scientifique et nous terminons par présenter l'Approche classiques des validations logicielles.

Le chapitre 2 porte sur la mise en place des langages et des outils de notre plateforme de conception système à haut niveau. Nous détaillons les apports de chacune d'elles pour assurer la Co-Simulation.

Dans chapitre 3, nous abordons la Co-Simulation MATLAB/VHDL, nous expliquons les différentes interactions entre les logiciels formant la plateforme et nous présentons un exemple pour mieux éclaircir cette approche.

Le chapitre 4 est consacré à la Co-Simulation MATLAB/FPGAs. Nous expliquons les différentes interactions entre les logiciels formant la plateforme. Le but de cette dernière partie est de traiter complètement un cas d'application en utilisant cette approche afin d'illustrer, de la meilleure façon possible, son fonctionnement.

Enfin, nous terminons par une conclusion générale, dans laquelle nous présentons les avantages des environnements proposés dans ce mémoire.

# **LANGUAGE AND ENVIRONMENT OF SIMULATION: STATE OF THE ART**

# **Chapitre I: LANGAGE ET ENVIRONNEMENT DE SIMULATION : ETAT DE L'ART**

## **I.1 Introduction**

Les outils de CAO sont devenus des appuis incontournables pour les ingénieurs et les scientifiques, au moment d'exécuter tous types de projets, particulièrement ceux dont la complexité et le temps de développement sont importants. Nous avons conduit, pendant toute la durée du mastère, une veille technologique des outils disponibles sur le marché et des techniques émergentes des laboratoires de recherche et autres organismes universitaires. Malheureusement, nous n'avons pas eu la possibilité de tout tester et nos analyses ne pourront qu'être fortement influencées par les standards et les tendances d'utilisation au niveau de l'industrie et de la recherche.

Pour ce chapitre d'analyse, nous avons commencé par présenter les systèmes enfouis. Ensuite nous avons classé les outils selon trois champs d'application : la conception électronique en général, la conception de haut-niveau des systèmes à base d'électronique et la gestion de l'information des projets de conception système. Cela permet de prévoir les langages et les outils que nous allons utiliser pour attendre toujours notre objectif qui est en premier lieu réduire le temps de conception et utiliser un seul langage pour toute la simulation.

## **I.2 Les systèmes enfouis (embarqués)**

Afin de mieux situer le cadre des travaux présentés dans ce mémoire, il convient de définir plus précisément ce que sont les systèmes enfouis (également appelés systèmes embarqués). S'il n'existe pas de définition "officielle", il est communément admis que, d'une manière très générale, un système enfoui peut être vu comme un système électronique dont le fonctionnement repose sur un microprocesseur (avec ou sans système d'exploitation), mais qui n'est pas un ordinateur (au sens Personale Computer) [Aas 04]. Pour être plus précis, nous pouvons dire qu'un système enfoui est un système électronique dédié à une ou à un ensemble d'applications prédéfinies et dont la mise à jour ne peut être que très limitée (par exemple chargement de nouveaux logiciels ou reprogrammation de matériel reconfigurable). De plus, un système enfoui peut être éventuellement multi-domaines, c'est à dire analogique et numérique : le domaine

analogique comprenant par exemple la partie RF d'un téléphone mobile alors que le domaine numérique comprenant le traitement numérique du signal et l'interface utilisateur.

La partie numérique est souvent hétérogène, puisqu'elle fait appel à des composantes logicielles et matérielles. Nous pouvons distinguer dans cette partie les systèmes fixes et les systèmes mobiles. Pour ces derniers, la maîtrise de la consommation est un facteur essentiel à leur réussite commerciale ; c'est pour cela que la recherche sur cet aspect est très dynamique. Enfin, la puissance du calcul des systèmes enfouis peut être très variable.

Les systèmes les moins complexes intègrent de simples microprocesseurs et microcontrôleurs (de nombreux produits font appel aux 8051, 68HC05, ou autres dérivés de 68000) alors que les systèmes plus évolués font appel aux dernières générations de microprocesseurs et de DSP (Digital Signal Processor), avec aussi des accélérateurs matériels dédiés.

Comme indiqué plus haut, les systèmes enfouis sont généralement implantés sous la forme de composantes logicielles et matérielles. Les composantes logicielles peuvent être implantées sur des processeurs à usage général (GPP) ainsi que sur des processeurs à usage spécifique (DSP, ASIP). Les composantes matérielles sont implantées soit sur des composants dédiés (ASIC), soit sur des composants reprogrammables (FPGA). Il est également important de souligner les cas des systèmes sur-une-puce (SoC), qui intègrent sur une seule puce de silicium les composantes logicielles et matérielles. En effet, bon nombre de processeurs (ou cœur de processeur) sont disponibles sous la forme de "propriétés intellectuelles" (IP, spécification, à un niveau d'abstraction donné, d'un composant matériel ou logiciel, et destinée à être réutilisée par une tierce partie) synthétisables, ce qui permet de les intégrer à côté des parties matérielles, soit sur ASIC soit sur FPGA de dernière génération.

Ces derniers intègrent un nombre considérable de portes (1,5 millions pour le modèle Altera EP20K1500E en technologie 0.13 μM), des blocs de traitement du signal numérique (modules matériels de type multiplicateur, additionneur, soustracteur, accumulateur, registres pipelines) comme la famille Stratix chez Altera. On peut enfin citer les FPGA intégrant d'origines des processeurs telle la famille Virtex-II Pro (pouvant disposer de 0 à 4 processeurs de type PowerPc405).

D'où la nécessité des langages et des outils pour assurer la simulation ou la Co-Simulation des systèmes hétérogènes.

### I.3 Simulateur analogique

Nous commençons ce tour d'horizon des outils et langages d'aide à la conception des systèmes à base d'électronique par l'un des outils pionniers de la simulation purement analogique, qui, au long des années, est devenu un standard industriel et académique : **PSPICE**. Suite à l'apparition de Spice 1 en 1972 [Mal02] à l'Université de Berkeley, Pspice [Cds03a] est devenu le standard de fait pour la simulation électronique analogique. Sa version, PSpice 9.2.3 est un des modules fonctionnels d'OrCad. Le premier simulateur de PSpice a été introduit en 1985. Depuis cette date, il a été constamment mis à jour en fonction de la technologie des ressources informatiques et des systèmes d'exploitation jusqu'au point de devenir un outil universellement utilisé dans l'industrie, dans les universités et dans les laboratoires de recherche. La plupart des fabricants de composants électroniques fournissent aujourd'hui des modèles écrits en PSpice.

PSpice est un simulateur complet pour la conception analogique. Avec ses modèles internes et ses bibliothèques largement répandues et développées, dès les systèmes à haute fréquence jusqu'aux circuits intégrés de basse puissance, tout peut être simulé. Dans la bibliothèque de PSpice, des modèles peuvent être édités mais les utilisateurs peuvent également créer des modèles pour de nouveaux dispositifs à partir des fiches techniques. « PSpice A/D Basics » est un simulateur de signaux mixtes. C'est une version plus élaborée de PSpice qui peut être employée pour simuler des systèmes mixtes sans limite théorique de taille, contenant des parties analogiques et des éléments numériques.

Malheureusement, quand il s'agit de grands systèmes, les simulations deviennent trop lourdes et demandent un temps d'exécution prohibitif.

### I.4 Simulateur mixte (analogiques, numériques)

Les exigences de la technologie et du marché ont imposé le développement d'outils plus puissants capables de traiter simultanément les domaines analogiques et numériques. La plupart des systèmes électroniques actuels comportent des combinaisons de circuits analogiques et numériques. Ce besoin a entraîné depuis la fin des années 90, l'apparition de langages de description matérielle de systèmes à signaux mixtes [Coo01] MSHDLs. Ces types de langages offrent un grand intérêt dans une approche de conception système.

### I.4.1 SABER

SABER [Ham01] est un outil très utilisé, développé par la société Analogy (aujourd'hui Synopsys) et orienté vers la conception système. Il offre la possibilité de faire des simulations de signaux et technologies mixtes : analogiques et numériques, grâce à l'existence de passerelles avec d'autres outils. Les algorithmes de simulation de SABER, fournissent une capacité de convergence qui permet à l'utilisateur d'arrêter et de relancer la simulation pour regarder les résultats intermédiaires et/ou changer certains paramètres des composants sans quitter l'environnement de simulation. La liste d'analyses disponibles sur SABER inclut : l'analyse de Monte Carlo, l'analyse de sensibilité, l'analyse en fréquence, l'analyse du bruit, l'analyse de distorsion, le calcul de fonctions transfert, transformées de Fourier et simulation des tensions d'alimentation. Tous les modèles (numériques, analogiques et mixtes) de la bibliothèque SABER standard sont codés en langage MAST.

L'interface de Co-Simulation Saber/Verilog-XL [Ana01a] combine les capacités de SABER avec le simulateur pour la conception numérique Verilog-XL de Cadence Systems. Cette interface donne à SABER l'avantage de pouvoir co-simuler avec Verilog dans presque tous les principaux environnements de conception, y compris SaberSketch, des environnements de Mentor Graphics, de Cadence ou Viewlogic. La sortie de la simulation est combinée et synchronisée en temps pour afficher et corrélérer les données analogiques et numériques. L'interface de Co-Simulation de SABER/ModelSim [Ana01b] incorpore les simulateurs numériques VHDL de ModelSim.

L'interface Saber/Fusion [Ana01c] (ancienne STI) fournit un service efficace pour la simulation mixte analogique / numérique dans l'environnement de conception Powerview. Le STI combine le simulateur AHDL de SABER avec de ViewSim structural, de VHDL Speedwave et des simulateurs numériques de VCS Verilog. Le Saber/Fusion STI se combine également avec le logiciel d'intégration Framework. Le résultat est une interface graphique qui fournit la Co-Simulation rapide de circuits conçus avec de nombreux modèles composants de bibliothèque disponibles dans les simulateurs de SABER et de FUSION.

L'inconvénient majeur de Saber, est son langage propriétaire, MAST, qui ralentit sa diffusion. Dernièrement, suite au rachat de l'outil par la société Synopsys et grâce à une réaction commerciale naturelle face à la montée en puissance de VHDL-AMS, une nouvelle initiative a été

lancée. Il s'agit d'une proposition OpenMAST™ [Syn04] dont l'objectif est de faciliter l'accès au code des modèles écrits en MAST.

#### I.4.2 Verilog -AMS

Verilog-AMS [Acc98] a été créé sous la tutelle d'Accellera (Organisation de standards EDA) afin de mettre en place les extensions analogiques mixtes de Verilog (IEEE-1364). La première version était Verilog-A LRM sortie en juin 1996 puis Verilog-AMS LRM en août 1998. Le langage Verilog-AMS permet de faire la description comportementale des systèmes analogiques et mixtes.

Ainsi que VHDL-AMS (1.3.2.3), Verilog-AMS peut être applicable aux systèmes électriques et non électriques. Le langage permet de faire des descriptions de systèmes, en utilisant des concepts comme des nœuds, des branches, et des ports. Les signaux de type analogique et numérique peuvent être présents dans le même module. Au contraire de VHDL-AMS, Verilog-AMS n'est pas un standard IEEE.

#### I.4.3 VHDL-AMS

VHDL-AMS est une norme IEEE [Ieee99] (1076.1 de 1999) qui élargit la définition du VHDL pour inclure la description des systèmes analogiques mixtes. Avec VHDL-AMS les systèmes qui étaient décrits en utilisant plusieurs outils tels que MATLAB, VHDL et SPICE peuvent être tous modélisés en utilisant un seul langage.

VHDL-AMS inclut toutes les propriétés du VHDL standard, avec en plus, la capacité de décrire les systèmes mixtes, analogiques et numériques par le biais de modèles multi abstractions, multidisciplinaires, hiérarchiques à temps continu et à événements discrets [Her02]. Au niveau conception système, VHDL-AMS peut être utilisé pour faire des descriptions de haut-niveau comme la description comportementale, le RTL (Register transfert level), les fonctions de transfert avec les transformées Z et de Laplace, des convertisseurs numérique/analogique, analogique/numérique, « phase-lock-loops » comportementaux, et les filtres analogiques et numériques. En revanche, VHDL-AMS ne permet pas de résoudre ni des systèmes à équations différentielles partielles ni des descriptions de caractéristiques géométriques des systèmes.

Pour la conception électronique détaillée, VHDL-AMS permet :

- Des simulations au niveau des portes logiques.

- Des modélisations de circuits analogiques et de modèles au niveau transistor SPICE / VHDL-AMS.

- Des descriptions de systèmes par des équations simultanées, non linéaires, différentielles et algébriques.

- De la modélisation et de la simulation des effets physiques liés au fonctionnement numérique.

Dans notre démarche, VHDL-AMS présente l'avantage [Her02] de proposer un langage commun indépendant des fournisseurs et de la technologie. Du point de vue technique, il permet une haute modularité facilitant les descriptions hiérarchiques. Cependant, le langage est complexe et les premières impressions de l'utilisateur peuvent être relativement décourageantes. Cette sensation est accentuée par le fait de ne pas pouvoir compter sur le support total d'une norme récente. Actuellement, une nouvelle version est en cours de préparation. Par rapport à la synthèse, VHDL-AMS inclut tous les sous-ensembles synthétisables de VHDL pour la partie numérique. Pour la partie analogique, des premiers travaux ont été réalisés [Dob03] [Dv03].

Quelques simulateurs sont déjà disponibles sur le marché :

- AdvanceMS™ [Mg01a] ANACAD (Mentor Graphics).

- System Vision™ [Mg03] version 8.3.0 de Mentor Graphics.

- SIMPLORER® 7.0 [Ans03] développé par ANSOFT.

- SMASH™ 5.1.3 [Dg03] de DOLPHIN Integration.

- TheHDL d'AVANTI.

- Hamster [Sim03], un simulateur gratuit pour PC, de SIMEC. Cet outil a disparu mais il s'utilise encore pour guider les « premiers pas » des utilisateurs de VHDL-AMS.

- SaberHDL™ [Syn03], de chez Synopsys propose l'option d'un simulateur intégré pour la simulation mixte. Le fabricant offrira un outil capable de supporter les langages : VHDL-AMS, MAST, HSPICE et Verilog AMS. SaberHDL pourra fonctionner sur Sun Solaris 2.6.8, Windows 2000 et RedHat Linux.

En conclusion, hormis les soucis d'implémentation de la part des fabricants d'outils. L'intégration naturelle de modèles de plusieurs disciplines permet d'avoir une vraie approche système en adéquation à notre problématique générale de conception.

## I.5 La simulation matérielle / logicielle

Le co-design est l'une des techniques les plus intéressantes car elle s'efforce de mettre en place une vraie méthode de conception simultanée du matériel (100% numérique) et du logiciel. Son émergence est due à la grande et croissante ressemblance de la conception des systèmes numériques avec la conception du logiciel. L'objet du co-design [Dmg97] est de réaliser les objectifs de la conception au niveau système en regroupant et exploitant la synergie du matériel et du logiciel par le biais d'une conception concourante. Voici quelques exemples d'outils conçus pour le co-design.

### I.5.1 La conception basée sur le langage C

Une bonne partie des outils destinés à la conception de systèmes mixtes numériques utilisent l'approche « C-Based System design », c'est-à-dire, les systèmes sont écrits sous la forme du code C ou C++. Nous commençons notre analyse avec SpecC :

- **SpecC** : Créé à l'Université de Californie Irvine par l'équipe de travail du professeur Daniel Gajski au CADLAB, SpecC [Dgg01] est plus une extension ou une adaptation du C, il est un langage de co-design «hardware/software» basé sur le langage C et proposé par UCI CADLAB. C'est une version élaborée d'ANSI-C dont le niveau d'abstraction le plus haut est décrit à base de machines à états finis. SpecC propose des spécifications comme canaux de communication, des représentations hiérarchiques, de la simultanéité et de l'abstraction de la synchronisation. Il est conçu pour être un langage unique qui peut être utilisé dans toutes les étapes du processus de co-design matérielle / logicielle. Un projet SpecC se compose d'un ensemble de déclarations comportementales, déclarations de canaux et d'interfaces. Un comportement est une classe avec un ensemble de ports : L'ensemble des comportements secondaires, l'ensemble des canaux, l'ensemble des variables et des fonctions « privées » et une fonction principale« publique ». Par ses ports, un comportement peut être relié à d'autres comportements ou canaux afin de communiquer. La fonctionnalité d'un comportement est indiquée par ses déclarations de fonction. Un canal est une classe qui contient la transmission. Il se compose d'un ensemble de variables et de fonctions appelées méthodes, qui définissent un protocole de communication. La version SpecC 2.0 a été développée par l'équipe du professeur

Masahiro FUJITA, à l'Université de Tokyo. Elle intègre des améliorations dans la gestion des événements concurrents, des interruptions, et du parallélisme. Il est intéressant de noter que récemment l'équipe du professeur FUJITA a été contactée par des concepteurs de satellites japonais qui veulent aborder la conception des micro-systèmes embarqués du point de vue système. Pour l'instant, SpecC ne comporte pas d'options pour la conception analogique et mixte. Le groupe du travail pour la version 3 a été lancé à Tokyo le 8 octobre 2002. Il étudie la faisabilité d'une extension analogique du langage. A notre avis, il reste encore du travail pour arriver à un langage système général. Le développement de l'outil a été pénalisé par la grande partie de marché couverte par son grand concurrent System C.

- **System C :** Peut être le plus utilisé des approches « C based ». Les origines de System C remontent au milieu des années 90, dans les travaux de l'Université de California Irvine et du groupe Synopsys. Le premier produit était appelé « Scenic » puis « Fridge ». La première version System C 0.9 est sortie en 1999 avec l'incorporation des éléments récupérés de N2C –Coware.

System C est un ensemble de bibliothèques créées en langage C++, permettant de faire la description d'un système logicielle / matérielle par le biais de spécifications exécutables et de plusieurs niveaux d'abstraction pour un même système. System C fournit la possibilité de créer des modules, processus fonctionnels et portes logiques. Le compilateur Co-Centric SystemC synthétise la description « hardware » écrit en System C au niveau des portes logiques (gate-level netlist) ou en Verilog ou VHDL pour faire de la synthèse sur des FPGAs. Les modèles System C sont écrits sur le formalisme des FSM « Finite State Machines ».

| Fabriquant          | Outil                                   |

|---------------------|-----------------------------------------|

| Axys Design         | MaxCore developer Suite                 |

| Axys Design         | MaxSim                                  |

| Cadence             | SPW                                     |

| CoFluent Studio     | CoFluent Design                         |

| CoWare              | CoWare N2C Design System                |

| Forte Design System | Cynlib Tool Suite                       |

| Innoveda            | Visual Elite-Architect                  |

| Mentor Graphics     | Vstation TBX                            |

| Synopsys            | CoCentrics System Studio                |

| Synopsys            | SCC Synopsys Cocentric SystemC compiler |

| Veritools           | SuperC                                  |

| Virtio              | Virtual Prototyping to SystemC          |

| WHDL Language       | Rule Checker & Rule Generator           |

**Figure 1 :** Quelques outils qui supportent System C.

Cette approche très intéressante est devenue l'une des standards du fait pour la conception et la synthèse de systèmes numériques mixtes matériels et logiciels. Tel que l'illustre la Figure 1, la plupart des fabricants d'outils CAO proposent System C parmi leurs produits. Une initiative commence à prendre de l'ampleur ; il s'agit d'étendre l'utilisation du System C aux systèmes électroniques mixtes matériels et logiciels. Des travaux de mise en forme d'une proposition System C-AMS a été proposés par [Gev04]. L'approche système préconisée est intéressante car elle peut représenter une alternative pour le traitement des systèmes avec tout type de composantes : Analogiques, numériques et logicielles.

- **Handel-C** [Cel02] est un langage écrit sur la base d'ISO/ANSI-C destiné à l'implémentation d'algorithmes sur « hardware », à l'exploration architecturale et au co-design. Handel-C permet la conception de matériel en utilisant des méthodes de conception de logiciel élargies avec des particularités pour le développement de matériel. Elles incluent des largeurs variables des structures (vecteurs) de données, le traitement parallèle des communications et des événements. Handel-C n'utilise pas de machines à états finis, grâce à une méthode propriétaire de description des écoulements périodiques et parallèles.

Les modèles Handel-C peuvent être insérés dans une méthodologie de réutilisation car des fonctions peuvent être compilées dans des bibliothèques et être employées dans d'autres projets. Des noyaux écrits sous Handel-C peuvent être exportés comme boîtes noires d'EDIF, de VHDL ou de Verilog pour leur réutilisation.

D'après le fabricant, Celoxica, les points forts de Handel-C sont :

- Un langage de haut-niveau basé sur ISO/ANSI-C pour l'exécution des algorithmes sur « hardware ».

- Le langage ne demande pas de grands investissements en temps de formation des utilisateurs.

- Handel-C permet de faire des appels directs sur des fonctions externes écrits sous C/C++ et vice-versa.

- Des extensions spécifiques pour le matériel incluant la gestion du parallélisme et des communications.

- Construction des noyaux spécifiques pour la suite Celoxica DX.

Nous trouvons intéressante la compatibilité de l'outil et l'utilisation de leur propre modèle de représentation des états des systèmes ; mais il est trop focalisé sur la réalisation matérielle. Il manque la généralité requise par notre approche.

• **N2C** [Cow01] a été développé par la société CoWare. Cet outil permet de capturer les spécifications d'un système numérique dans un modèle exécutable et implantable à partir de langage C/C++. Avec N2C, l'utilisateur peut faire une spécification concourante, visant deux objectifs :

- Une implémentation et vérification de matériel et logiciel embarqué spécifique à l'application.

- L'évaluation et l'intégration de la propriété intellectuelle (IP) de matériel et de logiciel vers des nouveaux produits ou dérivés.

CoWare N2C est conçu pour co-exister avec la plupart des outils commerciaux : Simulateurs de HDL, simulateurs de positionnement d'instruction (ISS), outils intégrés de l'environnement de développement de logiciel (IDE), et des systèmes d'exploitation temps réel. Les outils de synthèse reçoivent la sortie de N2C pour démarrer la déclinaison et synthèse du système. Une version universitaire de N2C est disponible pour les membres d'Europractice Software Service [Eur04].

### I.5.2 Les outils de haut-niveau

Dans une autre catégorie, nous citons des outils qui abordent le problème du co-design à un niveau plus élevé que la partition logicielle/matérielle. Parmi eux, le projet **POLIS** [Clo01] de l’Université de Californie Berkeley qui a été développé afin de créer une méthodologie formelle unifiée pour la modélisation complète des systèmes embarqués. Cette méthodologie inclue la partition matérielle/logicielle, la synthèse automatique et la vérification. POLIS a été développé sur le modèle de calcul formel CFSM ou « Co-design Finite State Machine ». Il est un logiciel expérimental.

Bien qu'il ait été testé sur plusieurs exemples de dimension industrielle [Fl1+98] [San96], il ne peut être applicable qu'à certains domaines spécifiques. *Eaglei* [Syn00] est un outil pour la co-vérification Logicielle/Matérielle depuis la post-partition jusqu'au prototype physique. *Eaglei* supporte des outils EDA de haut rendement, la simulation cycle à cycle, les accélérateurs de matériel et l'émulation de matériel pour la conception multiprocesseur. Avec *Eaglei*, il est possible de distribuer la simulation à travers un réseau pour améliorer la vitesse de simulation. Il fournit une plate-forme d'interopérabilité UNIX/PC. Cette caractéristique peut le rendre intéressant pour son intégration dans des plates-formes de conception.

*Seamless CVE* [MG00a] est un outil de Mentor Graphics pour la conception électronique. Grâce à son interface « Plug-In » (SPI), il est capable de réaliser la simulation multiprocesseur. *Seamless CVE* est compatible avec plusieurs outils de vérification et description [Mg00b] comme ModelSim VHDL, Verilog XL, VSC et avec plus de 70 microprocesseurs des différents fournisseurs.

A cause de l'exécution du modèle complet d'un microprocesseur, la vitesse du simulateur peut être six ou sept fois plus lente que l'exécution temps réel. *Seamless CVE* accélère la Co-Simulation grâce à la séparation fonctionnelle du microprocesseur de son interface électronique. La suppression selective de certains cycles dans la simulation matérielle est facultative. Les simulations matérielles et logicielles sont divisées en un simulateur d'instructions ou «Instructions Set Simulator » et un modèle d'interface ou « Bus Interface Model » pour le comportement électronique des entrées/sorties du processeur. L'arbitrage entre l'exécution des simulations est réalisé par le « Co-Simulation Kernel ».

Nous trouvons que cet outil demande de connaître préalablement l'architecture du système et donc il est utile seulement lorsque les choix de conception ont été réalisés. Nous le classons

dans la catégorie d'outils système car il permet de vérifier le fonctionnement complet de l'application.

L'outil **Co-Fluent Studio SDE**, proposé récemment par la société Co-Fluent Design. Il est orienté vers la conception de systèmes électroniques numériques comportant des implémentations matérielles et logicielles. Les origines de ce logiciel se trouvent à l'Ecole Polytechnique de Nantes sous la direction de Jean-Paul CALVEZ. Le principe d'utilisation [Per04] est de distinguer clairement les représentations fonctionnelles et architecturales du système à concevoir. En effet, l'outil permet de réaliser ces descriptions indépendamment. Trois niveaux d'abstraction ont été identifiés pour l'analyse des performances :

- Le niveau Système.

- Le niveau composant.

- Le niveau des communications entre composants.

La Méthodologie de Conception de Systèmes Electroniques [Cof03] (MCSE ou CoMES en anglais) est utilisée avec l'outil afin de gérer les différents niveaux de complexité d'un projet de conception.

La description finale du comportement des systèmes est générée sous deux formes automatiques de code. La première, destinée à la modélisation Système en C/C++, la deuxième en VHDL synthétisable orientée à l'implémentation des systèmes sous la forme de circuits intégrés. Nous trouvons cet outil particulièrement intéressant car il propose une approche générale pour la conception de haut niveau du domaine électronique, en considérant la modélisation du comportement des systèmes avec des modèles formels de calcul, de plus une issue vers la matérialisation est proposée. Dans de futurs travaux, il sera convenable d'approfondir cette démarche afin d'envisager des ouvertures vers une généralisation orientée VHDL-AMS donnant la possibilité de gérer des projets pluridisciplinaires.

## I.6 Les méthodes pour la conception logicielle

Nous continuons maintenant avec les méthodes pour la conception logicielle. Ces méthodes ont été pionnières dont la façon d'aborder le problème de la conception. En effet, les approches de la conception logicielle ont fait émerger des nombreux concepts également intéressants pour la conception amont.

### I.6.1 SADT et SA/RT des méthodologies à l'origine de la réflexion système

Nous trouvons dans la seconde moitié du siècle dernier où la complexité croissante des systèmes avait déjà demandé des efforts des scientifiques et des ingénieurs pour l'établissement d'outils et/ou des méthodes permettant d'alléger la tâche de spécification et de conception de ces systèmes. Parmi ces premiers travaux, ROSS avec SADT [Ros72] est une des pionniers dans la recherche d'une solution au problème de la spécification et de la conception des systèmes à haut-niveau. Développée à partir de 1972, cette approche avait pour objectifs de couvrir l'analyse de besoins, la spécification, la conception et la documentation en facilitant le partage de l'information entre les utilisateurs. Le modèle utilisé propose une description en blocs (d'activités ou de données) relié par quatre types de liens : Entrée, sortie, contrôle et mécanisme. Les blocs SADT peuvent être décomposés en niveaux hiérarchiques. L'approche propose deux formes possibles de diagrammes : Les « actigrams » et les « datagrams » qui représentent deux vues différentes d'un même système. L'utilisation de SADT été basée sur des principes de délimitation du contexte du système et de la limitation de taille de l'information. Les décompositions étaient limitées à sept blocs  $\pm 2$  (plus ou moins deux) par feuille. Cette approche simple et compréhensible n'est pas exclusive à un métier spécifique. Un banquier, un fonctionnaire,... peuvent lire un diagramme de leur domaine sans connaître la méthode. Efficace en spécification des exigences, elle présente un certain nombre d'inconvénients dès que des phases de conception sont abordées notamment ses insuffisances pour l'expression des algorithmes de contrôle.

D'un autre côté, SA/RT (Structured Analysis with Real-time-Extensions) [Wm85] propose, à partir d'une analyse établie sur une représentation graphique, une modélisation système dans laquelle deux facettes sont clairement différenciables : un modèle du processus statique qui lui est attaché, et un modèle de contrôle dynamique qui en permettra l'utilisation. L'originalité de cette méthode est la prise en compte de l'aspect dynamique du système. SA/RT est donc bien adapté aux applications temps réel à fort comportement dynamique.

### I.6.2 UML : le langage unifié de modélisation

UML est un langage qui émerge comme un standard de fait pour la conception de systèmes logiciels à haut-niveau, il a été proposé par l'OMG [Omg03] en 1997, avec comme objectif quatre activités principales [Bro03] du processus de conception :

- Une description du système selon plusieurs points de vue.

- La spécification des besoins et de la mise en œuvre.

- La visualisation pour faciliter la compréhension et la communication parmi les partenaires de la conception avant la réalisation du système.

- La représentation de systèmes complexes.

- La documentation de la totalité du projet, dès les spécifications jusqu'aux tests de fonctionnement.

L’application d’UML exige l’adoption d’une méthodologie claire et l’utilisation d’un bon outil logiciel mettant en œuvre le langage. Malgré cette volonté d’unification, UML n’est pas une solution totale pour la conception système, car elle n’établie pas la façon dont les diagrammes doivent être employés et moins encore un principe d’intégration ou d’interopérabilité entre eux. L’utilisation du langage perd beaucoup d’efficacité sans une méthodologie et sans le support d’un outil.

Dans le langage UML, plusieurs types de représentations graphiques [Mil03] sont possibles. Cinq modèles de représentation (chacun avec un ou plusieurs types de diagrammes) conforment la sémantique UML 1.5, à savoir :

Modèle d’utilisateur :

- « Use case diagrams » : ces diagrammes représentent le fonctionnement du système du point de vue d’un observateur externe. Leur but est de montrer ce que le système fait sans détailler le « comment ».

Modèle structurel :

- Diagrammes de classes : ces diagrammes décrivent les états statiques du système et leurs connexions.

- Diagrammes à objets : il s’agit d’une simplification des diagrammes de classes. Ces diagrammes décrivent les objets avec leurs interactions.

Modèle comportemental :

- Diagrammes de séquence : il s’agit de diagrammes d’interaction qui montrent le séquencement des opérations du système. C’est une vue temporelle.

- Diagrammes de collaboration : Ces diagrammes d'interaction comportent la même information que les diagrammes de séquence mais se focalisent sur les rôles au lieu des temps.

- Diagrammes à états et leurs extensions les « Statechart diagrams » : ils illustrent les états possibles du système et les transitions qui provoquent les changements des états.

- Diagrammes d'activités : Il s'agit essentiellement de « flowcharts ».

Modèle d'implémentation :

- Diagrammes de composants : ces diagrammes représentent l'équivalent matériel et ou logiciel des diagrammes de classes.

Modèle d'environnement :

- Diagrammes de déploiement : Ce dernier type de diagramme illustre les configurations physiques du matériel et du logiciel.

D'une façon générale, ces outils permettent de décrire les nœuds de distribution et leurs interactions dans le cas de systèmes distribués. Hormis l'approche objet, l'avantage majeur du langage UML est la multiplicité de diagrammes qu'il offre. Il permet au concepteur de créer différentes représentations du fonctionnement du système.

## I.7 Autres approches métiers et mixtes

D'autres approches ont essayé de se hisser à un niveau plus amont pour aborder le problème de la conception système. Ici, nous avons identifié deux volets : d'un part, les outils issus des initiatives des communautés indépendantes d'aborder le « haut-niveau » relatif à leur domaine, tels que l'automatique, le logiciel et l'électronique. D'autre part, les initiatives récentes qui « joignent » la conception système avec des approches généralistes et hétérogènes.

La communauté des automaticiens utilise depuis des années **Matlab®** et **Simulink®** comme leurs outils de base pour le calcul scientifique. Il s'agit, peut-être des plus célèbres outils de modélisation mathématique globale, Matlab® et Simulink® de chez **MathWorks**. Il dispose en 2004 des versions 7 et 6 respectivement. Traditionnellement, ils sont utilisés pour faire de la modélisation générale de systèmes par des fonctions de transfert, avec une forte orientation vers les systèmes de contrôle et commande. Ils permettent de réaliser une modélisation détaillée des

algorithmes de contrôle des systèmes dans des domaines multiples. Les versions actuelles comportent plusieurs « toolboxes » permettant de participer à la conception système à différents niveaux. Parmi les applications les plus intéressantes, nous trouvons l'utilisation de Matlab®/Simulink® en combinaison avec des outils VHDL pour réaliser le test de modèles pour leur implémentation matérielle. Le lien de Co-Simulation avec ModelSim®1.1 [Tmw03] permet de co-simuler et de vérifier du VHDL et du Verilog.

Cet outil permet de réaliser des vecteurs de test « logiciels » en intégrant les solutions HDL avec les algorithmes, ceci permet de vérifier le fonctionnement du HDL par rapport au modèle original ainsi que de donner des caractéristiques comportementales aux « testbench ». Ce principe est aussi répandu pour réaliser des essais de type « hardware in the loop », décrits de façon plus détaillée par [Gom01].

Parmi les offres de **MathWorks** nous trouvons des applications pour la spécification et la modélisation des systèmes automobiles [Tmw04a], la conception électronique mixte et la modélisation des composants. Ils proposent aussi des solutions pour la conception des systèmes embarqués [Tmw04b] et de certaines applications aérospatiales, notamment [Tmw04c] pour la conception des systèmes de commande et la validation de leurs interfaces homme/machine, la modélisation des systèmes mécaniques, des sources d'énergie et pour la modélisation détaillée de l'environnement de l'appareil en considérant des aspects tels que le vent et la gravité.

Dans la mesure où les outils de simulation progressent, nous pourrons envisager des modélisations couplées VHDL/MATLAB dans les quelles les équipes de conception pourront combiner leurs « savoir-faire » en matière de systèmes de commande sous MATLAB, pour élaborer des « testbenches », pour vérifier les modèles écrits en VHDL-AMS ou bien pour modéliser et synthétiser des lois de commande incluses dans ces systèmes.

Du côté informatique, de nombreux outils ont été proposés : Esterel Technologies a créé **Esterel Studio** [Dd00], pour la spécification et le développement des systèmes numériques et logiciels temps réel en utilisant la représentation hiérarchique graphique SyncCharts, donc, une notation graphique conçue par Charles ANDRE [And96] à l'Université de Nice Sophia-Antipolis. Le langage de programmation synchrone et son compilateur ont été conçus à Ecole des Mines de Paris et à l'INRIAi. Les travaux de recherche [Cla01] sur le langage, pour la plupart d'origine française, sont à la base de la création, en avril 2000, de la société d'Esterel Technologies SA.

L'approche synchrone d'Esterel studio pour la modélisation et la programmation a été retenue afin d'éviter les erreurs et les difficultés propres de la conception de ce type de systèmes, par le biais de méthodes traditionnelles. Esterel Studio utilise une sémantique de type FSM (Finite State Machine) très pure, idéale pour concevoir des systèmes indépendants de l'implémentation et dominés par des commandes.

## I.8 Approche classique de la validation logicielle

Le flot de conception classique de circuits intégré propose une étape de validation complète du logiciel embarqué, apparaissant relativement tard dans le processus du développement. Notamment, un modèle matériel du processeur dédié doit être développé et validé. Cette section présente successivement le flot de conception classique dans lequel s'insère la validation logicielle, puis décrit l'interfaçage entre le matériel et le logiciel, et enfin identifie les limites de son utilisation dans le cas de systèmes complexes.

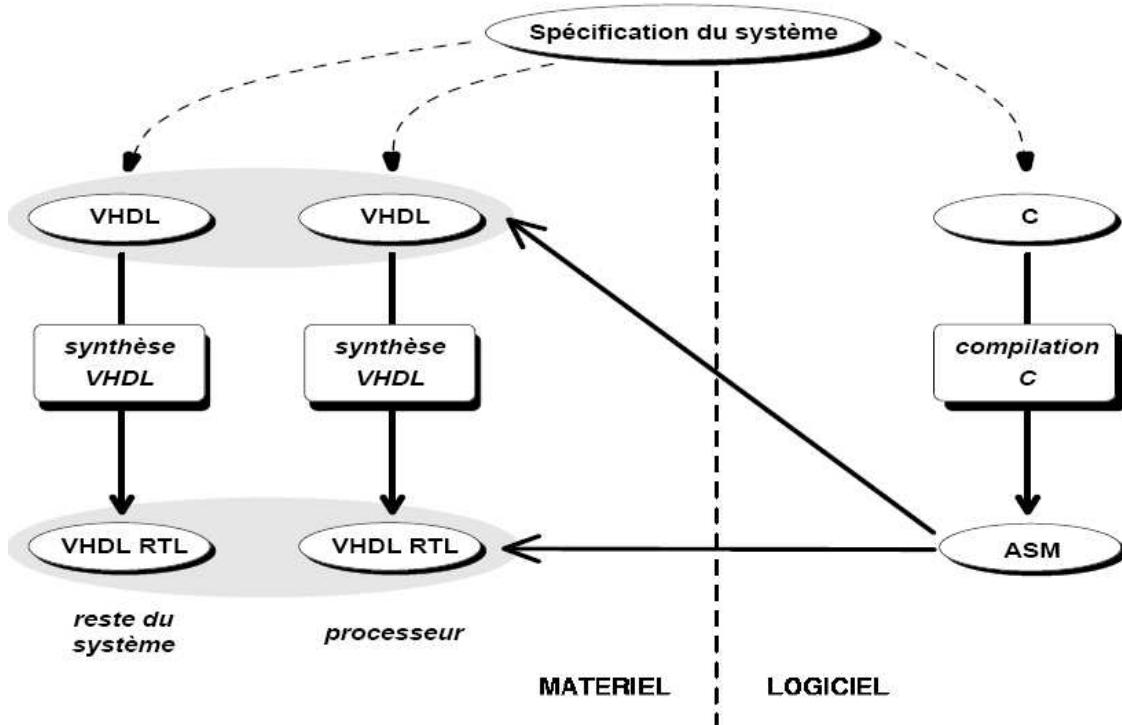

La figure 2 représente le flot de conception classique d'un système contenant un processeur et son logiciel embarqué. A partir des spécifications complètes du système, les descriptions de haut niveau des parties matérielles et logicielles sont produites (manuellement dans le cas général). Pour la partie matérielle, un langage tel que VHDL ou VERILOG est le plus souvent utilisé. Nous nous restreignons ici au langage VHDL, couramment utilisé en Europe. La partie logicielle utilise un flot de compilation C, relativement classique.

**Figure 2 :** Flow de conception classique.

La partie matérielle (à gauche) est constituée de deux parties : un processeur embarqué pour simplifier, nous ne considérons qu'un seul processeur et le reste du système constituer d'un ensemble de blocs matériels divers. Nous représentons ici un flot de synthèse comportementale du matériel, générant des modèles VHDL-RTL à partir de modèles comportementaux VHDL.

Le logiciel écrit en C (à droite) est compilé en code assembleur (ASM), par un compilateur développé spécialement pour ce processeur. Ce code assembleur, sous sa forme binaire, est ensuite chargé dans la mémoire programme du modèle VHDL du processeur (comportemental ou RTL), lequel est simulé conjointement avec le reste du système par un unique simulateur VHDL. Cette simulation est appelée simulation au niveau assembleur. Grâce à l'exactitude temporelle des simulations VHDL, la validation du logiciel embarqué atteint un niveau de précision au cycle près [Hag 93]. Le prix à payer est une vitesse de simulation relativement faible, puisqu'elle ne dépasse pas quelques instructions par seconde pour un seul processeur [Mei 97].

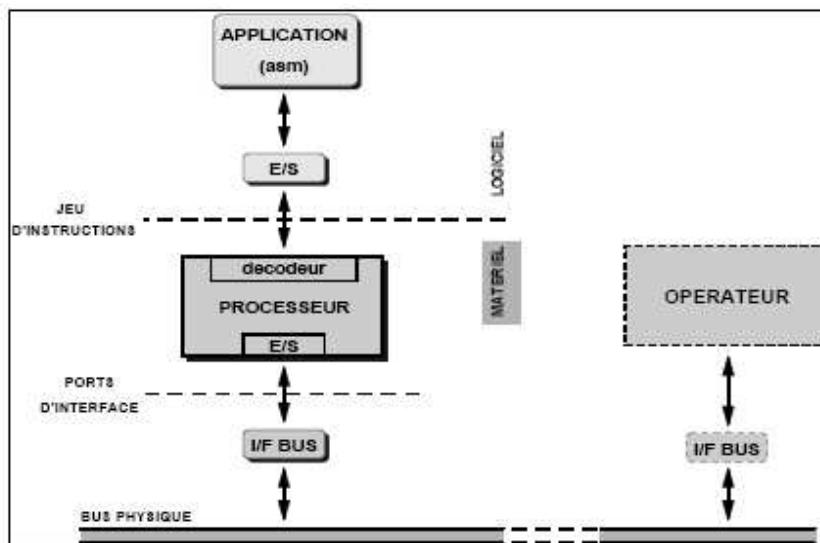

L'interface entre le logiciel et le matériel se situe entre le logiciel applicatif et le processeur, et plus précisément entre les instructions en code machine et le décodeur d'instructions figure 3.

Le code assembleur (ou code machine) de l'application, comprenant également les entrées/sorties avec le reste du système, est directement traité par le décodeur du processeur. Les opérations d'entrée/sortie destinées au reste du système sont transmises à l'interface bus, via le bloc d'entrée/sortie du processeur. L'interface bus gère la transmission des données et signaux de contrôle sur le bus physique, partagé avec les autres opérateurs du système. L'interface matérielle -logicielle est donc entièrement définie par le jeu d'instructions du processeur.

Nous distinguons deux types de validations : la validation fonctionnelle et la validation temporelle. La première vise simplement à valider le comportement du logiciel, communiquant éventuellement avec le reste du système. La seconde s'attache à vérifier que les différents signaux de contrôle et données sont traités dans un intervalle de temps compatible avec les exigences de performances, et qu'ils sont disponibles à la date prévue.

**Figure 3 :** Interface logiciel-matériel en simulation VHDL.

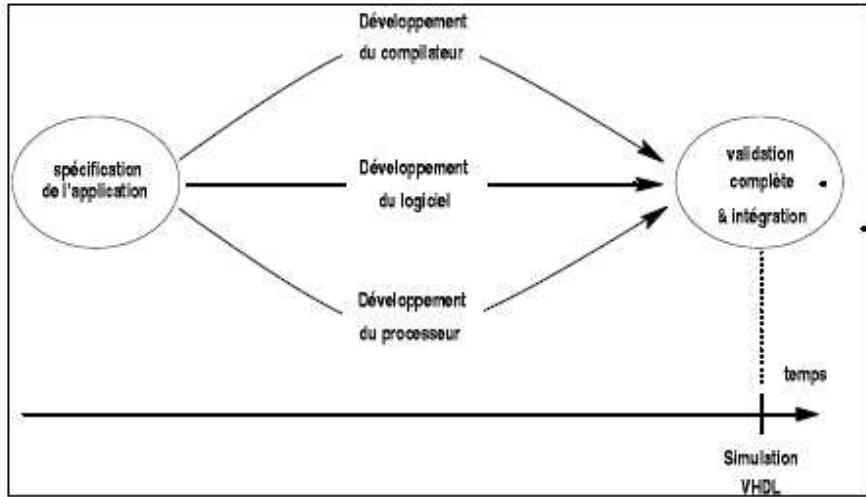

Cette approche de validation présente un inconvénient majeur : la simulation du logiciel avec le matériel intervient tard dans le flot de développement. La figure 4 représente les étapes nécessaires pour aboutir à la validation du logiciel embarqué.

**Figure 4 :** Étapes pour la validation du logiciel dans un flot classique.

Le logiciel doit évidemment être développé (en C), de même que le compilateur complet (comprenant au minimum le générateur de code, l'assembleur et l'éditeur de liens) doit être développé et validé. De plus, le processeur lui-même doit être disponible, et donc ses spécifications figées (interface et jeu d'instructions). Il est remarquable que plus la validation intervient tôt dans la conception d'un système, plus une erreur est corrigée rapidement (voir figure 5) [Cal 95].

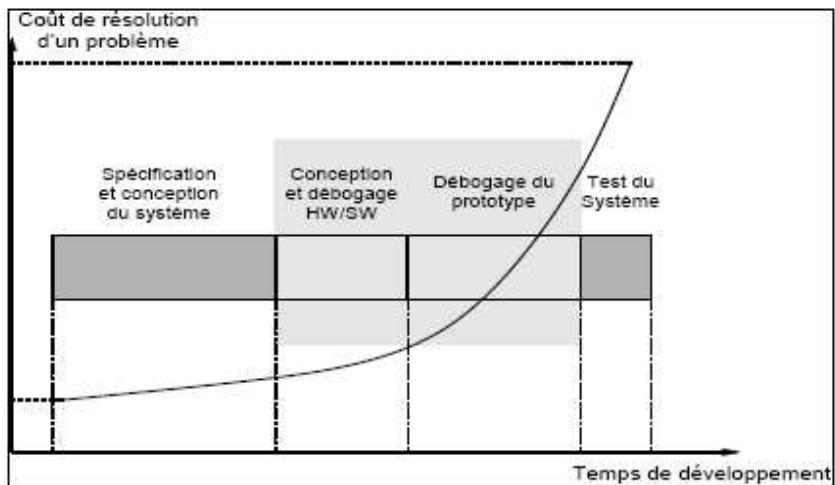

**Figure 5 :** Temps de conception et coût de débogage.

Dans ce contexte, la moindre modification des spécifications (processeur, interface, jeu d'instructions) implique la régénération du modèle du processeur ainsi que le compilateur. Le temps du cycle est alors trop long pour espérer explorer plusieurs solutions [Ver 94] [Bol 97].

## I.9 Outils existants

Comme nous venons de le voir, les systèmes enfouis font appel à des architectures hétérogènes logicielles/matérielles [Aas 04]. Afin de concevoir de tels systèmes, les méthodes de conception conjointe logicielle/matérielle sont utilisées. Elles permettent de définir les sous-ensembles du système à intégrer et d'effectuer leur partitionnement sur les cibles logicielles et matérielles. Cependant, la complexité sans cesse grandissante de ces systèmes et les diverses contraintes auxquelles doivent faire face les concepteurs, font qu'il est nécessaire de faire appel à des nouvelles langages et outils, ce que nous allons montrer maintenant. Afin d'assurer le succès commercial de tels systèmes il est primordial que ceux-ci répondent aux attentes des consommateurs parmi les quelles nous pouvons citer : le délai de mise sur le marché (time-to-market) des nouvelles générations de produits, nouvelles fonctionnalités, petite taille, poids léger, faible consommation en énergie, simplicité d'utilisation et bien sûr coût acceptable. Les outils sont arrivés à un degré de maturité assez important restent cependant trop lents et ne permettent donc pas d'explorer, dans des délais raisonnables, les gigantesques espaces de conception inhérents aux systèmes actuels. Nous allons citer ainsi l'outil Design Trotter et plus particulièrement le module d'estimation système qui permet l'exploration rapide des fonctions complètes décrites en langage de haut de niveau (actuellement le langage C). Le résultat obtenu grâce à la méthode proposée, est aidé le concepteur lors de la phase initiale de la conception d'un système mais il reste limiter sur un nombre d'application et peut contenir des fautes. Le concepteur peut avoir une approche plutôt logicielle (approche "informatique", exemple : C) ou plutôt matérielle (approche "électronique", exemple : VHDL). Le choix du langage de spécification qu'il utilise est d'ailleurs souvent guidé par le type d'approche auquel il est habitué. Ensuite, il existe plusieurs algorithmes pour décrire un même traitement, quelque soit le langage choisi. C'est surtout ce deuxième point qu'il serait intéressant d'intégrer à cette méthodologie et à l'outil Design Trotter.

Et pour le plus récent, nous trouvons l'outil proposé par M. Juan-Carlos Hamon qui est HileS .l'outil HiLeS Designer 0 est arrivé au stade opérationnel [Moc05]: il est en version 0V6. Il s'agit d'un outil de conception amont permettant de représenter les spécifications d'un produit en un modèle formel basé sur les Réseaux de Pétri et le langage VHDL-AMS. Ce modèle permet par une relation à l'outil TINA une certaine vérification des spécifications et la validation d'une

architecture temporisée du système sous la forme de blocs fonctionnels interconnectés. L'outil est encore faible en matière de vérification. Le premier exemple, le calculateur ECP, a permis de tester la première version de cet outil dans un environnement industriel. Un certain nombre de limites sont apparues pour lesquelles ils ont fait des propositions de nouveaux développements :

- Lecture de spécifications avec un guide d'interprétation. Ce dernier projet nous a permis d'envisager le rôle de UML dans notre démarche ainsi que de profiter de l'importante avis de l'expert sur la construction de la modélisation HiLeS.

- La mise en place des observateurs définis par l'utilisateur.

- L'amélioration des interfaces avec des outils de simulation VHDL-AMS. Pour incrémenter la flexibilité de HiLeS Designer.

- L'utilisation ou la proposition d'une méthode facilitant l'écriture du code VHDL-AMS associé aux blocs fonctionnels HiLeS.

## I.10 Conclusion

Ce premier chapitre définit tout d'abord le domaine de la conception dans un contexte où l'innovation ne provient plus seulement des nouveautés en termes de matériaux ou de technologies :

La conception et la simulation des systèmes électroniques ont été un argument fort de motivation pour le développement d'outils, de méthodes et langages permettant de gérer la complexité croissante des circuits et des systèmes. La CAO électronique, prise en compte à tous ses niveaux, industriel, académique et recherche, est devenue un moteur incontournable d'innovation et de développement d'outils dédiés à la conception. Les objectifs sont toujours les mêmes, réduire le temps de production « time to market », anticiper les possibles sources d'erreur, réduire les coûts de fabrication, réaliser des prototypes virtuels les plus représentatifs de la réalité et en général, réaliser la conception sans faute.

Malgré, le haut degré de spécialisation de la plupart des outils, le besoin de réduire le coût et le temps de fabrication a imposé la nécessité de trouver des solutions permettant d'avoir une vision globale des systèmes en prenant compte de leur complexité et de leur pluridisciplinarité. L'objectif est d'assurer la cohérence du système dès les étapes les plus en amont du processus de

---

conception. Dans ce contexte, l'utilisation de langages standardisés et des outils de simulation s'imposent comme une pratique incontournable qui sera expliquée dans le chapitre suivant.

## Chapitre II: Plateformes de simulation

### II.1 Introduction

La conception et la simulation des systèmes électroniques ont été un argument fort de motivation pour le développement d'outils, de méthodes et langages permettant de gérer la complexité croissante des circuits et des systèmes.

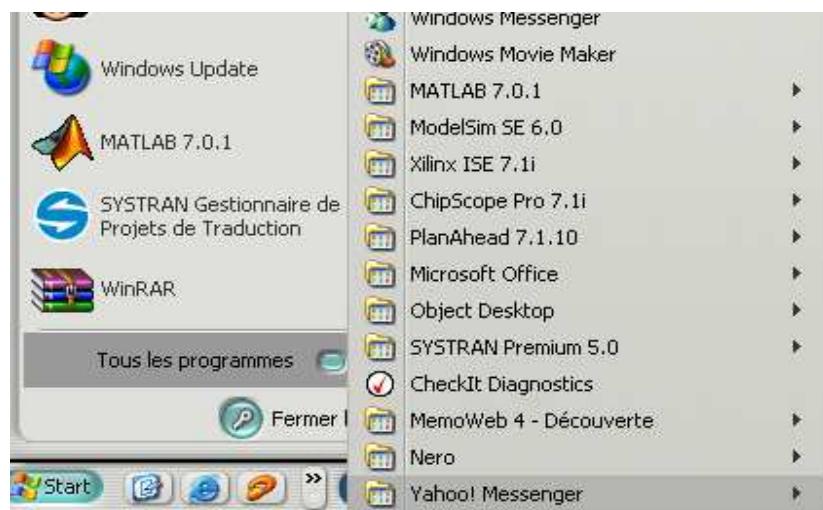

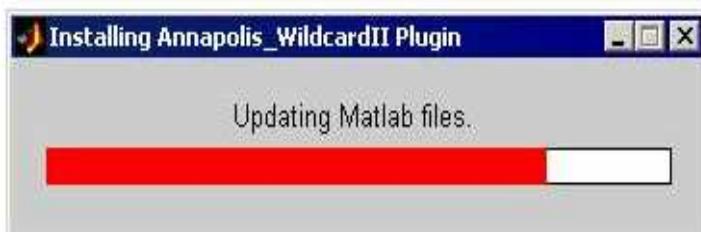

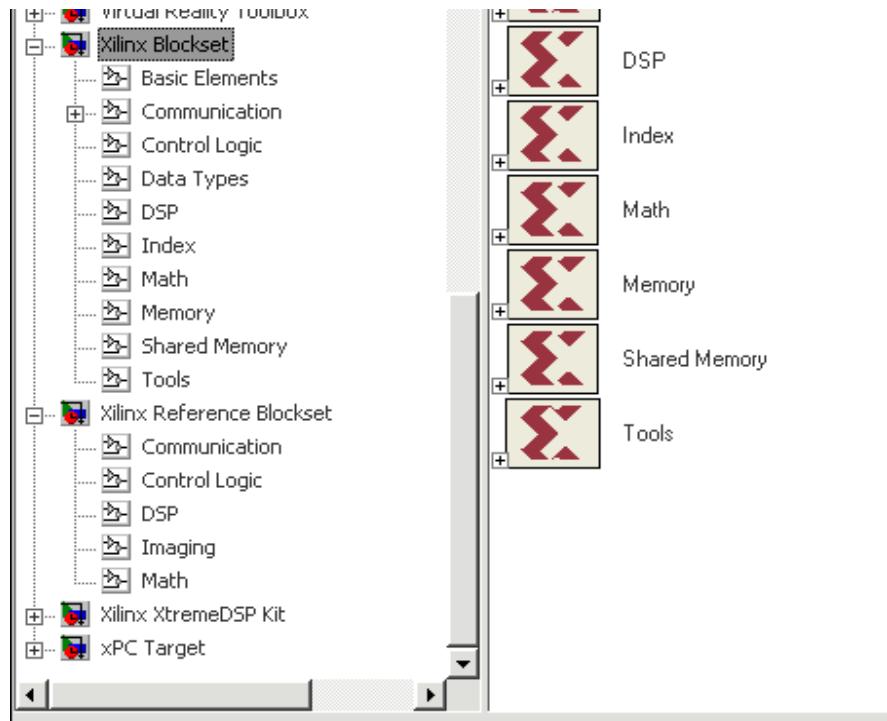

Pour cela, nous avons mis en place des plateformes de simulation qui sont composées principalement de MATLAB, ModelSim 6.0 et FPGA. Pour le kit de la carte FPGA, nous trouvons principalement : ISE 7.1i, Chip Scope pro, PlanAhead, Synplify 7.3.4 et System Generator qui permettent d'assurer l'interfaçage entre plateformes. En plus, nous présentons les nouveautés de chaque outil et les résultats qu'il produit pour la Co-Simulation des systèmes hétérogènes tous en conservant le même objectif qui est en premier lieu la réduction du temps de conception.

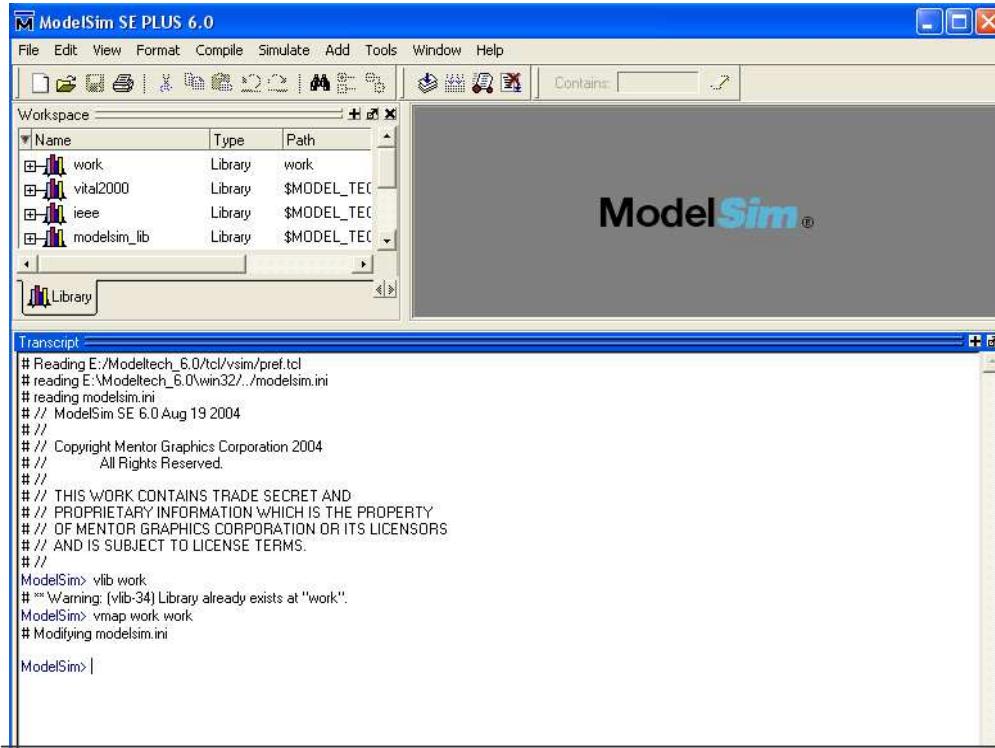

### II.2 Simulation VHDL (ModelSim)

Le VHDL est un langage général de description de matériel permettant un grand niveau d'abstraction. Un système aussi complexe peut être décrit sous forme d'un ensemble de blocs interconnectés [Pn 03].

**Figure 6 :** Le simulateur VHDL.

Lorsque nous désirons réaliser un circuit de type programmable, ASIC, ou bien de type circuit imprimé, nous sommes soumis à une double contrainte technologique. Il faut savoir représenter un certain nombre de primitives [Sdc03] : nous parlons alors de niveau portes avec des fonctions logiques de base (ET, OU etc...), des fonctions combinatoires MSI (addition, multiplexeur etc...), des fonctions séquentielles simples (bascules et registres), (mémoire et latch). Le synthétiseur est l'outil capable d'interpréter une certaine description VHDL et d'en déduire le schéma niveau porte correspondant. La description acceptable par le synthétiseur sera dite niveau RTL (Register Transfer Logic). Le synthétiseur est très efficace au niveau porte pour des tâches telles que l'implantation des fonctions combinatoires, le calcul, le codage du compteur, le séquenceur, l'implantation des échanges par bus etc... Par contre, les choix d'architecture, la structuration d'un système sont des tâches de trop haut niveau et restent à la charge du concepteur.

Le VHDL synthétisable est soumis à des limitations propres au synthétiseur (ceux-ci évoluent sans-cesse et essaient d'intégrer des fonctions de plus en plus complexes). Au moment de la description VHDL, nous devons avoir une idée de ce qui va être généré :

- Il faut que la table de vérité d'un circuit combinatoire soit complètement définie.

- Dans un système synchrone, les fronts d'horloge doivent être parfaitement identifiés.

- Le nombre de bits d'un mot soit optimisé etc.

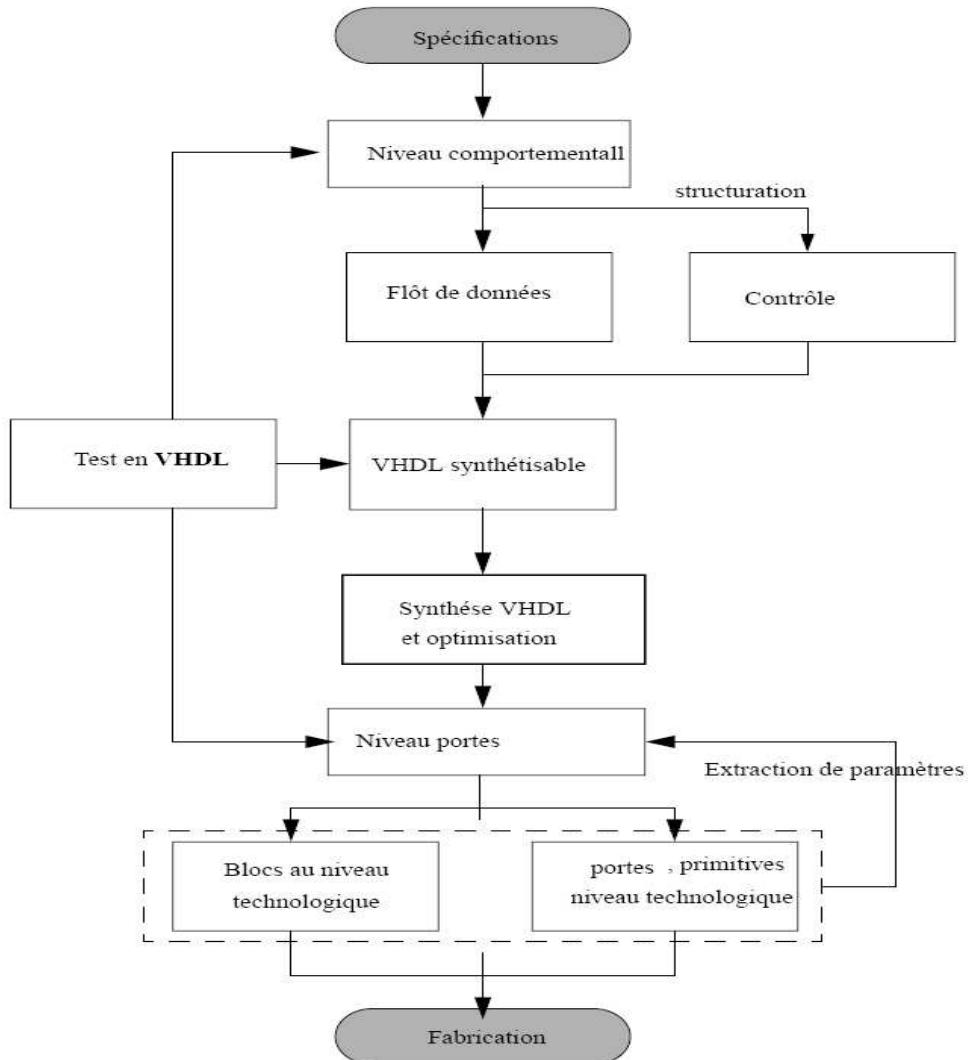

Donc, nous pouvons dire que le VHDL est un outil incontournable lors d'un cycle de conception. Il permet de passer d'un niveau très abstrait à un niveau circuit comme l'illustre la Figure 7. Tout le long du cycle, certaines parties resteront inchangées car non synthétisables, ce sont les dispositifs de test du circuit. Le circuit en cours de conception passera de l'état de modèle abstrait à celui de description synthétisable.

**Figure7 :** Utilisation du VHDL pour les niveaux de conception.

## II.3 Simulation MATLAB

The MathWorks Release 14 inclut tous les produits de l'environnement MATLAB® et Simulink® [Tmw04c].

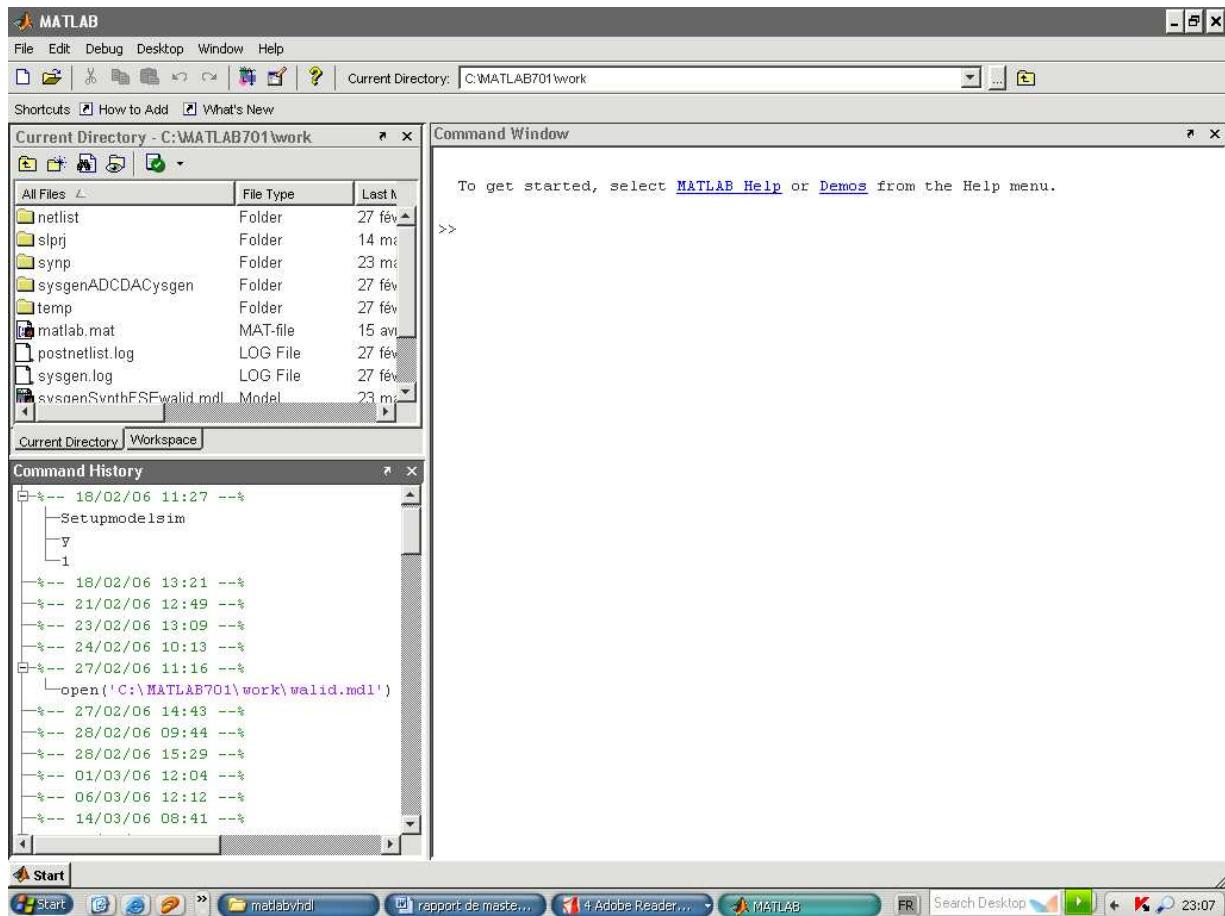

**Figure 8 :** L'interface de MATLAB 7.

### Nouveautés pour le calcul scientifique avec MATLAB 7 :

Cette version inclut de nouveaux outils de programmation, la prise en charge des calculs entiers et simple précision, la possibilité de manipuler des ensembles de données plus importants et apporte des améliorations au niveau des performances. De plus, MATLAB Compiler 4 prend en charge la totalité du langage MATLAB, permettant ainsi le déploiement d'un plus grand nombre d'applications.

MATLAB est un langage de calcul scientifique de haut niveau et un environnement interactif pour l'analyse de données et le développement d'algorithmes et d'applications. Elle inclut aussi de nouvelles fonctionnalités majeures dans les domaines de la programmation et de la génération automatique du code, du graphe et de la visualisation, des mathématiques, de l'accès aux données. Les nouvelles fonctionnalités sont les suivantes :

#### **Nouveautés pour la conception basée sur des modèles avec Simulink 6 :**

Cette version prend en charge les projets de développement de très grande largeur et la conception d'applications dont la performance est un point critique. Simulink 6 inclut de nouvelles fonctionnalités pour gérer les modèles de grande taille et augmenter l'efficacité des flux de travail pour les systèmes de contrôle, de traitement du signal et de communication.

Simulink est une plate-forme pour la simulation multi domaine et la conception basée sur des modèles de systèmes dynamiques. Il fournit un environnement graphique interactif et un ensemble de bibliothèques de blocs personnalisables qui nous permettent de concevoir, de simuler, de mettre en œuvre et de tester de façon précise des systèmes de contrôle, de traitement de signal, de communication et d'autres systèmes qui varient dans le temps. Simulink 6 améliore les performances, la réactivité, la fidélité de la modélisation et l'efficacité des flux de travaux lors de la modélisation de grands systèmes. Les nouvelles fonctionnalités sont les suivantes :

#### **Modélisation basée sur des composants pour les grands systèmes :**

- Possibilité de segmenter un modèle en plusieurs fichiers, où chaque fichier est un modèle séparé.

- Possibilité de modéliser, de simuler, de tester et de mettre en œuvre individuellement chaque composant de la conception avant de l'incorporer dans un modèle de système.

- Meilleure intégration de nos modèles dans un logiciel existant de gestion de configuration et de contrôle de version basé sur des fichiers.

- Chargement et génération de code incrémentiels.

- Meilleurs diagrammes de mise à jour et simulations plus rapides pour les modèles de grande taille.

- Fonction Model Workspaces fournit des espaces de travail séparés pour le stockage et la gestion des paramètres et des variables de chaque modèle.

- Meilleure prise en charge des bus pour la définition des interfaces, la prise en charge des opérations sur les signaux de bus et la spécification des bus comme structures pour la génération de code.

## II.4 Xilinx ISE 7.1i

La nouvelle version d'ISE [Xilinx05], la version 7.1, ajoute une technologie plus innovatrice pour aider à minimiser la logique de développement et le coût de production. ISE 7.1i fournit une exécution plus rapide que n'importe quel autre PLD, il permet une conception à grande vitesse, et plus facile à employer par rapport au logiciel de conception disponible. Elle permet au client de lancer leurs produits sur le marché avant leurs concurrents.

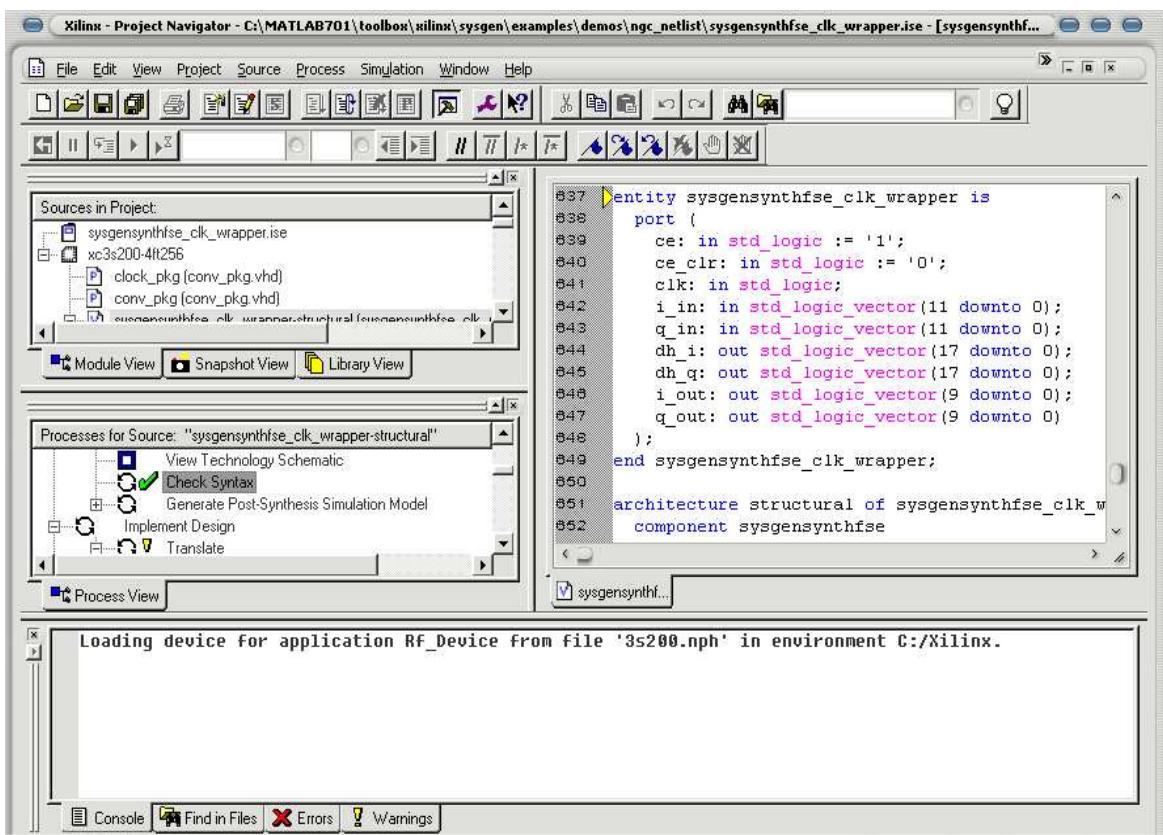

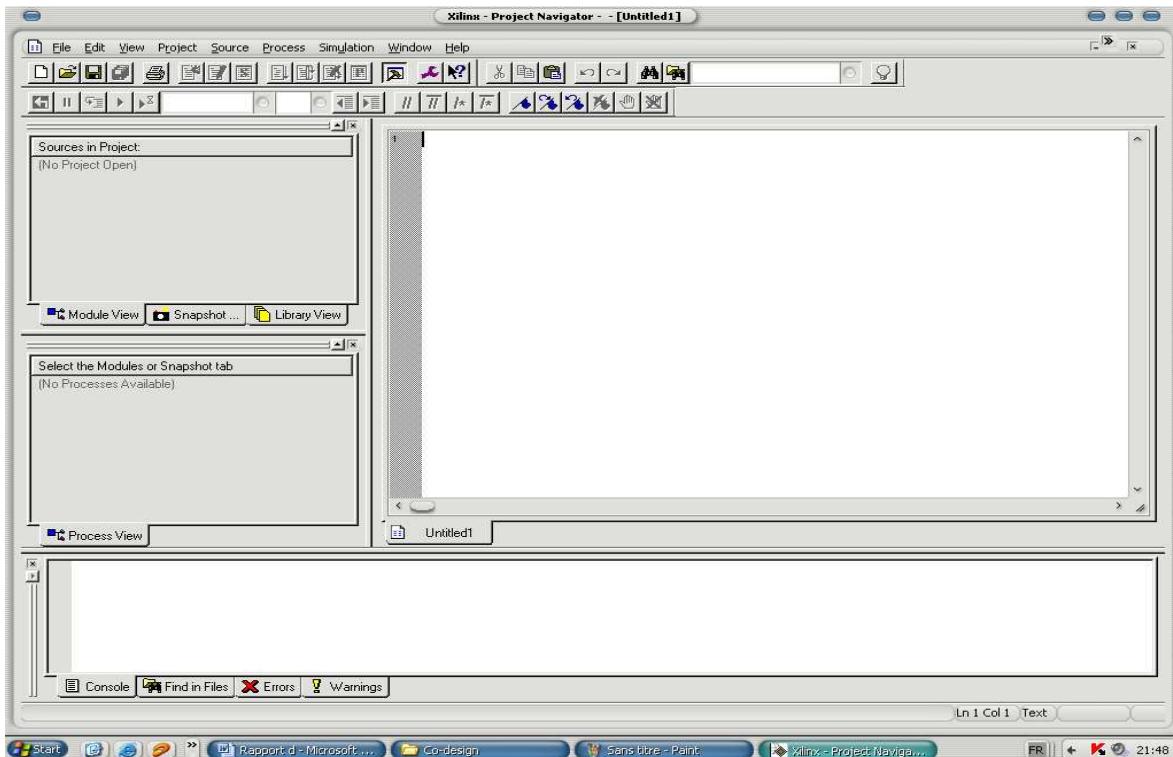

Figure 9 : L'interface ISE 7.1i de Xilinx.

La facilité d'utilisation est un grand objectif de XilinX. Avec le dégagement d'ISE 7.1i, XilinX peut maintenant offrir aux clients une solution intégrée de simulation avec le nouveau simulateur d'ISE. Le client de chaque base d'ISE BaseX et d'ISE accède à une version limitée appelée le simulateur « Lite d'ISE ». Les clients de *base d'ISE* peuvent améliorer le simulateur d'ISE.

ISE 7.1 fournit l'appui pour la nouvelle famille de Spartan-3[Xap 05]. Ce dernier fixe une nouvelle norme pour réduire le prix de FPGA. Cette famille d'industrie, présente les dispositifs les moins chers de la deuxième génération sur les technologies de 90nm.

La nouveauté se prolongeant aux FPGAs Virtex-4, ISE 7.1i offre plus de dispositif d'appui additionnel dans ISE *BaseX* et ISE. Ce nouvel appui lui facilite plus encore pour les clients de commencer des conceptions visant FPGAs par des logiques avancées, rendement plus élevé, densité la plus élevée, et une grande capacité de mémoire.

## Configurations

Le logiciel XilinX ISE 7.1i offre trois configurations de conception, tous fournies sous le logiciel intégré de l'environnement (ISE) de conception:

**Figure 10 :** ISE Foundation 7.1i de XilinX.

**ISE Foundation 7.1i :** La *base d'ISE* est l'exécution de conception de la logique programmable la plus complète de l'industrie. Cette configuration d'ISE soutient toutes les familles de logique de « fil » de XilinX et fournit tout requis pour remplir n'importe quelle conception de XilinX, intégrant « seamlessly » avec les produits de la vérification les plus

avancés de l'industrie. Xilinx offre également les outils facultatifs de productivité conçus pour collaborer avec la base d'ISE.

**Figure 11 :** ISE BaseX 7.1i de Xilinx.

**ISE BaseX 7.1i :** ISE BaseX est l'environnement programmable de conception de logique le plus rentable, le plus complet. La configuration d'ISE BaseX fournit toutes les possibilités contenues dans ISE WebPACK en plus des outils additionnels. Ils aident les concepteurs à rendre leur conception logique programmable, plus rapidement et minimiser le coût de conception.

**Figure 12:** ISE WebPACK 7.1i de Xilinx.

**ISE WebPACK 7.1i :** la configuration d'ISE la plus facile à obtenir, il est sur le Web et libre ! ISE WebPACK fournit tout requis pour remplir des conceptions logiques programmables visant tout le principal Xilinx CPLDs et FPGAs à basse densité. ISE WebPACK combine l'entrée de HDL, la synthèse et les possibilités de vérification avec les outils de l'exécution les plus puissants de l'industrie. ISE WebPACK est disponible pour le Microsoft Windows XP, le Windows 2000, et maintenant Linux 3.

Pour augmenter la productivité nous devons aussi avoir les Logiciels facultatifs qui sont :

- **Chip Scope Pro On-chip Debugging Tools:** les conditions de taille [XilinX05], de vitesse et de conseil de la situation actuelle d'aujourd'hui FPGAs le rendent difficile de corriger des conceptions en utilisant des méthodes traditionnelles d'analyse de logique. Les outils de Chip Scope fournissent un outil puissant et précis pour aider à vérifier et corriger des conceptions de FPGAs, en temps réel et sur option des travaux directement avec des analyseurs de logique d'Agilent pour encore une analyse plus profonde de signal de FPGA. Chip Scope pro permet l'insertion des noyaux low-profile d'analyseur de logique et d'autobus dans des conceptions. Ces noyaux logiques permettent à l'utilisateur de regarder tous signaux et nœuds internes dans un FPGA. Déclencher les conditions et l'installation en temps réel par l'intermédiaire du port de JTAG sans affecter la logique d'utilisateur ou exiger la recompilation de la conception.

- **PlanAhead Hierarchical Floorplanner :** PlanAhead fournit une conception hiérarchique, blocue basée et accroissement méthodologie, permettant à des concepteurs de changer seulement une partie de la conception et de laisser la conception intacte. Les possibilités hiérarchiques de planification de conception de PlanAhead incluent une interface utilisateur graphique avancée (GUI) qui le rend facile à utiliser pour même les concepteurs inexpérimentés. L'affichage intuitif des ressources de dispositif, la hiérarchie de connectivité, logique et physique laisse des concepteurs visualiser et fixer rapidement les problématiques. Les concepteurs peuvent créer et mettre en œuvre l'hiérarchie physique indépendamment de l'hiérarchie logique, et simultanément projeter et analyser les réalisations physiques multiples, maximisant l'exploration de l'espace de conception en identifiant plus rapidement la réalisation optimal.

- **ModelSim Xilinx :** ModelSim XE est un environnement complet de simulation du PC HDL qui permet aux concepteurs de vérifier le code source de HDL , les modèles fonctionnels et de synchronisation de leurs conceptions. MXE réalise la simulation de HDL et l'environnement de correction fournissant l'assurance de 100% VHDL et de langue de Verilog.

- **System Generator for DSP :** est l'outil logiciel du ministre de l'industrie pour concevoir, simuler, et mettre en application les systèmes à base FPGA de rendement élevé