---

*Table des matières*

---

***Introduction générale******Chapitre1 : Système sur puce multiprocesseurs temps réel: état de l'art***

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| 1- Introduction .....                                                                    | 10 |

| 2- Taxonomie d'architectures multiprocesseurs .....                                      | 10 |

| 2.1- Les systèmes à mémoire partagée (Shared-memory systems).....                        | 10 |

| 2.2- Les systèmes à mémoire distribuée (distributed memory system) .....                 | 11 |

| 2.3- Comparaison entre un système à mémoire partagée et celui à mémoire distribuée ..... | 12 |

| 2.4- Les systèmes à mémoire distribuée partagée .....                                    | 13 |

| 3- système d'exploitation temps réel .....                                               | 13 |

| 3.1- RTOS et contrainte temps réel .....                                                 | 13 |

| 3.1.1- Systèmes à contraintes souples .....                                              | 14 |

| 3.1.2- Systèmes à contraintes dures .....                                                | 14 |

| 3.2- Caractéristiques d'un RTOS .....                                                    | 14 |

| 3.3- Concepts de base d'un RTOS .....                                                    | 15 |

| 3.3.1- Section critique .....                                                            | 15 |

| 3.3.2- Ressource partagée et exclusion mutuelle .....                                    | 15 |

| 3.3.3- Tâche .....                                                                       | 15 |

| 3.3.4- Communication entre tâches.....                                                   | 18 |

| 3.4- Conflits.....                                                                       | 20 |

| 3.4.1- Interblocage (Deadlock) .....                                                     | 20 |

| 3.4.2- Inversions des priorités.....                                                     | 20 |

| 3.5- Systèmes d'exploitation dans les systèmes embarqués .....                           | 21 |

| 3.5.1- Caractéristiques des RTOS pour les systèmes embarqués .....                       | 22 |

| 3.5.2- Importance des RTOS pour les systèmes embarqués .....                             | 22 |

| 3.5.3- Limites des RTOS dans les systèmes embarqués .....                                | 23 |

| 4- Quelques exemples de noyaux embarqués .....                                           | 24 |

| 4.1- RTEMS .....                                                                         | 24 |

| 4.1.1- Architecture interne de RTEMS .....                                               | 24 |

| 4.1.2- Architecture d'une application RTEMS.....                                         | 24 |

| 4.1.3- Services de RTEMS .....                                                           | 25 |

| 4.1.4- Ordonnancement .....                                                              | 25 |

| 4.1.5- Caractéristiques et capacités .....                                               | 25 |

| 4.1.6- Aspect multiprocesseurs.....                                                      | 26 |

| 4.2- Ecos .....                                                                          | 26 |

| 4.2.1- Caractéristiques et capacités .....                                               | 26 |

| 4.2.2- HAL .....                                                                         | 27 |

| 4.2.3- Détails du noyau .....                                                            | 27 |

| 4.2.4- Ordonnancement .....                                                              | 28 |

| 4.2.5- Avantages d'Ecos .....                                                            | 28 |

| 4.3- QNX .....                                                                           | 29 |

| 4.3.1- Caractéristiques techniques .....                                                 | 30 |

| 4.3.2- Caractéristiques de spécification de QNXv6.1 .....                                | 30 |

| 4.4- Windows CE .....                                                                    | 31 |

| 5- Estimation de performance dans les systèmes embarqués temps réel .....                | 33 |

| 5.1- Approches d'estimation du temps d'exécution :.....                                  | 34 |

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| 5.1.1- Travaux visant des architectures cibles monoprocesseur : .....   | 34 |

| 5.1.2- Travaux visant des architectures cibles multiprocesseurs : ..... | 35 |

| 6- Contribution.....                                                    | 36 |

| 7- Conclusion .....                                                     | 36 |

## ***Chapitre 2: Conception d'un MPSoC temps réel et estimation de performance***

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| 1-Introduction .....                                                                     | 39 |

| 2- Plate-forme de conception .....                                                       | 39 |

| 2.1- Etude du système d'exploitation temps réel : MicroC/OS-II.....                      | 39 |

| 2.1.1- Capacités et caractéristiques .....                                               | 40 |

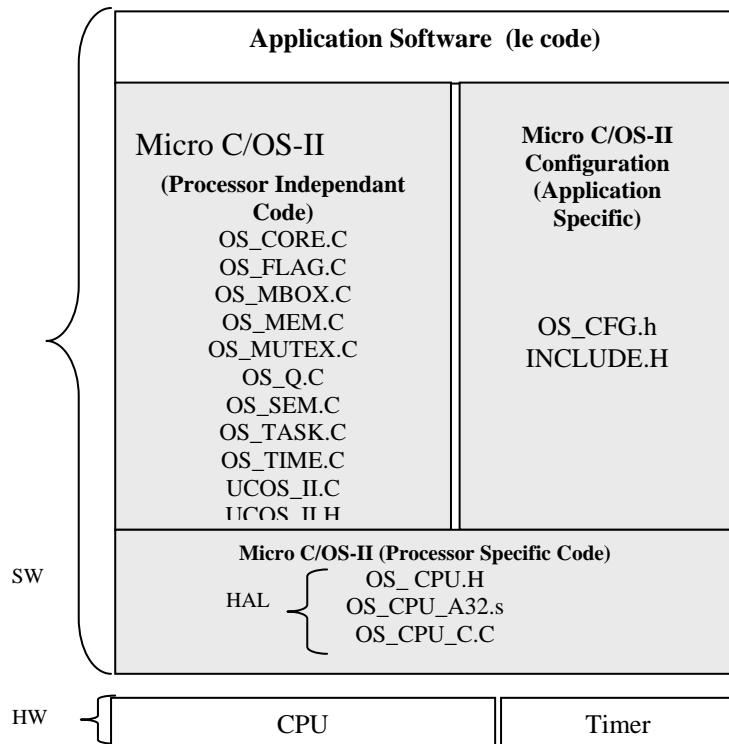

| 2.1.2- Structure de MicroC/OS-II .....                                                   | 40 |

| 2.1.3. Fonctionnement de MicroC/OS-II.....                                               | 41 |

| 2.1.4- Communication inter tâches .....                                                  | 42 |

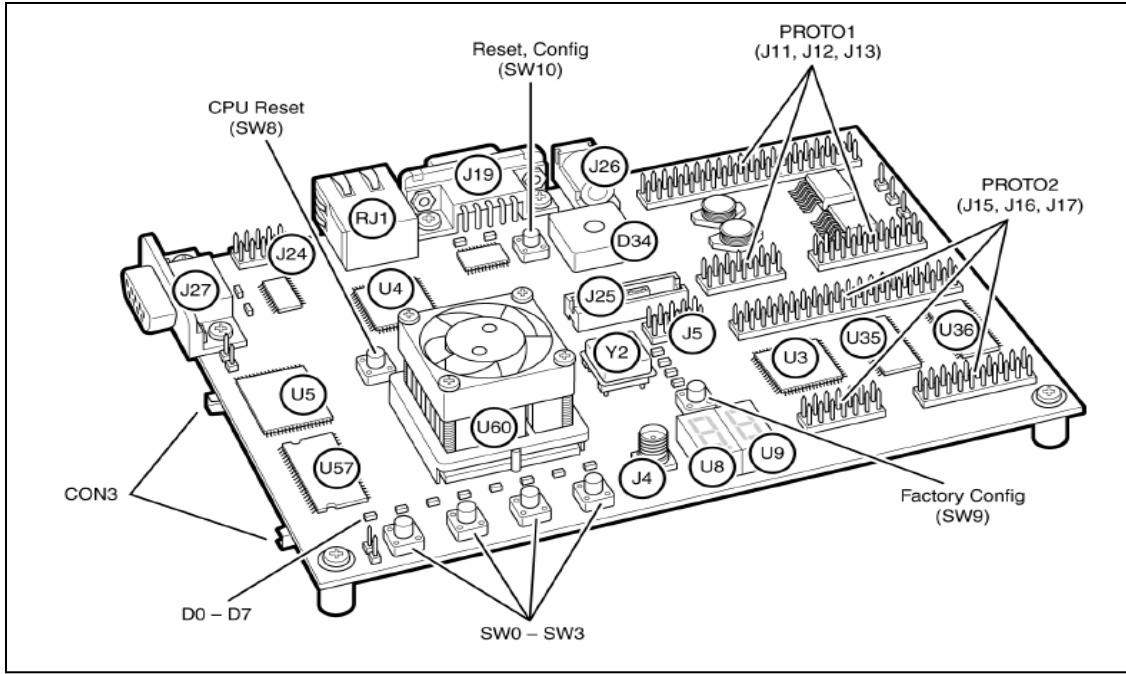

| 2.2- Carte de développement : STRATIX-II.....                                            | 44 |

| 2.2.1. Description .....                                                                 | 44 |

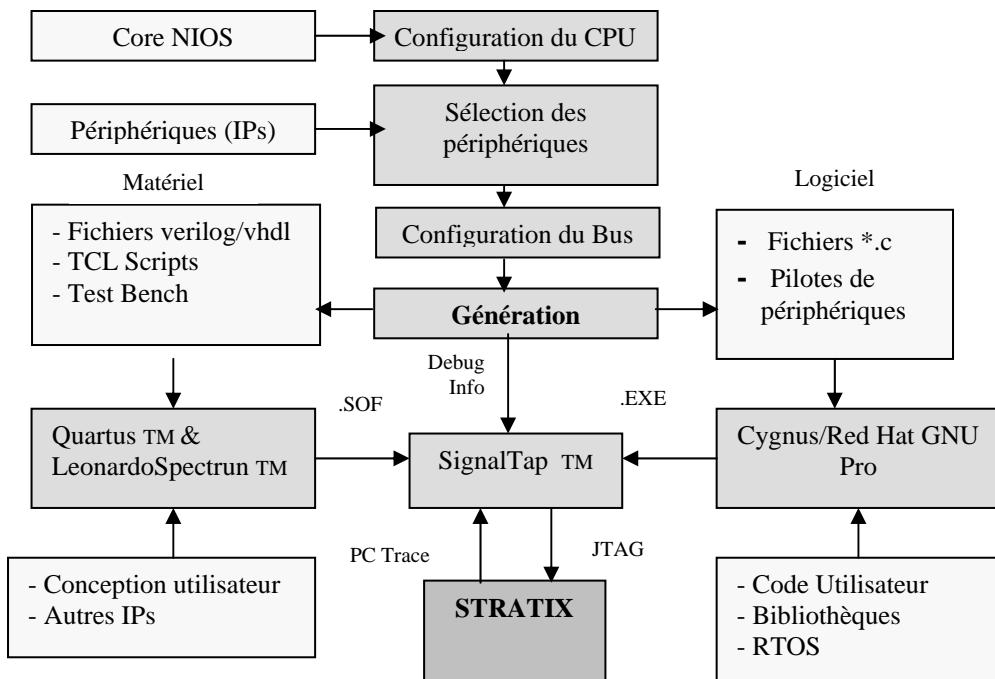

| 2.3- Environnement de développement.....                                                 | 45 |

| 2.3.1. Environnement Quartus .....                                                       | 45 |

| 2.3.2. SOPC Builder.....                                                                 | 45 |

| 3- Méthodologie de développement logiciel et matériel.....                               | 46 |

| 4- Conception d'un système réactif embarqué monoprocesseur.....                          | 46 |

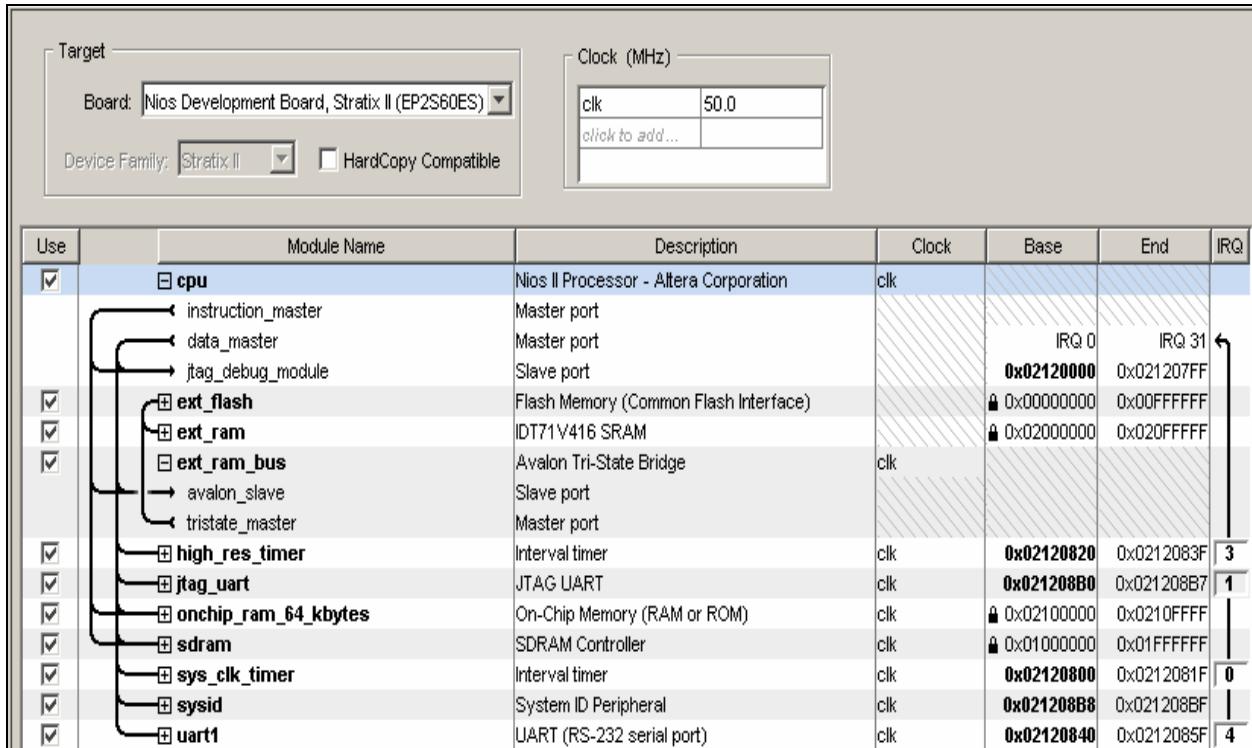

| 4.1- Réalisation de la plate-forme matérielle à base de NIOS II.....                     | 46 |

| 4.2- Portage du MicroC/OS-II sur le processeur NIOS .....                                | 48 |

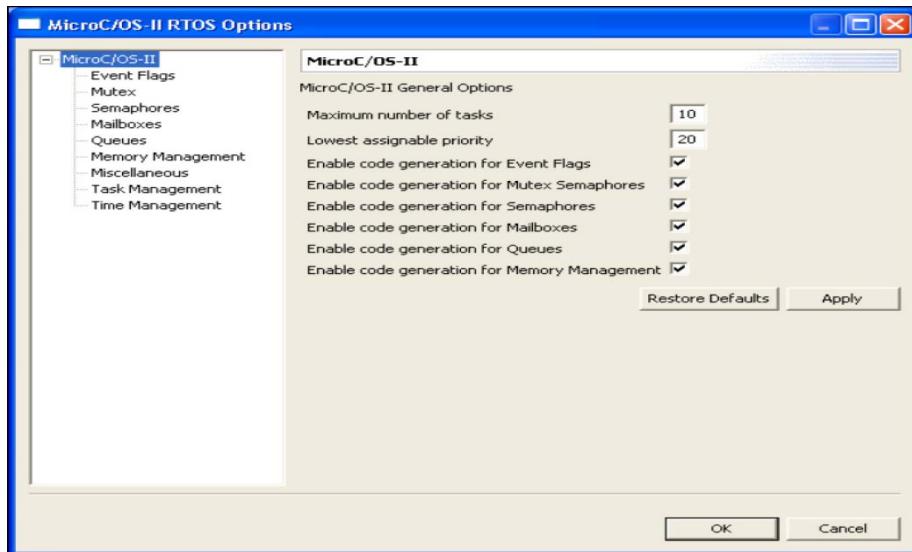

| 4.3- Configuration des services de MicroC/OS-II .....                                    | 49 |

| 5- Conception d'une architecture multiprocesseurs .....                                  | 49 |

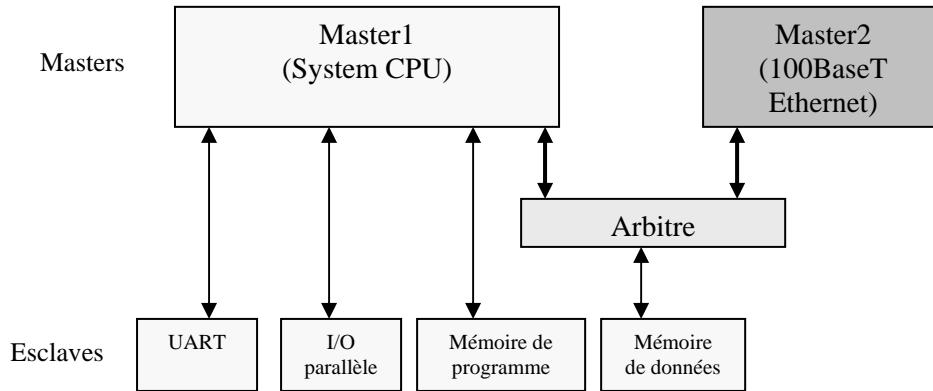

| 5.1- Bus Avalon.....                                                                     | 49 |

| 5.2- Mutex fournie par l'interface Avalon .....                                          | 50 |

| 5.2.1- Comportement de base.....                                                         | 50 |

| 5.2.2- Configuration du mutex dans SOPC Builder.....                                     | 51 |

| 5.2.3- Modèle de programmation logicielle .....                                          | 52 |

| 5.3- Boîte aux lettres « Mailbox» fourni par altéra .....                                | 53 |

| 5.3.1- Comment utiliser le cœur de la boîte aux lettres dans SOPC Builder.....           | 53 |

| 5.3.2- Caractéristiques du mailbox .....                                                 | 54 |

| 5.3.3- Programmation du cœur de la boîte aux lettres .....                               | 54 |

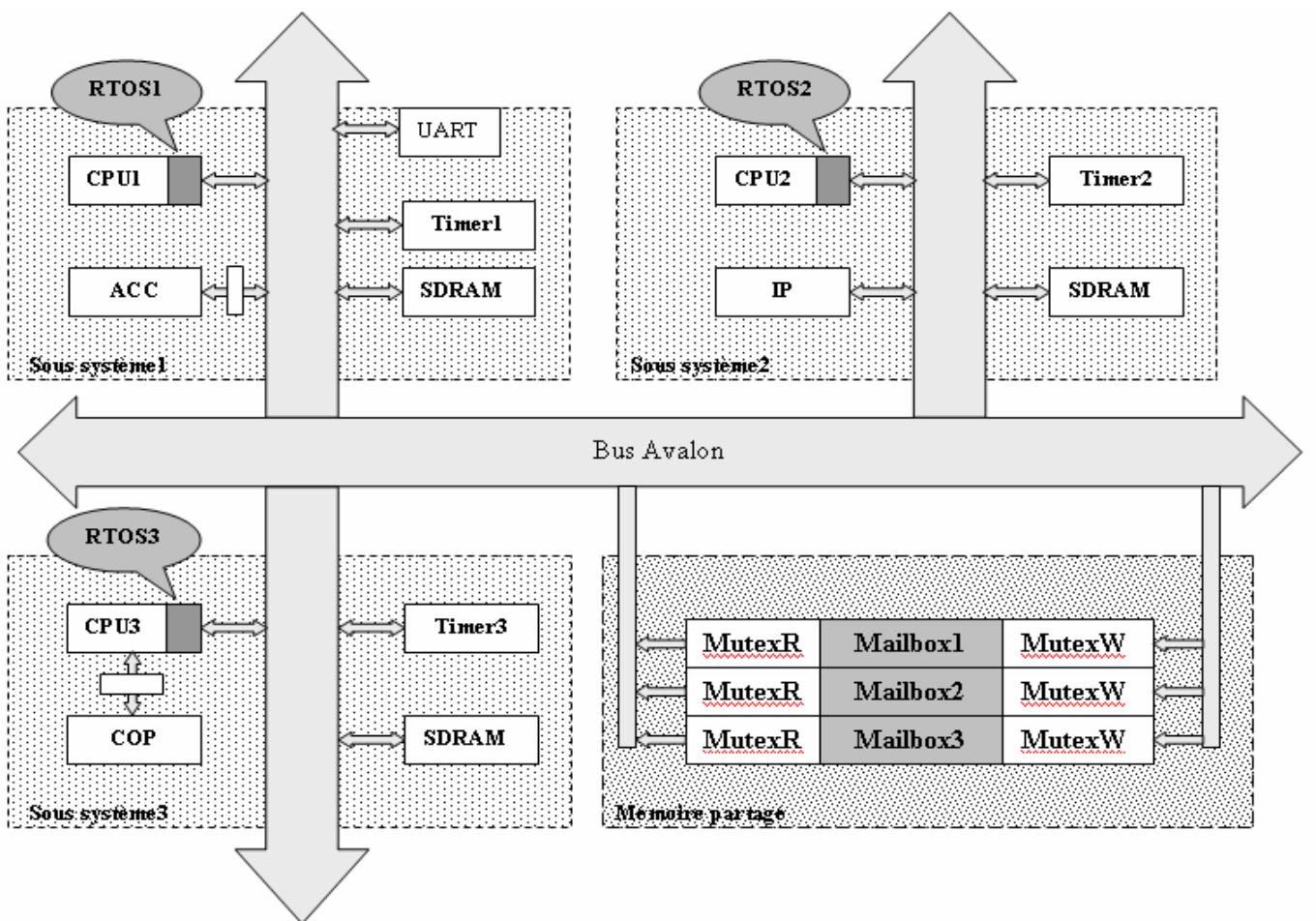

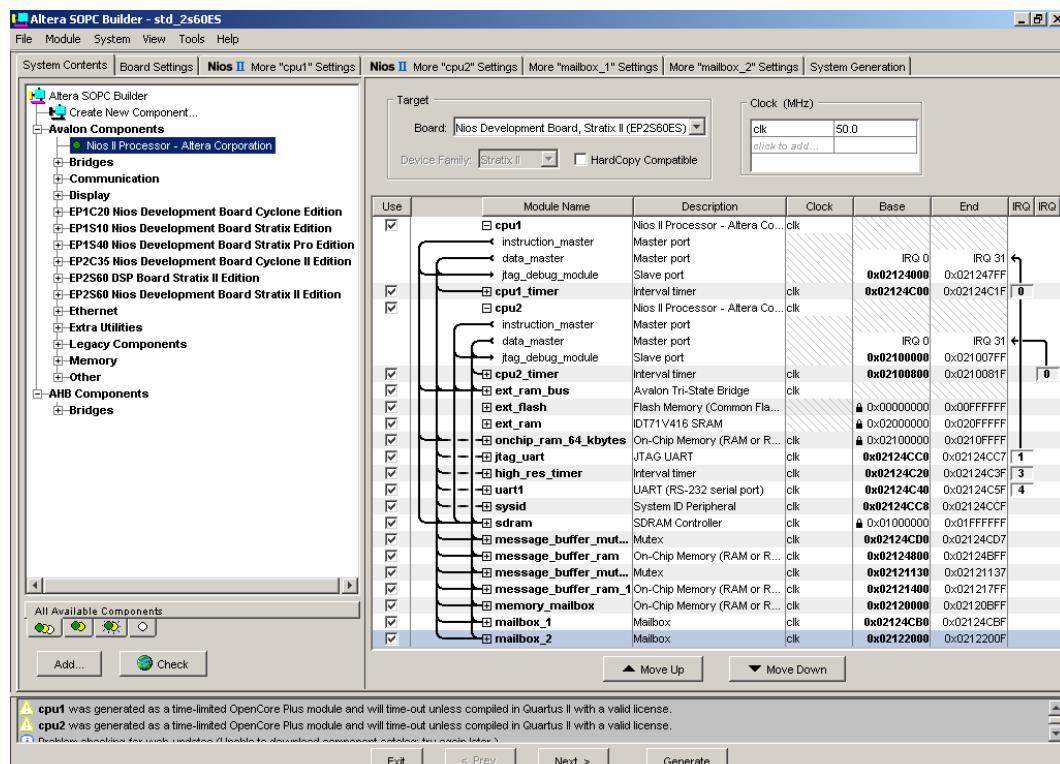

| 5.4-Topologie proposée pour une architecture multiprocesseurs : .....                    | 55 |

| 6- Estimation de performance des systèmes sur puce temps réel.....                       | 57 |

| 6.1- Principe .....                                                                      | 57 |

| 6.2- Remarque .....                                                                      | 57 |

| 6.3- Evaluation de l'effet du MicroC/OS-II sur le temps d'exécution d'une fonction ..... | 58 |

| 6.4- Mesure du temps pris par les services du RTOS .....                                 | 60 |

| 6.5- Formalisation du modèle.....                                                        | 61 |

| 6.6- Mise en équation .....                                                              | 62 |

| 6.6- Limites de la méthode d'estimation .....                                            | 63 |

| 7. Conclusion .....                                                                      | 63 |

## ***Chapitre 3: Expérimentations et validations***

|                                                  |    |

|--------------------------------------------------|----|

| 1- Introduction .....                            | 65 |

| 2- Application de traitement d'images 3D .....   | 65 |

| 2.1- Introduction à la création d'objet 3D ..... | 65 |

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

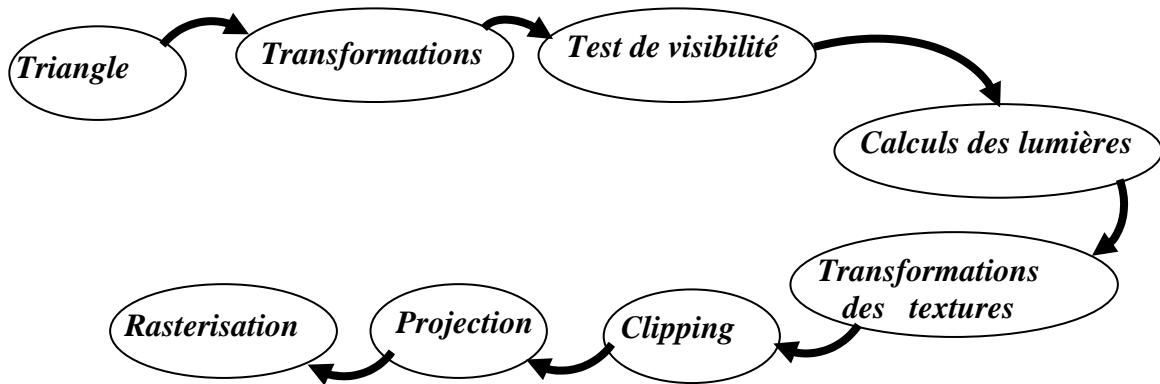

| 2.2- Pipeline 3D.....                                                                              | 66 |

| 2.3- Maillage Triangulaire.....                                                                    | 66 |

| 2.4- Transformation géométrique.....                                                               | 66 |

| 2.4.1- <i>Translation</i> .....                                                                    | 66 |

| 2.4.2- <i>Changement d'échelle</i> .....                                                           | 67 |

| 2.4.3- <i>Rotation</i> .....                                                                       | 67 |

| 2.4.4- <i>Composition de transformation</i> .....                                                  | 68 |

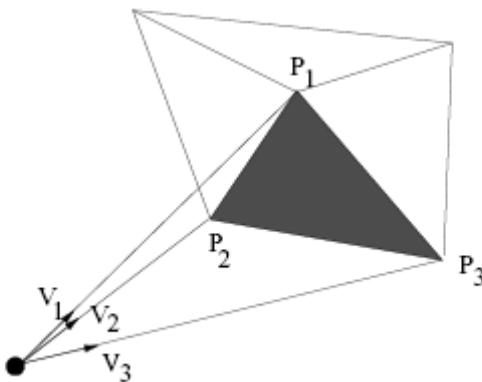

| 2.5- Test de visibilité.....                                                                       | 68 |

| 2.6- Calculs des lumières .....                                                                    | 69 |

| 2.6.1- <i>Lumière ambiante</i> .....                                                               | 69 |

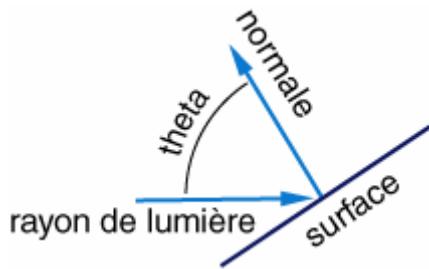

| 2.6.2- <i>Lumière due à une réflexion diffuse</i> .....                                            | 69 |

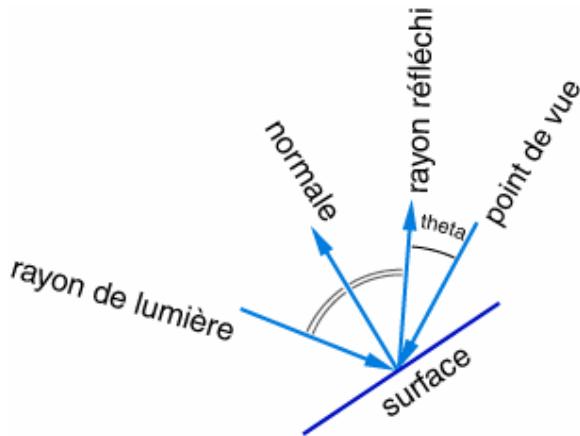

| 2.6.3- <i>Lumière due à une réflexion spéculaire</i> .....                                         | 70 |

| 2.7- Transformations des textures .....                                                            | 71 |

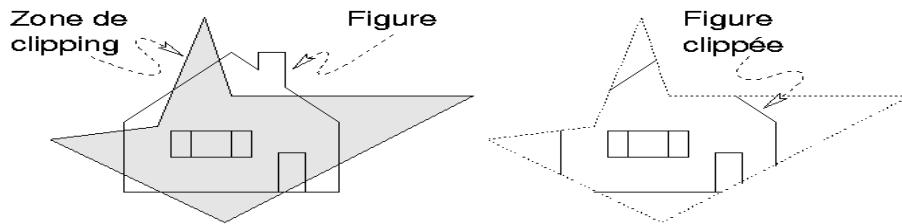

| 2.8- Clipping (fenêtrage).....                                                                     | 71 |

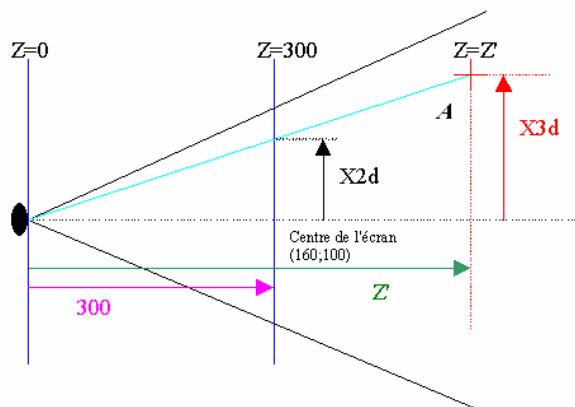

| 2.9- Projection .....                                                                              | 72 |

| 2.10- Rasterisation.....                                                                           | 73 |

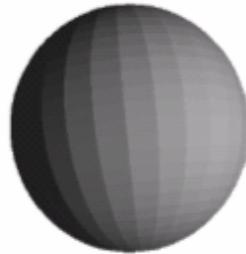

| 2.10.1- <i>Ombrage plat</i> .....                                                                  | 73 |

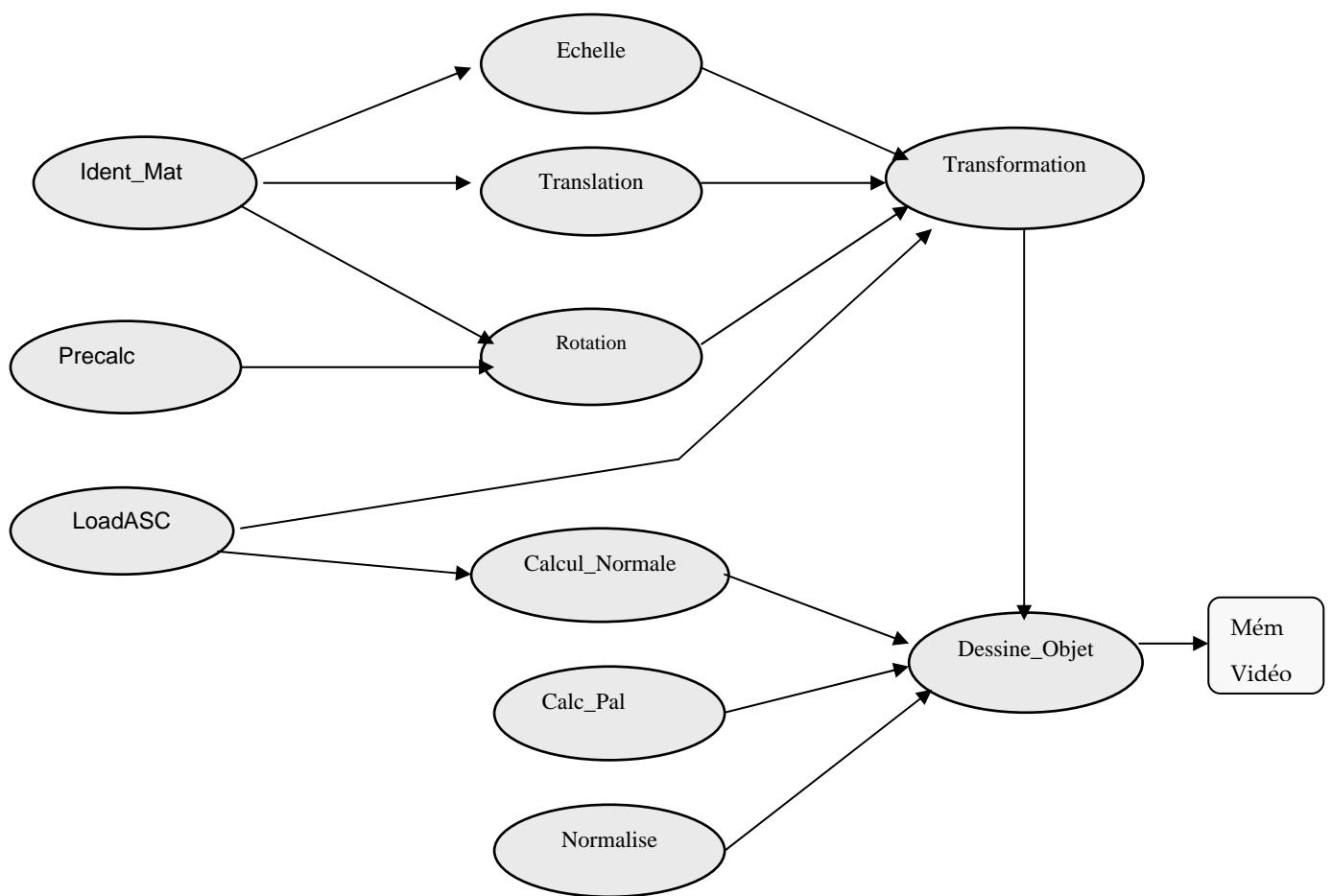

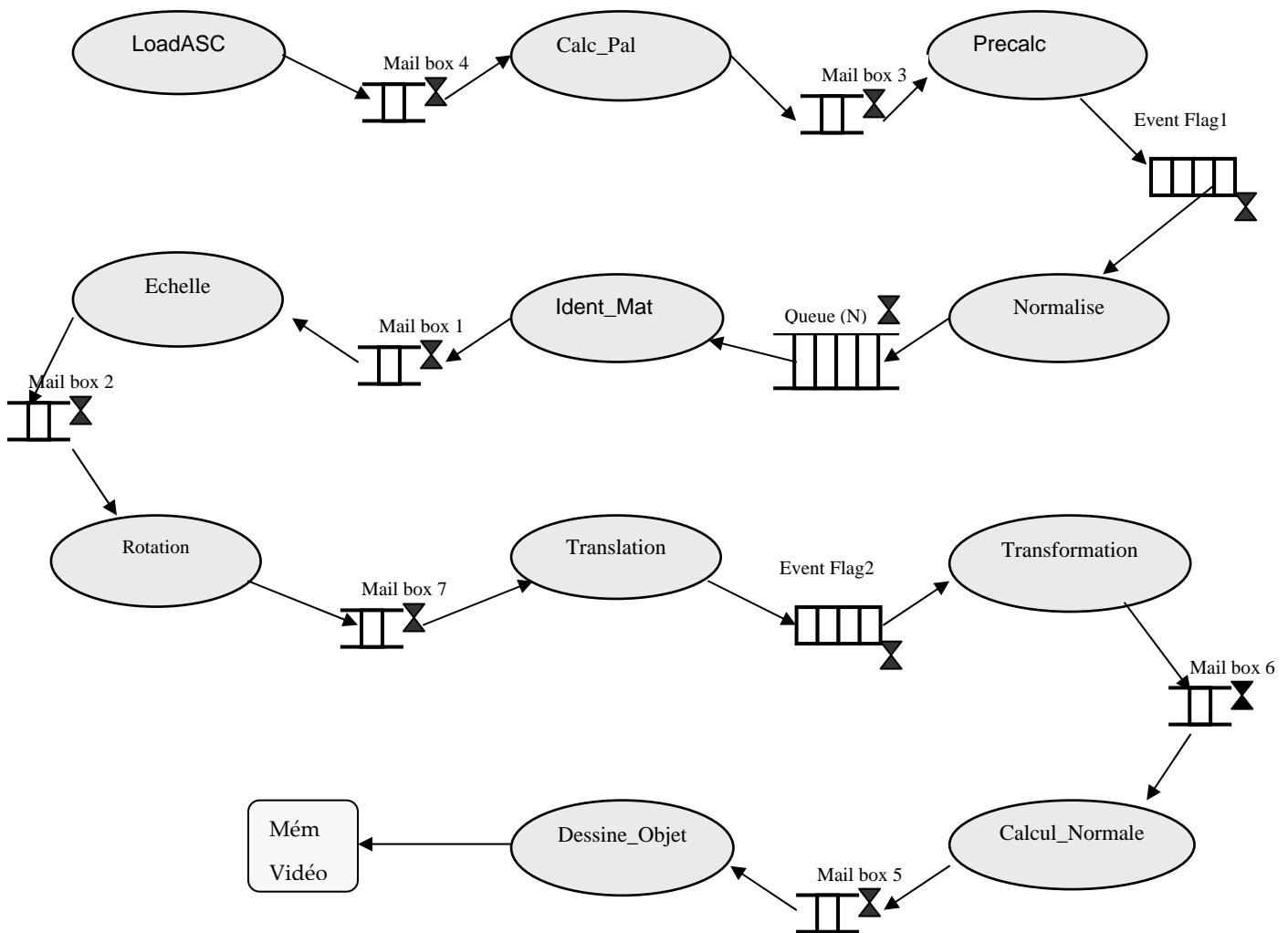

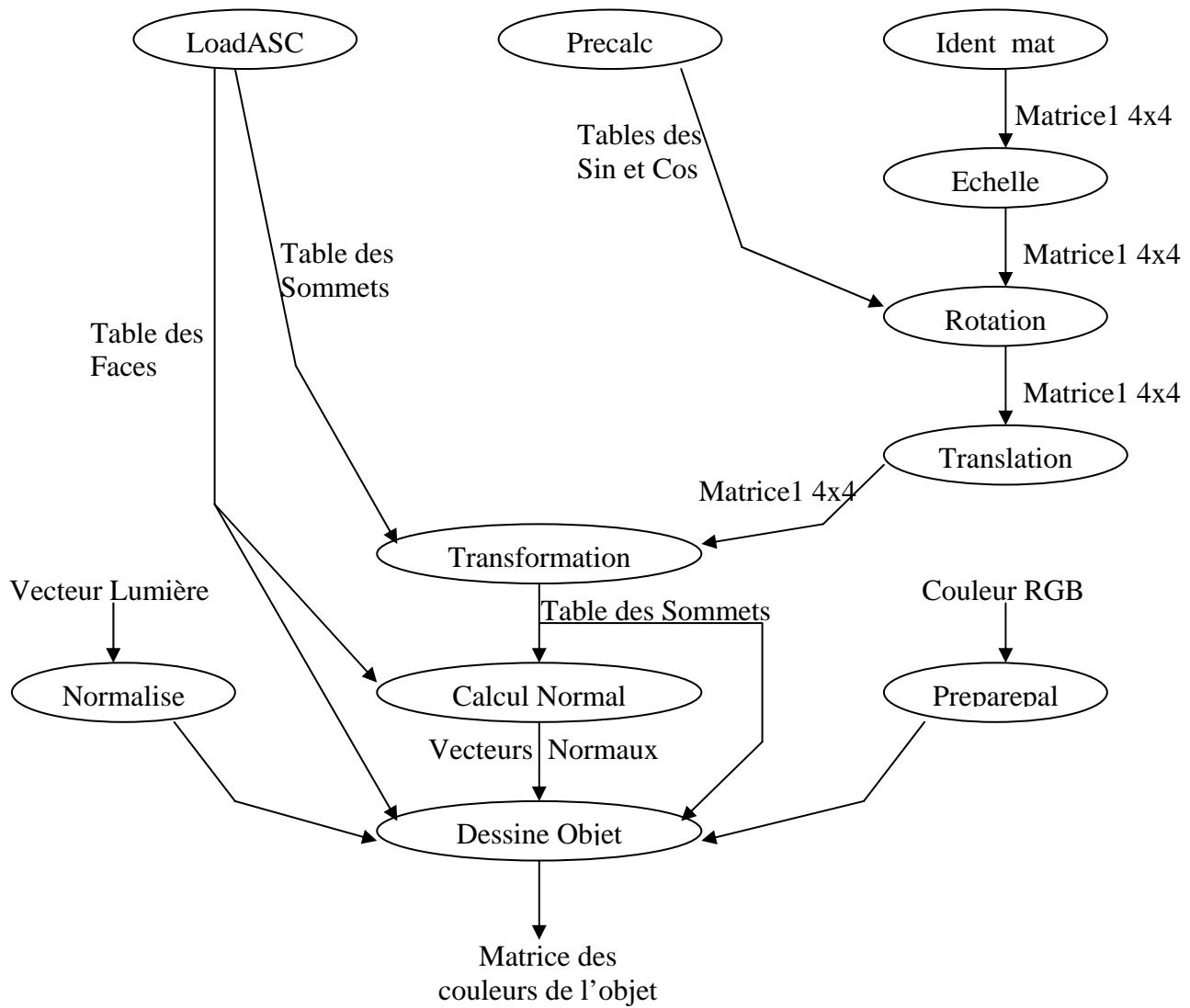

| 2.11- Graphe de tâches de l'application 3D .....                                                   | 73 |

| 3- <i>Validation du modèle d'estimation proposé</i> .....                                          | 74 |

| 4- <i>Conception de coprocesseur</i> .....                                                         | 76 |

| 5- <i>Conception d'accélérateurs pour le traitement d'images 3D</i> .....                          | 77 |

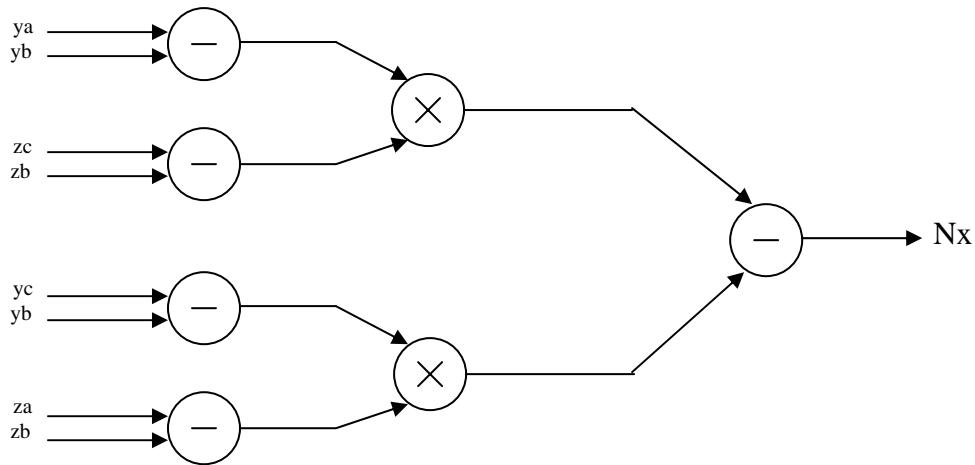

| 5.1- Détermination de la normale à une face .....                                                  | 77 |

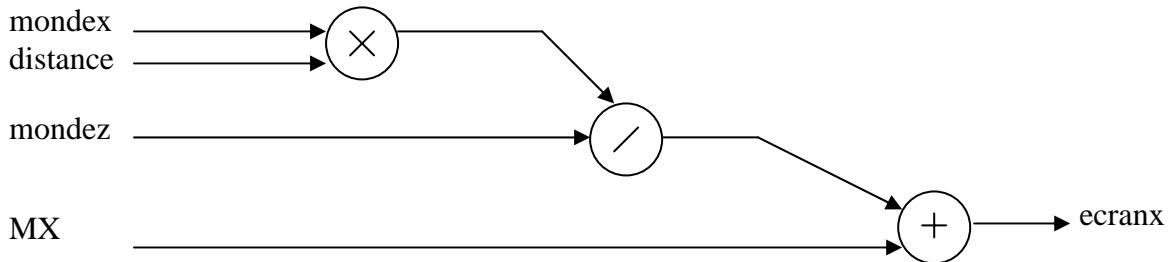

| 5.2- Projection .....                                                                              | 78 |

| ecran = monde * DISTANCE / monde + MX.....                                                         | 78 |

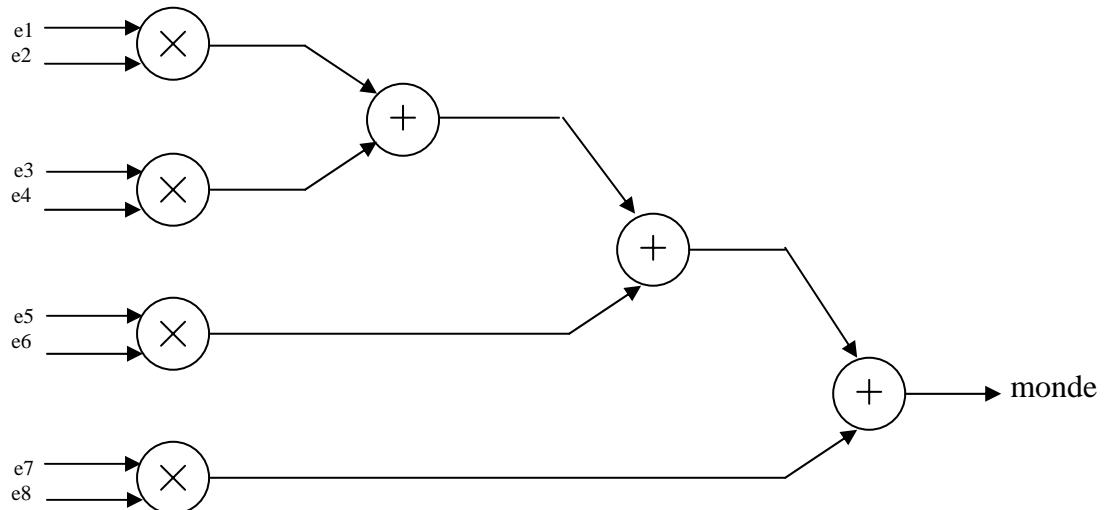

| 5.3- Produit vectoriel.....                                                                        | 78 |

| 5.4- Transformation.....                                                                           | 79 |

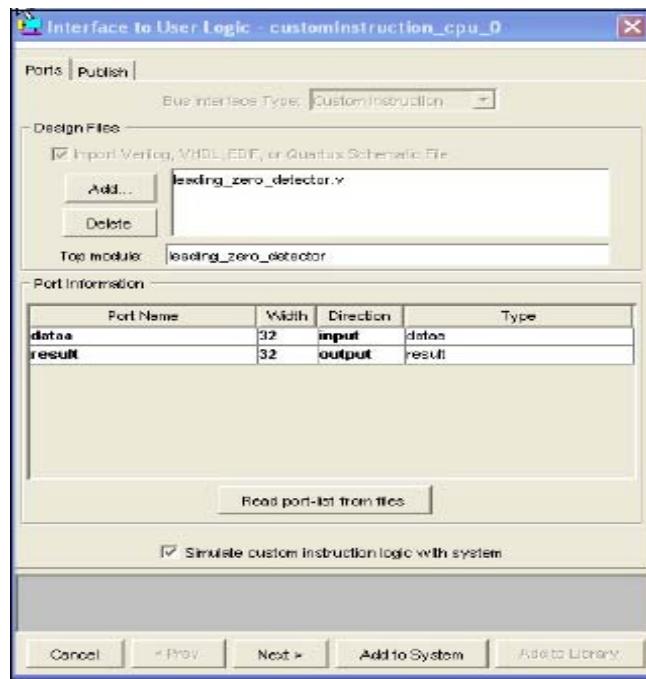

| 5.5- Interconnexion processeur accélérateur .....                                                  | 79 |

| 5.5.1- <i>Différentes méthodes d'interconnexion</i> .....                                          | 79 |

| 5.5.2- <i>Interconnexion à travers les PIO</i> .....                                               | 80 |

| 5.6- Compilation.....                                                                              | 81 |

| 5.7- Mesure accélérateur .....                                                                     | 81 |

| 6- <i>Conception d'un système réactif embarqué multiprocesseurs</i> .....                          | 82 |

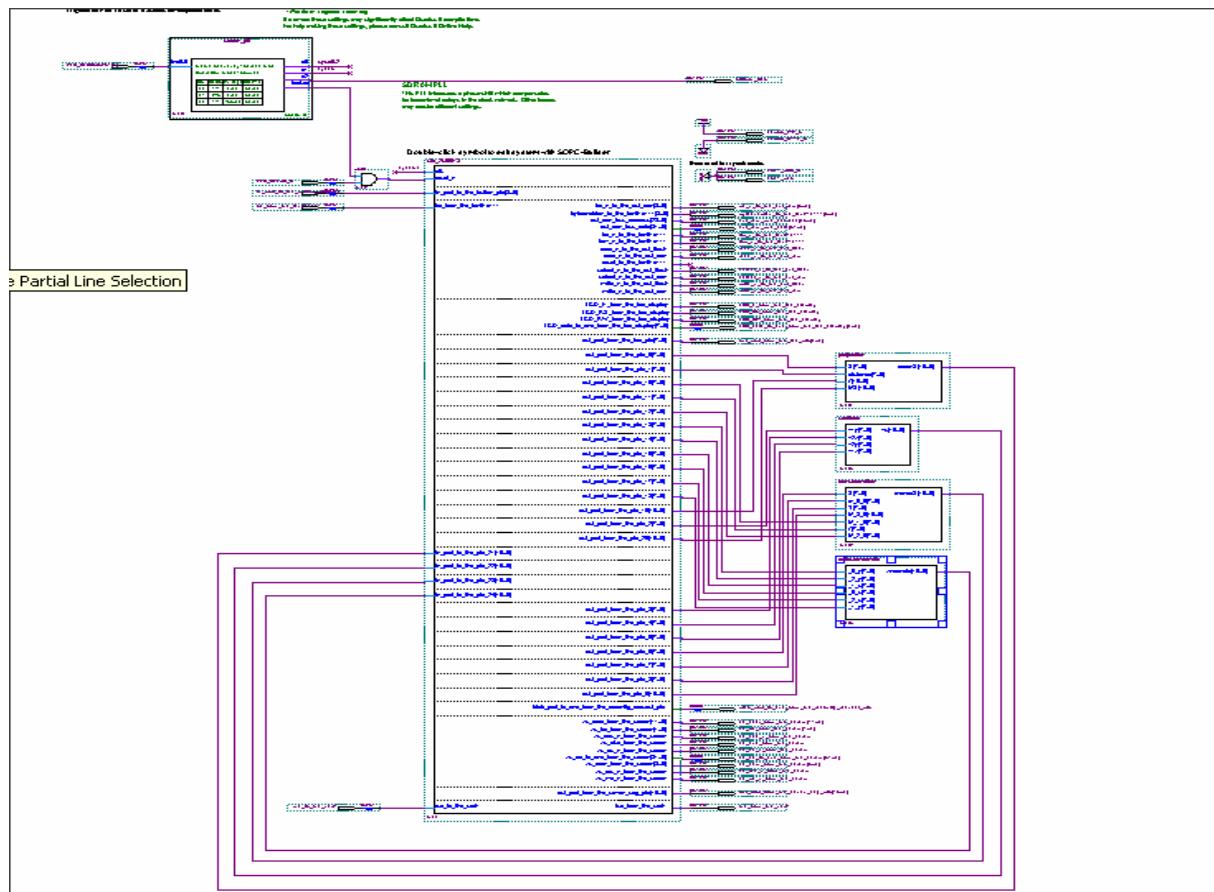

| 6.1- Création du système hardware .....                                                            | 82 |

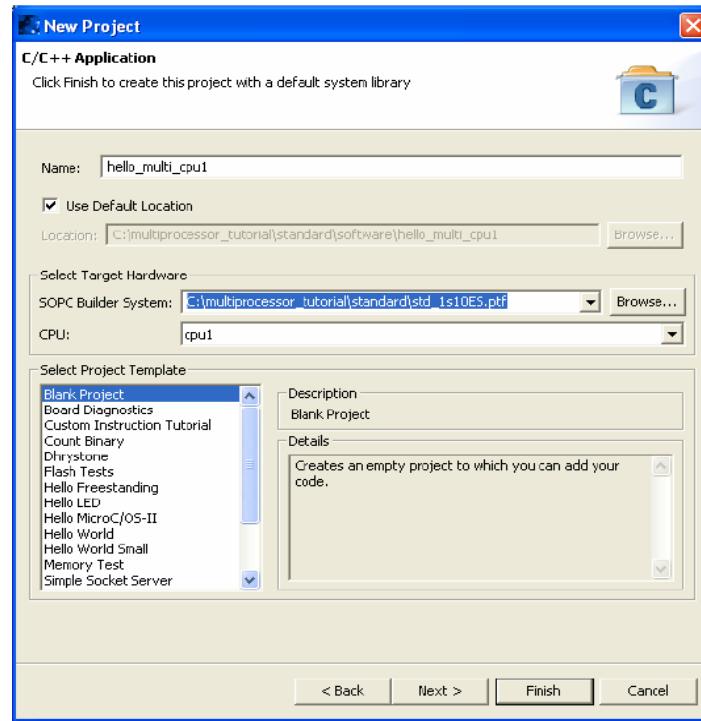

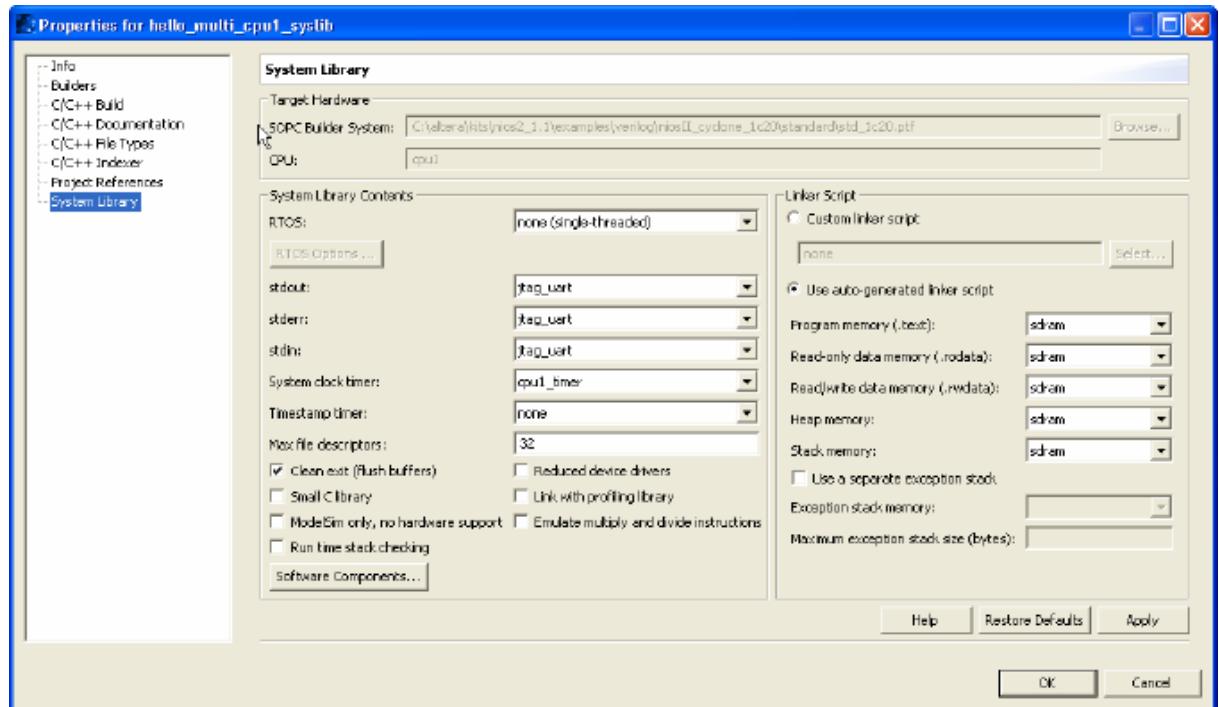

| 6.1.1- <i>Démarche à suivre pour la réalisation d'une plateforme multiprocesseurs</i> .....        | 82 |

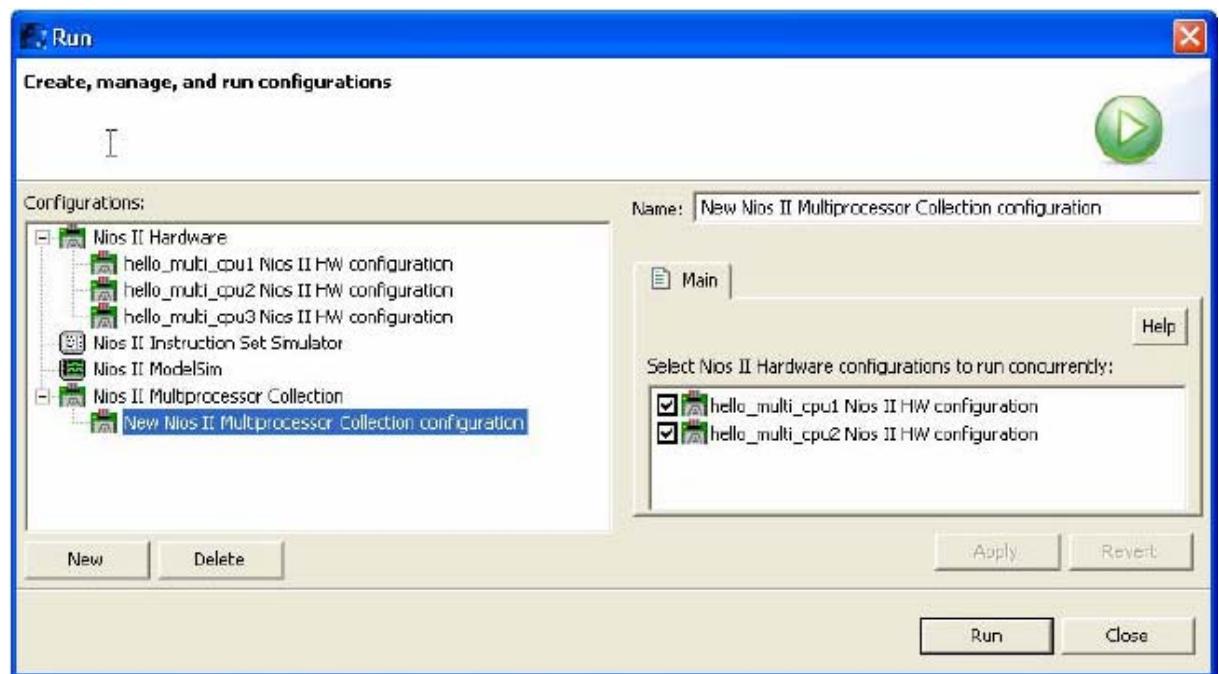

| 6.2- Développement de la partie software.....                                                      | 84 |

| 6.3- Exécution de l'application de traitement d'images 3D sur la plateforme multiprocesseurs ..... | 86 |

| 7- <i>Interprétation</i> .....                                                                     | 88 |

| 8- <i>Conclusion</i> .....                                                                         | 90 |

## **Conclusions et perspectives**

## **Bibliographie**

---

*Liste des figures*

---

|                                                                      |    |

|----------------------------------------------------------------------|----|

| Figure 1: architecture multiprocesseurs .....                        | 7  |

| Figure 2: architecture à mémoire partagée centralisée.....           | 11 |

| Figure 3: architecture à mémoire distribuée.....                     | 12 |

| Figure 4: architecture à mémoire distribuée partagée .....           | 13 |

| Figure 5: Etats d'une tâche.....                                     | 18 |

| Figure 6: Sémaphores binaires et compteur .....                      | 19 |

| Figure 7: Architecture d'un SE à micronoyau .....                    | 21 |

| Figure 8: Organisation de RTEMS.....                                 | 24 |

| Figure 9: Les éléments d'Ecos .....                                  | 28 |

| Figure 10: Gestion de processus par Micro-Kernel .....               | 29 |

| Figure 11: Structure de MicroC/OS-II .....                           | 41 |

| Figure 12: Carte de développement STRATIX II.....                    | 44 |

| Figure 13: Flot de conception logiciel et matériel.....              | 46 |

| Figure 14: Architecture monoprocesseur .....                         | 48 |

| Figure 15: Configuration de l'RTOS .....                             | 49 |

| Figure 16: Système multi masters .....                               | 50 |

| Figure 17: Architecture multiprocesseurs proposée.....               | 56 |

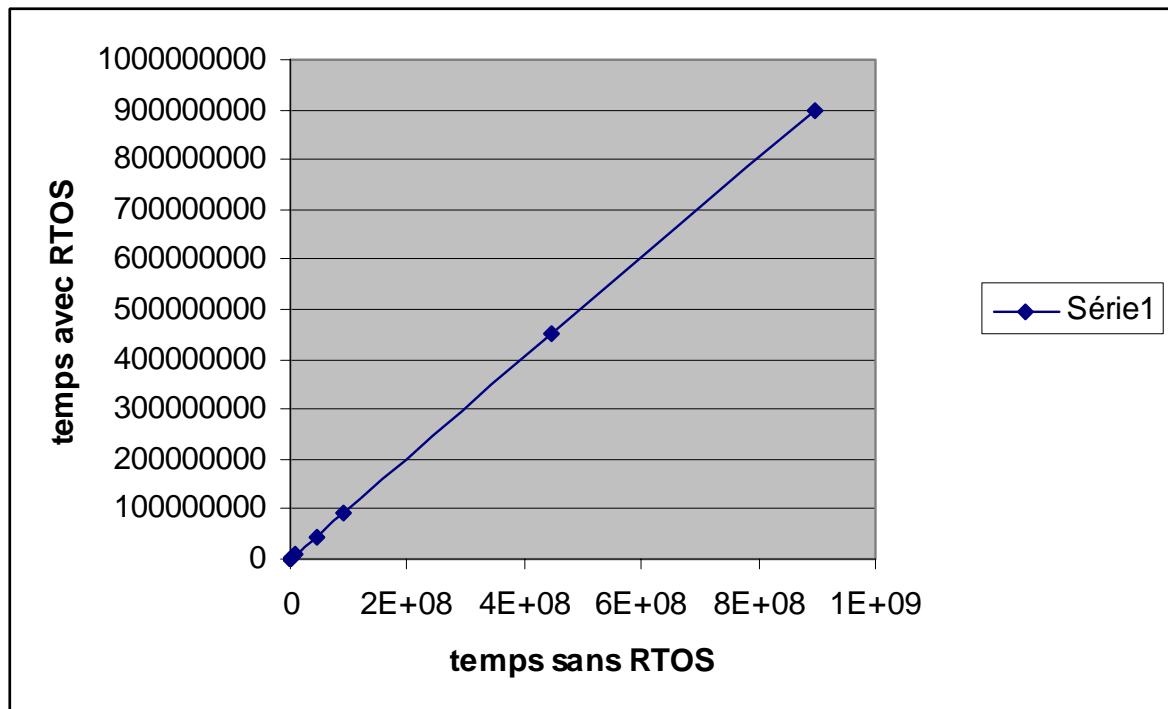

| Figure 18: Courbe d'estimation.....                                  | 59 |

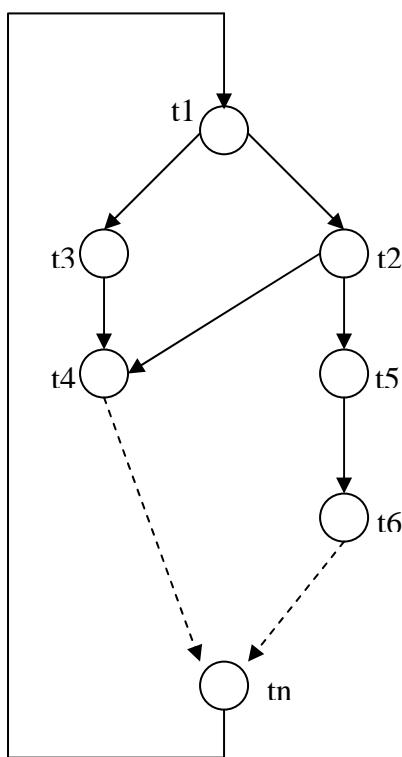

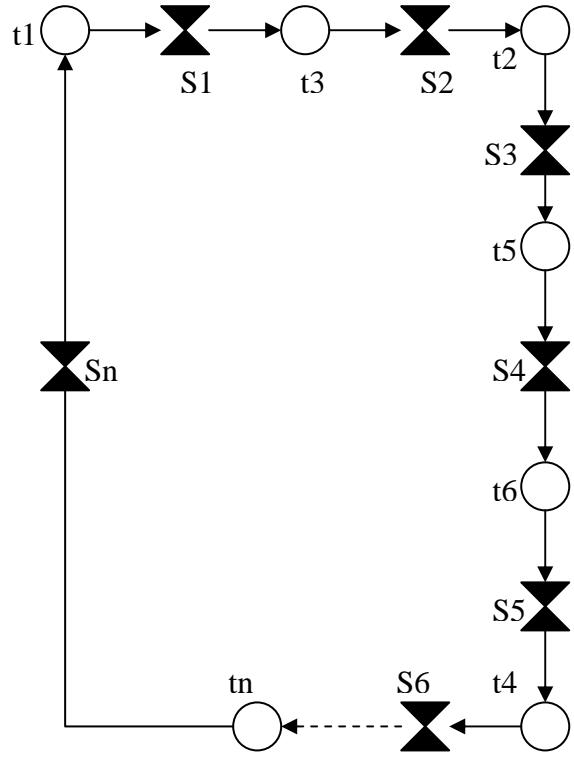

| Figure 19: Graphe de tâche      Figure 20: Graphe de séquence.....   | 62 |

| Figure 21: Diagramme de conception de pipeline .....                 | 66 |

| Figure 22: Test de visibilité d'une facette triangulaire .....       | 68 |

| Figure 23: Principe de la réflexion diffuse .....                    | 70 |

| Figure 24: Principe de la réflexion spéculaire.....                  | 71 |

| Figure 25: Clipping d'une figure.....                                | 72 |

| Figure 26: Principe de la projection .....                           | 72 |

| Figure 27: Application d'ombrage plat sur une sphère .....           | 73 |

| Figure 28: graphe de taches de l'application 3D .....                | 74 |

| Figure 29: Diagramme de séquence de l'application 3D .....           | 75 |

| Figure 30: Ajout des coprocesseurs .....                             | 77 |

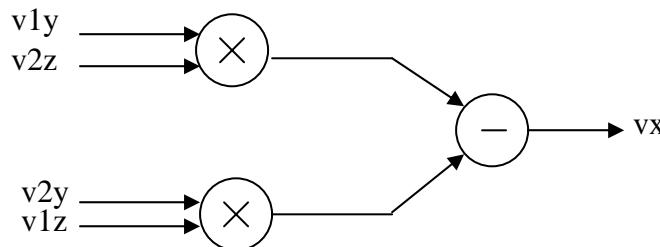

| Figure 31: Schéma bloc du module de calcul normal .....              | 78 |

| Figure 32: Schéma bloc du module de Projection.....                  | 78 |

| Figure 33: Schéma bloc du module du produit vectoriel .....          | 79 |

| Figure 34: Schéma bloc du module de transformation .....             | 79 |

| Figure 35: Schéma du système et des accélérateurs.....               | 81 |

| Figure 36: Conception du système par le SOPC Builder .....           | 83 |

| Figure 37: Choix du processeur .....                                 | 85 |

| Figure 38: Choix du timer .....                                      | 85 |

| Figure 39: Exécution sur une architecture multiprocesseurs .....     | 86 |

| Figure 40: Graphe de dépendance de données de l'application 3D ..... | 87 |

*Liste des tableaux*

---

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| Tableau 1: Comparaison entre une architecture à mémoire partagée et celle distribuée ..... | 12 |

| Tableau 2: Caractéristiques de QNXv6.1 .....                                               | 31 |

| Tableau 3: Caractéristiques de Windows CE .....                                            | 33 |

| Tableau 4: Registre de mutex .....                                                         | 51 |

| Tableau 5: Fonction du mutex .....                                                         | 52 |

| Tableau 6: Fonction du mailbox .....                                                       | 55 |

| Tableau 7: Mesure du temps d'exécution avec et sans RTOS .....                             | 58 |

| Tableau 8: Temps pris par les services du MicroC/OS-II .....                               | 61 |

| Tableau 9: Performances des architectures proposé .....                                    | 89 |

Avec le progrès de la capacité d'intégration de centaines de millions de transistors sur une seule puce et l'avancement au niveau de la conception des cœurs de processeurs embarqués deux tendances architecturales peuvent être distinguées.

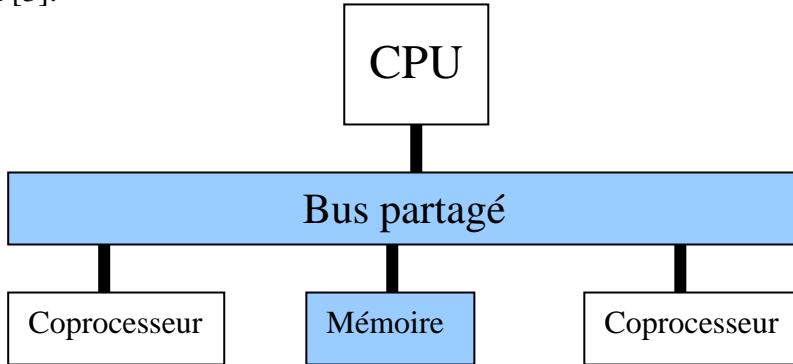

La première tendance consiste à développer une architecture monoprocesseur extensible par un ensemble de coprocesseurs ou/et accélérateurs matériels génériques ou dédiés [1,3]. Comme exemple d'architecture monoprocesseur on peut citer : Power PC, Intel Pentium 4, ST100, et beaucoup d'autres processeurs de type *VLIW*<sup>1</sup> ou super-scalaire [3]. Dans de telles architectures, la communication est basée sur le principe maître/esclaves : le *CPU*<sup>2</sup> est le maître mais les périphériques sont les esclaves. Les interfaces des co-processeurs sont généralement faites de registres transposés dans la mémoire du CPU et peuvent produire des interruptions au CPU. Ces communications se font généralement via un bus partagé (le bus mémoire du CPU). En terme de performance, de telles architectures centrées autour d'un seul CPU ont un inconvénient : la dégradation de performance engendrée par le fait que le processeur effectue la communication aussi bien que le calcul [3].

Figure 1: architecture multiprocesseurs

La deuxième tendance adresse des architectures multiprocesseurs. En effet, l'implémentation multiprocesseurs était réservée aux stations de calculs scientifiques [9, 10] et actuellement les systèmes embarqués sont adhérents. Ainsi, le fait de viser une implémentation multiprocesseurs de systèmes embarqués permet d'améliorer la réponse du système aux contraintes de performance et de faible consommation.

De très nombreux systèmes embarqués font appel à un ou plusieurs systèmes d'exploitation pour faciliter la gestion des événements et gérer la réactivité de ces systèmes.

<sup>1</sup> Very Long Instruction Word

<sup>2</sup> Central Processing Unit

En plus, et du fait de la complexité croissante de ces systèmes (exemple : Système sur puce), de la présence de fortes contraintes temps réel, de la limitation des ressources disponibles, tant en mémoire qu'en énergie disponible et donc en puissance de calcul, mais également de la pression exercée par le marché sur ces produits, l'usage de systèmes d'exploitation temps réel (*RTOS*<sup>3</sup>) est devenu nécessaire dans les systèmes embarqués. Des premiers travaux ont été élaborés dans notre équipe [1] afin de proposer un modèle de communication interprocesseur. Ce modèle a été étudié avec des primitives logicielles.

Parmi les objectifs de ce projet on cite l'implémentation d'un modèle sur une plateforme multiprocesseur d'une part et l'expérimentation d'un environnement de prototypage des systèmes réactifs/multiprocesseurs (Processeurs et *RTOS* embarqués), sur des architectures reconfigurables dans le cadre des Systèmes sur puce (*SoC*<sup>4</sup>) d'autre part. Cette plateforme a été utilisée afin d'évaluer les performances des systèmes sur puce temps réel en second lieu.

Ce rapport est organisé de la façon suivante :

Dans le premier chapitre, on présentera d'abord, une étude des différentes architectures multiprocesseurs qui existent, Puis on mettra en évidence les concepts de base des systèmes d'exploitation temps réel ainsi que quelques exemples de *RTOSs* embarqués les plus connus et on terminera ce chapitre par une étude de quelques outils d'estimation de performance dans le cadre des systèmes sur puce.

Dans le deuxième chapitre, on commencera d'abord par la présentation de notre plateforme de travail. Ensuite, on passera à la conception d'une architecture multiprocesseurs en utilisant des modules de communication inter processeur implémentés en hardware offert par Altera. On terminera ce chapitre par la génération d'un modèle d'estimation de performance pour les applications temps réel.

Dans le dernier chapitre, nous envisagerons, dans la première section, la description de l'application de traitements d'images 3D et la validation du modèle d'estimation proposé à travers cette application, et dans la deuxième section, la conception de *SoC* multiprocesseurs sur des architectures reconfigurables. Il s'agit en fait d'étudier les points clés liés à la conception d'un tel système multiprocesseurs, dans le cadre des *SoCs*. En effet, et vu les limites des *RTOS* embarqués, un modèle de communication inter processeur doit se mettre en place. Afin de valider ce modèle, un exemple de système multiprocesseurs a été réalisé à base de la plate-forme ALTERA autour du cœur de processeur « *NIOS* » et le bus on chip « *AVALON* ».

---

<sup>3</sup> *Real Time Operating System*

<sup>4</sup> *System on Chip*

# Chapitre 1

## 1- Introduction

Les nouvelles technologies s'orientent vers l'intégration sur une même puce de plusieurs processeurs, *DSP*<sup>5</sup>, *IP*<sup>6</sup> matériels et logiciels, mémoires, bus partagés, etc. Nous parlons ainsi de systèmes multiprocesseurs mono puce (*MPSoC*<sup>7</sup>). En fait, les systèmes multiprocesseurs sont l'une des solutions pour répondre à la complexité croissante des systèmes intégrés utilisés pour des applications telles que les applications multimédia.

Pour ce faire, depuis plusieurs années, des systèmes d'exploitation temps réel sont utilisés dans les architectures multiprocesseurs sur puce vu que la présence des RTOS permet de structurer et de simplifier la programmation de la partie logicielle d'un tel SoC.

Ce chapitre est organisé comme suit :

La première partie est consacrée pour la présentation des différentes topologies possibles pour la réalisation d'une plateforme multiprocesseurs.

Dans la deuxième partie de ce chapitre, nous décrirons les concepts de base des systèmes d'exploitation temps réel, puis nous présentons les caractéristiques de quelques RTOS utilisés dans le cadre des systèmes sur puce.

La troisième partie présentera un état de l'art sur les différents outils d'estimation du temps d'exécution existant ainsi que notre contribution.

## 2- Taxonomie d'architectures multiprocesseurs

### 2.1- Les systèmes à mémoire partagée (Shared-memory systems)

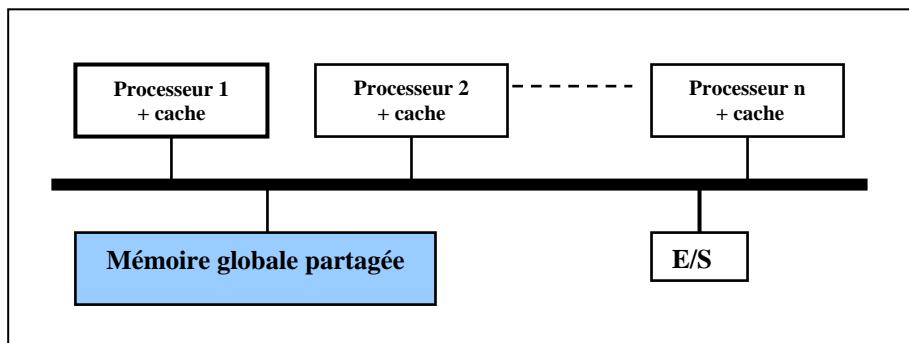

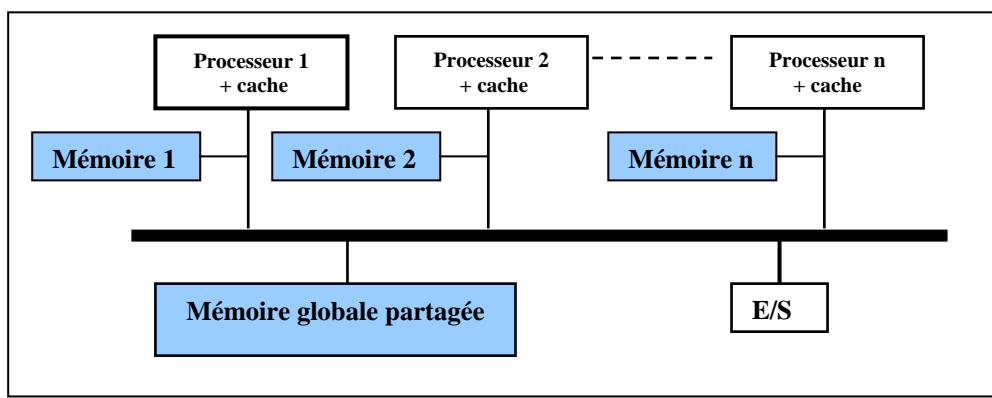

Les machines du premier groupe que nous appelons les architectures à mémoire partagée centralisée Figure 2, ont au maximum quelques douzaines de processeurs au milieu des années 90. Les multiprocesseurs avec un faible nombre de processeurs peuvent se partager une mémoire centralisée unique et un bus pour interconnecter les processeurs et la mémoire [1]. Avec de gros caches, le bus et la mémoire unique peuvent satisfaire les besoins mémoire d'un petit nombre de processeurs. Puisqu'il y a une seule mémoire principale avec un temps d'accès uniforme pour chaque processeur, ces machines sont parfois appelées *UMA*<sup>8</sup> pour Accès Mémoire Uniforme. Ces systèmes offrent un modèle de programmation général et

---

<sup>5</sup> *Digital Signal Processor*

<sup>6</sup> *Intellectual Properties*

<sup>7</sup> *MultiProcessor System on Chip*

<sup>8</sup> *Uniform Memory Access*

« *commode* » permettant un partage simple des données, à travers un mécanisme uniforme de lecture et d'écriture des structures partagées dans la mémoire globale.

La facilité et la portabilité de la programmation sur de tels systèmes réduisent considérablement le coût de développement des applications parallèles. Par contre, ces systèmes souffrent d'un handicap qui est la grande latente pour l'accès à la mémoire, ce qui rend la flexibilité (l'extensibilité de l'architecture pour d'autres applications) assez limitée. Ce type d'architecture à mémoire partagée centralisée reste de loin l'organisation la plus populaire actuellement dans les multi-ordinateurs distribués sur réseau.

Figure 2: architecture à mémoire partagée centralisée

## 2.2- Les systèmes à mémoire distribuée (*distributed memory system*)

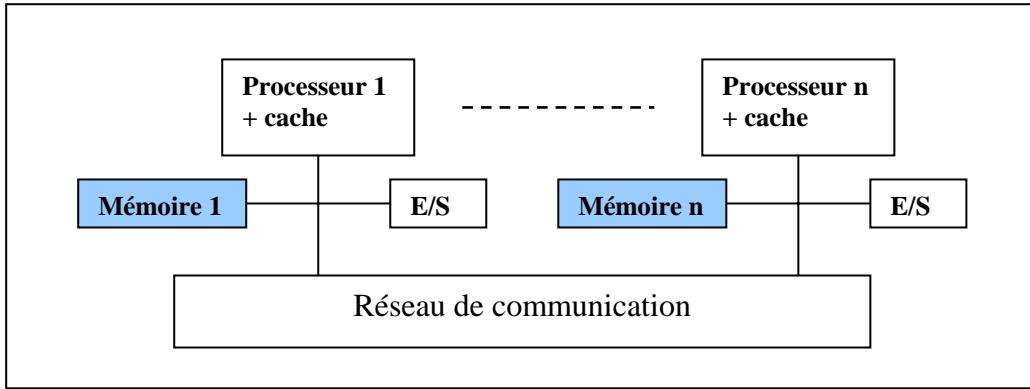

Ces systèmes sont souvent appelés « *les multi-ordinateurs* ». Ils sont constitués de plusieurs nœuds indépendants. Chaque nœud consiste en un ou plusieurs processeurs et de la mémoire centrale. Les nœuds sont connectés entre eux en utilisant des technologies d'interconnexion extensibles (scalable) Figure 3. Ces systèmes sont dits aussi machines à architecture de type *NUMA*<sup>9</sup>, car en pratique, dans un réseau de stations de travail, l'accès à la mémoire locale de la station est nettement plus rapide que celui à la mémoire d'une station distante via le réseau [1].

La nature flexible de tels systèmes, les rend d'une très grande capacité de calcul. Mais, la communication entre des processus résidents dans des nœuds différents nécessite l'utilisation de modèles de communication par passage impliquant un usage explicite de primitives du type *Send/Receive*[8]. En optant pour ce type de systèmes, le concepteur doit particulièrement faire attention à la distribution des données ainsi qu'à la gestion des communications (le transfert des processus pose un important problème à cause des différents espaces d'adressage, c'est-à-dire deux variables distinctes peuvent avoir la même adresse

<sup>9</sup> Non Uniform Memory Access

logique et deux adresses physiques différentes). Ainsi, les problèmes logiciels, contrairement aux problèmes matériels sont relativement complexes dans les systèmes à mémoire distribuée.

Figure 3: architecture à mémoire distribuée

### 2.3- Comparaison entre un système à mémoire partagée et celui à mémoire distribuée

Le tableau suivant récapitule les différences essentielles entre les architectures à mémoire partagée et celles à mémoire distribuée. Nous constatons que la communication entre les processeurs est plus simple dans les systèmes à mémoire distribuée. En effet, ce type de systèmes est utilisé pour un nombre élevé de processeurs contrairement aux systèmes à mémoire partagée.

| Architecture à mémoire partagée                                                      | Architecture à mémoire distribuée                                  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Temps d'accès à la mémoire uniforme pour tous les processeurs (UMA)                  | Temps d'accès dépendant de la position du mot de donnée en mémoire |

| Petit nombre de processeurs                                                          | Grand nombre de processeurs                                        |

| Communication des données entre processeurs assez complexe                           | Communication facile entre processeurs                             |

| Les processeurs disposent généralement de plusieurs niveaux de cache (ou gros cache) | Processeurs avec des caches ordinaires                             |

| Architectures d'une flexibilité limitée                                              | Architectures flexibles                                            |

| Processeurs interconnectés par bus                                                   | Processeurs interconnectés par réseau d'interconnexion             |

| Grande mémoire physiquement centralisée                                              | Petites mémoires physiquement distribuées                          |

Tableau 1: Comparaison entre une architecture à mémoire partagée et celle distribuée

## 2.4- Les systèmes à mémoire distribuée partagée

Un concept relativement nouveau, qui est la mémoire distribuée partagée, combine les avantages des deux approches. Un système *DSM*<sup>10</sup> implante (logiquement) un système à mémoire partagée sur une mémoire physiquement distribuée. Ces systèmes préservent la facilité de programmation et la portabilité des applications sur des systèmes à mémoire distribuée, sans imposer pour autant la gestion des communications par le concepteur. Les systèmes DSM, permettent une modification relativement simple et une exécution efficace des applications déjà existantes sur des systèmes à mémoire partagée, tout en héritant de la flexibilité des systèmes à mémoire distribuée [1].

Figure 4: architecture à mémoire distribuée partagée

Un système multiprocesseurs avec mémoire distribuée partagée est généralement constitué d'un ensemble de nœuds (clusters), connectés par un réseau d'interconnexion Figure4. Un nœud peut être soit un simple processeur ou une hiérarchie qui cache une autre architecture multiprocesseurs, souvent organisée autour d'un bus partagé. Les caches privés aux processeurs sont d'une grande importance afin de réduire la latente. Chaque nœud possède un module de mémoire local (physiquement), faisant partie du système DSM global, ainsi qu'une interface le connectant au système.

## 3- Système d'exploitation temps réel

### 3.1- RTOS et contrainte temps réel

Un système est dit temps réel lorsqu'il est soumis à des contraintes de temps et qu'il y répond dans un intervalle acceptable. Il n'est pas nécessairement rapide, tout dépend des contraintes imposées par l'application [1, 2].

<sup>10</sup> *Distributed shared Memory*

Parmi l'ensemble des systèmes temps réels existants, nous distinguons deux grandes familles: les systèmes à contraintes souples et les systèmes à contraintes dures [36].

### **3.1.1- Systèmes à contraintes souples**

Ils acceptent des variations de durée quant aux traitements des données. Un système de visioconférence, par exemple, est de ce type. Avec ce type de système, il est souhaitable que les images soient affichées à une cadence de 30 images par seconde. Cependant, si l'ensemble du système subit une forte charge de travail, certaines images pourront être supprimées afin de garder une cohérence avec le son.

### **3.1.2- Systèmes à contraintes dures**

Ils n'acceptent aucun compromis sur la durée de traitement des données. Ce type de système se trouve, par exemple, dans les centrales nucléaires. Si un réacteur vient d'avoir un disfonctionnement, le système devra être capable de déclencher un processus de sécurité dans un délai extrêmement court.

En outre, pour le système de gestion des airbags dans une voiture, il possède des contraintes temps réel très importantes. En fait, quand un capteur détecte une déformation de la carrosserie, il envoie un signal au contrôleur qui doit avoir gonflé les airbags dans les 10 ms sous peine d'arriver trop tard, ce qui aurait des conséquences désastreuses pour les occupants de la voiture. Même si un capteur tombe en panne et qu'il n'envoie plus d'informations, le système doit continuer à fonctionner et fournir les meilleures réponses possibles.

## **3.2- Caractéristiques d'un RTOS**

Un système d'exploitation temps réel doit s'affranchir des incertitudes sur le temps. Si une tâche ne peut être effectuée immédiatement, elle devra l'être au bout d'un temps «  $t$  » connu.

Un tel système possède donc la caractéristique d'être déterministe. Il apporte aussi les services suivants :

- Communication;

- Synchronisation;

- Gestion et ordonnancement des tâches;

- Gestion de la mémoire et du temps;

- Gestion des interruptions et des entrées/sorties physiques.

### 3.3- Concepts de base d'un RTOS

Dans ce paragraphe, nous rappelons quelques concepts clés concernant les systèmes d'exploitation temps réel [38]:

#### 3.3.1- *Section critique*

Une section critique de code (appelée aussi une région critique) doit être traitée continuellement. Une fois, la section de code commence l'exécution, elle ne devra pas être interrompue. Afin d'assurer cela, les interruptions sont généralement désactivées avant que le code critique ne soit exécuté mais on les activera de nouveau quand le code sera achevé

#### 3.3.2- *Ressource partagée et exclusion mutuelle*

Une ressource partagée est un objet qui peut être utilisé par plusieurs parties du programme. Cette ressource peut être un registre, une variable, une structure de données, ou quelque chose physique comme un LCD, ou un beeper.

Si deux parties séparées ont besoin de la même ressource, on devra gérer cela par l'exclusion mutuelle. A chaque fois, qu'une partie du programme veut utiliser une ressource partagée, il faudrait obtenir un accès exclusif à cette ressource afin d'éviter le conflit.

#### 3.3.3- *Tâche*

##### 3.3.3.1- *Multi-tâches*

Le multitâche maximise l'utilisation du CPU, et fournit une construction modulaire des applications. En plus, il permet au programmeur de l'application de gérer la complexité inhérente dans les applications temps réel. Les programmes d'application sont typiquement plus faciles à concevoir et à maintenir si le multitâche est mis en œuvre.

Un système temps réel multitâche doit avoir les caractéristiques suivantes [3] :

- Plusieurs tâches doivent être exécutées périodiquement et à des intervalles différents;

- Une tâche peut s'exécuter avec une faible priorité de façon à garantir les contraintes de temps des autres tâches.

- Une tâche peut communiquer de l'information à une autre.

##### 3.3.3.2- *Ordonnancement*

###### 3.3.3.2.1- *Ordonnancement préemptif*

La préemption se produit quand une tâche jugée plus prioritaire que la tâche courante apparaît et devient éligible pour s'exécuter. Tant que la préemption peut se produire à tout moment, elle exige donc l'utilisation des interruptions et la gestion de la pile pour garantir l'exactitude du changement de contexte. Par une neutralisation temporaire de la préemption, les programmeurs peuvent empêcher les ruptures non désirées dans leurs programmes pendant les sections critiques du code [5].

L'ordonnancement préemptif est très « *stack-intensive* ». En fait, l'ordonnanceur maintient une pile séparée pour chaque tâche. Ainsi, quand une tâche suspendue reprend l'exécution après le changement de contexte, toutes les valeurs de la pile, uniques et propres pour cette tâche, sont remises en place. Elles sont généralement les adresses de retour des appels des sous-routines, les paramètres et les variables locales.

### **3.3.3.2.2- *Ordonnancement coopératif***

L'ordonnanceur coopératif est susceptible d'être plus simple que celui préemptif. Comme les tâches devraient toutes se coopérer pour que le changement de contexte se produise, l'ordonnanceur est alors moins dépendant des interruptions, et il peut être plus petit et potentiellement plus rapide. En plus, les programmeurs connaissent exactement quand les changements de contexte vont se produire, et peuvent donc protéger les régions critiques du code [5].

En le comparant avec l'ordonnanceur préemptif, l'ordonnanceur coopératif possède certains avantages tels que sa simplicité relative, son contrôle total au changement de contexte et un temps de réponse de l'interruption plus court.

### **3.3.3.3- *Changement de contexte***

Quand un noyau décide d'exécuter une autre tâche, il sauvegarde simplement le contexte de la tâche courante (registres du CPU) dans sa propre pile. Une fois cette opération est effectuée, le contexte de la nouvelle tâche reconstituée de sa zone de stockage reprend alors l'exécution de son code. Ce processus est appelé un changement de contexte (*Context Switch*). Ce contexte représente l'état du processeur à un moment donné [4]:

- **Registre:** La tâche suspendue devra pouvoir continuer son exécution sans être affectée. La première opération à effectuer est la sauvegarde de l'état du processeur au moment de la suspension. Le noyau possède pour chaque tâche non dormante un espace mémoire réservé à cet effet.

- Pile: Les données temporaires utilisées par la tâche suspendue doivent être préservées lors des opérations de la nouvelle tâche active. Ces données sont organisées sous la forme d'une pile contenant le contexte (adresse de retour, valeur des registres), des appels de sous-routines et les variables temporaires de ces sous-routines.

### 3.3.3.4- Structure d'une tâche

Généralement, une tâche est une opération qui a besoin de se produire à plusieurs reprises dans l'application. La structure est réellement très simple. Elle se compose d'une initialisation optionnelle et d'une boucle infinie qui se répète inconditionnellement.

Avec un ordonnanceur préemptif, une tâche peut se voir comme suit [5]:

```

Initialize() ;

For (;;)

{

.....

}

```

**Structure d'une tâche pour un multitâche préemptif**

Quant à l'utilisation d'un ordonnanceur coopératif, une tâche peut se voir comme suit:

```

Initialize() ;

For (;;)

{

.....

TaskSwitch();

}

```

**Structure d'une tâche pour un multitâche coopératif**

La seule différence entre les deux versions est le besoin d'exiger explicitement le changement de contexte dans la version coopérative. Dans le multitâche coopératif, chaque tâche décide elle-même d'abandonner le contrôle du processeur pour une autre tâche.

Mais, dans le multitâche préemptif, l'ordonnanceur procède à un changement de contexte juste à l'apparition d'une tâche de priorité plus élevée éligible pour s'exécuter. Nous pouvons noter aussi que les changements de contextes peuvent se produire à des temps multiples à l'intérieur d'une tâche, dans les deux types de systèmes coopératifs et préemptifs.

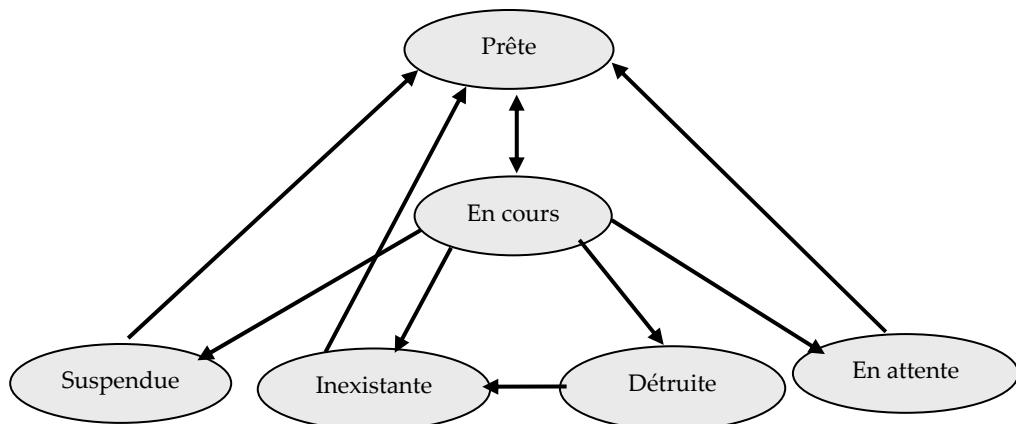

### 3.3.3.5- Etat d'une tâche

Un RTOS maintient chaque tâche dans un état bien défini. La figure 5 illustre les différents états qu'une tâche peut être dedans, et les transitions permises entre les différents états [18].

Figure 5: Etats d'une tâche

- Avant qu'une tâche ne soit créée, elle est dans un état « *Inexistante* ». Elle retournera à cet état quand elle sera détruite.

- Une tâche « *Prête* » est à l'état prêt pour s'exécuter, mais elle ne le peut pas car elle n'est pas la tâche la plus prioritaire. Elle devra donc rester dans cet état jusqu'à ce que l'ordonnanceur détermine quelle est la plus prioritaire et la bascule à l'état « *En cours* ».

- Une tâche « *En cours* », c'est à dire en cours d'exécution, devra retourner à l'état éligible après un simple changement de contexte. Mais, elle peut transiter vers un autre état si la tâche appelle un service de RTOS qui détruit, stoppe, retarde, ou fait attendre la tâche.

- Une tâche « *Suspendue* » est une tâche qui était précédemment en cours d'exécution, mais maintenant elle est suspendue et en attente de l'expiration du « *delay timer* ». Une fois, le temporisateur associé est expiré, le système d'exploitation bascule la tâche à l'état « *Prêt* ». Nous pouvons ainsi noter que les tâches périodiques sont susceptibles d'être « *Suspendue* » à tout instant particulier.

- Une tâche « *Inexistante* » est précédemment en cours d'exécution, et elle sera par la suite suspendue indéfiniment. Elle ne sera recommandée que via un appel d'un service RTOS permettant de provoquer sa régénération.

- Une tâche « *Bloquée* » est suspendue ; elle restera en attente jusqu'à la production de l'événement désiré.

### 3.3.4- Communication entre tâches

Un RTOS fournit diverses méthodes pour faire communiquer les tâches entre elles. Dans le multitâches à base d'événements, et pour qu'une tâche réagisse à un événement, ce dernier doit déclencher une sorte de communication avec la tâche.

Les tâches peuvent aussi coopérer l'une avec l'autre par divers outils de communication comme les sémaphores, les messages, et les queues de messages. Ainsi nous distinguons deux principales actions [18]:

- Signalisation; appelée aussi envoi (*Posting*).

- Attente; appelée aussi réception (*Pending*).

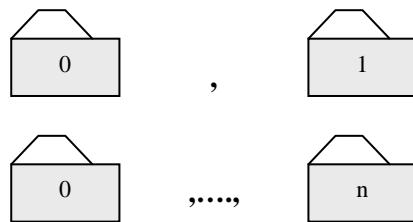

### 3.3.4.1- *Sémaphores*

Il y a deux types de sémaphores : les sémaphores binaires (*Binary Semaphore*) et les sémaphores compteurs (*Counting Semaphore*). Un semaphore binaire peut prendre uniquement deux valeurs, 0 ou 1. Un semaphore compteur peut prendre une gamme de valeurs basées sur sa taille. Par exemple, la valeur d'un semaphore compteur à 8 bits peut s'étendre de 0 à 255. Il peut aussi être à 16 ou 32 bits. Les sémaphores et leurs valeurs se présentent généralement de la façon suivante figure 6 :

Figure 6: Sémaphores binaires et compteur

### 3.3.4.2- *Messages*

Les messages fournissent un moyen arbitraire d'envoi d'informations à une tâche. L'information peut être un nombre, une chaîne, un tableau, une fonction, un pointeur, ou toute autre chose. Comme avec les sémaphores, le système d'exploitation fournit le moyen pour créer, signaler, et attendre les messages.

Actuellement, le contenu du message n'est pas l'information elle-même, mais plutôt un pointeur indiquant l'emplacement de l'information. Quand un message est initialisé d'être vide, il contient donc un pointeur nul, qui ne pointe à aucune chose.

### 3.3.4.3- *Files de communication (message queue)*

Les files de messages sont une extension de messages. Une queue de messages peut contenir des messages multiples (jusqu'à un nombre prédéterminé) à tout moment. L'envoi des messages peut continuer jusqu'à ce que la boîte de messages soit pleine. La réception aussi peut continuer jusqu'à ce qu'elle soit vide.

Un RTOS aura besoin d'allouer une certaine *RAM*<sup>11</sup> additionnelle pour gérer chaque queue de messages. Cette RAM sera utilisée pour garder la trace du nombre de messages dans la queue, et l'ordre dans lequel les messages sont envoyés.

### 3.4- Conflits

Une variété de conflits peut se produire dans un environnement multitâche. Les plus connus sont les suivants: l'interblocage et l'inversion des priorités [5].

#### 3.4.1- *Interblocage (Deadlock)*

Le « *Deadlock* » se produit avec deux ou plusieurs tâches, quand chaque tâche est en attente sur une ressource contrôlée par une autre. Cette ressource resterait non disponible indéfiniment. Les tâches en attente seront donc abouties à une impasse. La solution, pour toutes les tâches désirant acquérir des ressources, est de :

- Acquérir souvent des ressources dans un ordre prédéterminé.

- Acquérir toutes les ressources avant de continuer.

- Libérer les ressources dans un ordre opposé.

En utilisant un « *timeout* », nous pouvons éviter le « *Deadlock* ». En fait, en essayant d'obtenir la ressource, une période de temps optionnelle peut être spécifiée. Si la ressource n'est pas acquise dans une telle période de temps, la tâche continue mais avec un code d'erreur indiquant que le temps d'attente de la ressource a expiré.

#### 3.4.2- *Inversions des priorités*

Les inversions de priorité se produisent quand une tâche de haute priorité est en attente sur une ressource commandée par une autre de basse priorité. La tâche la plus prioritaire devra attendre jusqu'à ce que la tâche de basse priorité libère la ressource, sur laquelle elle peut continuer. Pour ce, la priorité de la tâche la plus prioritaire doit être réduite à celle de la tâche de basse priorité.

Il y a une variété de méthodes pour éviter ce problème (exemple, transmission prioritaire). La méthode la plus pratique consiste à changer dynamiquement la priorité de la tâche qui commande une ressource. Cette méthode est donc basée sur les priorités des tâches désirant acquérir cette ressource [18].

---

<sup>11</sup> Random Access Memory

### 3.5- Systèmes d'exploitation dans les systèmes embarqués

L'usage de systèmes d'exploitation est nécessaire dans les systèmes embarqués, du fait de la complexité croissante de ces systèmes (exemple : Systèmes sur puce), de la présence de fortes contraintes temps réel, de la limitation des ressources disponibles, tant en mémoire qu'en énergie disponible et donc en puissance de calcul, mais également de la pression exercée par le marché sur ces produits. En effet, le temps de développement doit être raisonnable, afin de limiter le temps de mise sur le marché (*time to market*), et permet ainsi d'assurer le succès du produit.

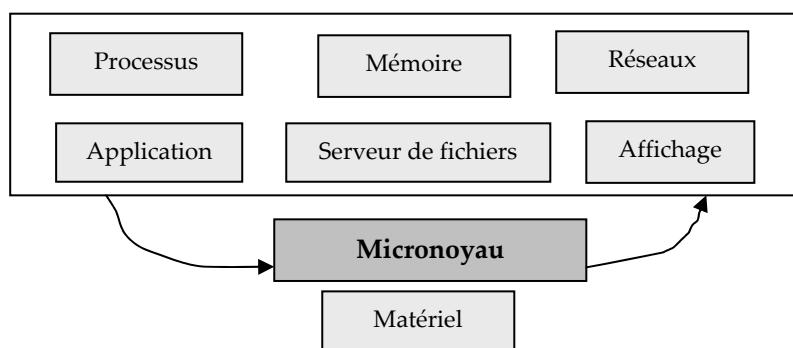

Les systèmes d'exploitation à micronoyaux sont mieux adaptés aux systèmes embarqués [9]: la tolérance aux fautes doit être forte, car les conditions environnementales ne sont pas toujours optimales (exemple: systèmes pour l'automobile ou l'industrie). Ceci est permis par la possibilité de redondance, ainsi que le confinement des erreurs, qui est bien meilleur dans un système d'exploitation à micronoyau que dans un système d'exploitation plus classique. Par ailleurs, il est également possible de charger dynamiquement les modules à exécuter, ainsi que de les distribuer, ce sont des besoins forts pour ce type de système. La figure 7 montre l'architecture d'un tel système d'exploitation.

Quelques exemples d'implémentation de Systèmes d'Exploitation pour Systèmes Embarqués [9]:

- *Inferno* (Lucent) : avec sécurité intégrée,

- *VxWorks*, version générique,

- *VxWorks*, pour l'automobile,

- *VxWorks*, pour l'électronique grand public,

- *VxWorks*, pour l'industrie,

- *pSOS Systems*,

- *Lynx Real-Time Systems (LynxOS)*.

Figure 7: Architecture d'un SE à micronoyau

Parmi les Systèmes d'Exploitation pour les Systèmes Embarqués, nous distinguons les systèmes d'exploitation temps réel (RTOS) qui se caractérisent par la présence de contraintes temps réel.

### **3.5.1- Caractéristiques des RTOS pour les systèmes embarqués**

Les caractéristiques essentielles d'un RTOS pour les systèmes embarqués sont:

- La première caractéristique des RTOS est son temps de réponse prévisible à un stimulus externe [13]. Un tel système possède donc la caractéristique d'être déterministe.

- Un RTOS doit s'affranchir des incertitudes sur le temps. Si une tâche ne peut être effectuée immédiatement, elle le devra au bout d'un certain temps «  $t$  » connu [14].

- Si un périphérique génère une interruption, le RTOS doit répondre et démarrer le service à l'intérieur d'une période de temps connu, et ce, peu importe la charge du processeur sur lequel s'exécute le RTOS [13].

- Dans l'industrie, on s'entend dire de façon générale qu'un OS est RTOS lorsque le changement de contexte et le temps de réponse à une interruption sont garantis à l'intérieur d'une période de 10  $\mu$ s [13].

- Finalement, un bon RTOS doit aussi supporter les mécanismes d'un OS distribué (permet ainsi l'exploitation des systèmes temps réel distribués), mécanismes d'ordonnancement [15] (préemptif, non préemptif ou coopératif), précision de l'horloge et des minuteries, les outils de visualisation, et la compatibilité POSIX.

### **3.5.2- Importance des RTOS pour les systèmes embarqués**

Depuis plusieurs années des systèmes d'exploitation temps réel (RTOS) sont introduits dans les architectures embarquées [13] monoprocesseurs et multiprocesseurs, telles que les architectures réactives embarquées afin de gérer la réactivité du système. En fait, la présence d'un RTOS permet de:

- Structurer et simplifier la programmation de la partie logicielle du SoC. En effet, le RTOS gère lui-même le matériel et propose aux applications logicielles des fonctions d'accès de haut niveau. Ainsi, le travail du programmeur d'application est soulagé de la programmation des accès au matériel.

- Utiliser des spécificités des processeurs. En effet, Les systèmes d'exploitation spécialement programmés pour le processeur sur lequel ils vont s'exécuter, peuvent tirer parties de ses spécificités en ce qui concerne le mécanisme d'interruption, les instructions de réduction de consommation et de gestion de cache [16].

- Et le réutiliser comme un IP logiciel dans les systèmes embarqués.

Grâce au RTOS, la réutilisation du point de vue logiciel peut se faire à plusieurs niveaux [13]:

- Gestion des tâches dans un système temps réel multitâches (notion de priorité, ordonnancement, changement de contexte, etc.);

- gestion des interruptions et des entrées/sorties physiques;

- gestion du temps (minuteries);

- gestion des communications entre tâches;

- gestion de la mémoire, etc.

### **3.5.3- *Limites des RTOS dans les systèmes embarqués***

Il est courant d'utiliser un système d'exploitation temps réel dans un tel système embarqué comme étant une structure logicielle permettant de gérer l'exécution complète de plusieurs tâches concurrentes sur le même système. Cependant, et bien que cette méthode soit couramment employée dans les systèmes embarqués spécifiques, celle-ci peut entraîner certains inconvénients en terme de coût, consommation et performances. Parmi ces limites, nous citons [16] :

- Les systèmes d'exploitation consomment de la mémoire. En plus, ils sont spécifiques au processeur sur lequel ils s'exécutent.

- Les impératifs de performances empêchent souvent l'utilisation d'interfaces génériques abstraites, et la multitude des systèmes d'exploitation et des architectures sont des freins à l'uniformité des interfaces.

- La généralité du système d'exploitation vis à vis de l'application faite est qu'il soit souvent plus volumineux que nécessaire. C'est un défaut important dans le monde des systèmes embarqués où la mémoire est limitée.

- La vitesse du système d'exploitation est aussi limitée par l'ordonnancement dynamique des tâches qui demande du temps aussi bien pour la décision que pour le passage d'une tâche à l'autre.

- Les systèmes d'exploitation peuvent être non déterministes : En fait, il est souvent impossible de savoir, avant utilisation, si une application basée sur un système d'exploitation respectera des délais ou non.

## 4- Quelques exemples de noyaux embarqués

Nous présentons dans la suite de cette section deux systèmes d'exploitation embarqués pour chaque catégorie. Nous rappelons ainsi les caractéristiques, et les services de chacun de ces systèmes d'exploitation. Cette étude est inspirée de [1].

### 4.1- RTEMS

RTEMS<sup>12</sup> est un noyau temps réel qui fournit de hautes performances pour les applications embarquées militaires. En plus, de point de vue code, il est très complet et assez lourd par rapport à certains autres RTOS. En fait, le taux d'occupation de cet RTOS est généralement très grand (200Mo). Les architectures supportant RTEMS sont les suivantes : M68k, Coldfire, Hitachi SH, Intel i386, Intel i960, MIPS, PowerPC, SPARC, AMD A29k et HP PA-RISC.

#### 4.1.1- Architecture interne de RTEMS

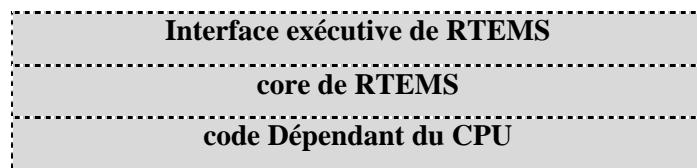

Comme indiqué dans la figure 8, RTEMS peut être envisagé comme un ensemble de composants superposés en couches qui travaillent en harmonie pour produire un ensemble de services pour des applications temps réel.

L'interface exécutive de l'application est formée par des groupes de directives constituant *le manager de ressources*. Les fonctions utilisées par les différents managers tels que l'ordonnanceur (*scheduler*), le partitionneur (*dispatcher*), et la gestion de l'objet sont intégrées dans le noyau exécutif. Ce dernier est en relation avec le « *code dépendant du CPU* ».

Figure 8: Organisation de RTEMS

#### 4.1.2- Architecture d'une application RTEMS

RTEMS se sert d'un Bridge (pont) entre les deux couches critiques : celle de l'architecture matérielle cible et celle du code de l'application dépendante. La plupart des

<sup>12</sup> Real Time Executive for Multiprocessors Systems

opérations matérielles dépendantes de l’application temps réel peuvent être localisées dans la couche la plus basse du gestionnaire des périphériques.

Le manager de l’interface I/O de RTEMS présente un outil efficace pour l’incorporation des dépendances matérielles dans le système en fournissant un mécanisme général au code de l’application qui y accède. Un système temps réel bien conçu peut bénéficier de cette architecture en construisant une bibliothèque riche en composants pouvant être utilisée dans d’autres applications ou projets temps réel.

#### 4.1.3- Services de RTEMS

- Les services primaires : Erreur Fatale, Initialisation, Tâche, horloge et temporisateur, Interruption ;

- Les services de Communication et de Synchronisation : Signal, Sémaphore, Message et Evénement ;

- Le multiprocessing ;

- I/O;

- Rate Monotonic;

- Les services de mémoire : Partition, Région, Dual-ported memory et I/O ;

#### 4.1.4- Ordonnancement

L’ordonnanceur de RTEMS utilise l’un des algorithmes suivants :

- A base de priorité (*priority-based*),

- Préemptif,

- Méthode de tourniquet (*round-robin*),

- Par partage de temps (*Time slicing*).

Il est à noter que l’ordonnanceur de RTEMS choisit toujours la tâche prête de plus haute priorité.

#### 4.1.5- Caractéristiques et capacités

RTEMS inclut les aspects suivants :

- Le multitâche ;

- Des systèmes supportant des processeurs homogènes ou hétérogènes ;

- Pilotage par évènement (*Event-driven*) et en fonction de la priorité (*Priority-based*) ;

- Ordonnancement préemptif (*Preemptive scheduling*) ;

- Ordonnancement Rate Monotonic (*RMS*) ;

- Communication et synchronisation entre tâches;

- L'héritage de priorité ;

- Gestion des interruptions ;

- Allocation dynamique de la mémoire.

#### 4.1.6- *Aspect multiprocesseurs*

RTEMS supporte le multiprocesseurs. La communication inter processeur est gérée par la couche MPCI non complète (*MPCI*<sup>13</sup>).

### 4.2- Ecos

Ecos est un noyau à code source ouvert, développé par RedHat. L'objectif principal d'Ecos est de fournir aux développeurs embarqués une infrastructure logicielle commune pour délivrer une gamme diverse de produits embarqués.

La nature de configuration d'Ecos permet à ce système d'exploitation d'être personnalisé aux exigences de l'application, en délivrant de meilleures performances en temps d'exécution (*run time*) et une occupation de ressource matérielle optimisée. Ecos est visé aux applications à fort débit dans l'électronique grand public, les télécommunications, les véhicules à moteur, et les applications profondément embarquées. Dans la version 1.3.1 d'Ecos par exemple, le OS occupe 3K de ROM et 1K de RAM [21].

Les plus adoptés sont: Motorola PowerPC, Intel strong ARM, Advanced RISC Machines ARM7, NEC VR4300, MB8683 \* series, Hitachi SH3, Toshiba TX39, Matsushita MN10300, Fujitsu SPARClite, etc.

#### 4.2.1- *Caractéristiques et capacités*

- Conception modulaire pour la configuration au niveau source.

- Un ensemble riche en primitives de synchronisation.

- Choix des algorithmes d'ordonnancement.

- Choix de la stratégie d'allocation de la mémoire.

- Des horloges et compteurs.

- L'acceptation des interruptions et des communications.

- Traitement des exceptions.

- Une bibliothèque C conforme à la norme ISO.

- Une bibliothèque mathématique.

<sup>13</sup> Multiprocessor Communication Interface

- La portabilité : Ecos et ses composants sont liés à HLA. Ainsi, ils s'exécutent sur n'importe quelle cible, une fois le HAL et ses pilotes sont portés sur l'architecture cible.

#### 4.2.2- HAL

Ecos inclut une couche d'abstraction du matériel (**HAL**<sup>14</sup>), qui cache les traits spécifiques du CPU et des différents dispositifs « *On Chip* » de la plate-forme supportée. Ainsi le noyau et les autres composants peuvent être implémentés de façon portative. Cette abstraction concerne exactement : le changement de contexte, la réaction suite à une interruption matérielle et l'accès aux registres.

Il y a trois couches sur lesquelles fonctionne le HAL :

- *L'architecture* : est le premier sous module de HAL. Chaque famille de processeurs supportée par eCos est considérée comme une architecture différente. Chaque sous module d'architecture contient :

- le code nécessaire pour le démarrage du CPU,

- la livraison des interruptions,

- le changement de contexte,

- et autres fonctionnalités spécifiques à l'architecture.

- *La variante* : est le deuxième sous module de HAL. Elle représente un processeur spécifique dans la famille de processeurs décrite par l'architecture.

- *La plate-forme* : est le troisième sous module de HAL. Une plate-forme est une partie spécifique du matériel qui inclut l'architecture à base de processeur choisi, et même la variante. Typiquement, ce module inclut le code pour le démarrage de la plate-forme, la configuration sélectionnée de chip, les contrôleurs des interruptions, et les dispositifs de temporisateur.

#### 4.2.3- Détails du noyau

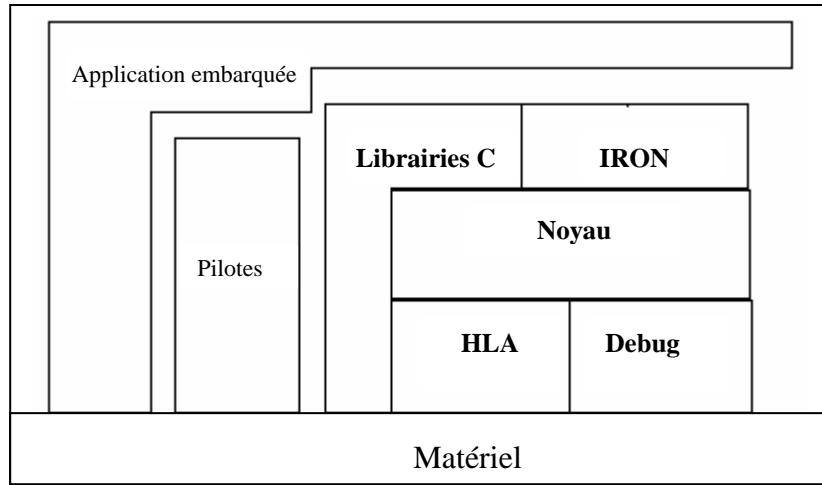

Ce noyau présenté dans la figure ci-dessous est composé des éléments suivants : L'application mise en jeu.

- Des librairies écrites en C, utilisées par le noyau lors de la compilation.

- Les pilotes et HLA qui coopèrent ensemble afin d'assurer l'abstraction du matériel et le portage.

- Le noyau qui gère les tâches, la communication, la synchronisation, les compteurs et les interruptions.

---

<sup>14</sup> *Hardware Abstraction Layer*

- Le debug : c'est un support débogueur du multitâche.

- IRON : c'est une couche qui assure l'utilisation efficace des hétérogénéités présentes dans les systèmes embarqués.

**Figure 9: Les éléments d'Ecos**

#### 4.2.4- *Ordonnancement*

Ecos soutient deux différents ordonnanceurs qui mettent en application des politiques distinctes. Les deux ordonnanceurs sont les suivants:

- *Bitmap Scheduler*: il permet l'exécution des threads à des niveaux de priorité multiples. Cependant, un seul et simple thread peut exister à chaque niveau de priorité. Ceci facilite l'algorithme d'ordonnancement, et rend l'ordonnanceur bitmap très efficace. Le nombre de niveaux de priorité est au maximum 32 : 0 correspond à la priorité la plus élevée et 31 la plus basse. Chaque niveau de priorité est représenté par un bit.

- *Multi-level Queue Scheduler*: Le nombre de niveaux de priorité est au maximum 32 : 0 correspond à la priorité la plus élevée et 31 la plus basse. Un même niveau de priorité peut être attribué à plusieurs tâches en même temps. Cet ordonnanceur permet :

- La préemption entre les différents niveaux de priorité.

- Le soutien du *SMP*<sup>15</sup>.

- Le partage du temps sur un même niveau de priorité.

#### 4.2.5- *Avantages d'Ecos*

- *La configurabilité* : Ecos est désigné comme une architecture composante et configurable formée par plusieurs composants logiciels principaux. La nature de configuration d' Ecos nous permet de sélectionner les différentes options nécessaires dans un

<sup>15</sup> *Symmetric Multi-Processing*

composant logiciel, ou/et de supprimer des composants tout à fait inutilisables afin de créer un système spécialement conçu pour répondre aux exigences de notre application. Par conséquent, la taille de l'application devient compacte et plus rapide comprenant seulement les composants à utiliser.

- *La portabilité* : Ecos est désigné être portatif sur une large gamme d'architectures cibles en incluant les architectures à 16, 32 et 64 bits, les microcontrôleurs et les DSPs. La raison permettant à Ecos d'être fortement portatif est l'implémentation de HAL.

### 4.3- QNX

QNX est un système temps réel de type *UNIX* développé par la société canadienne « *QNX Software* ». Il est conforme à *POSIX*, il permet de développer directement des applications sur la plate-forme cible, et il intègre l'environnement graphique « *Photon* », proche du système Xwindows.

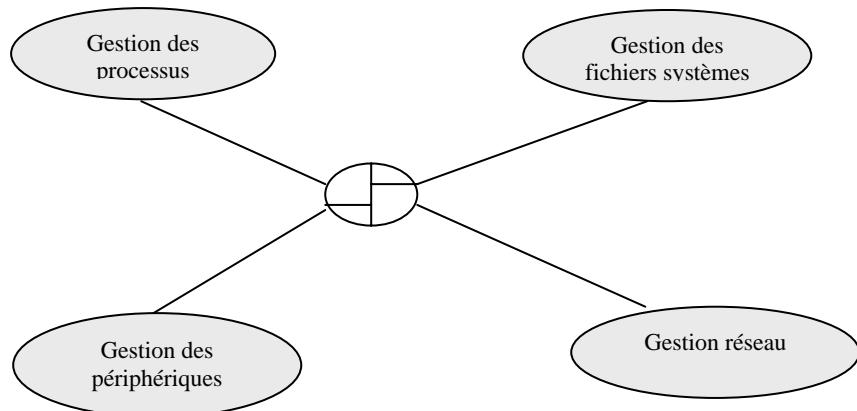

Le point fort de QNX réside dans son architecture à micronoyau préemptif. Comme son nom peut déjà le laisser présumer, QNX a pour domaine de prédilection les applications temps réel dans lesquelles un nombre d'événements doit être géré dans un laps de temps déterminé et garanti. QNX se voit donc doté d'une architecture dans laquelle le noyau du système est réduit à sa plus simple structure. L'unique tâche de ce dernier est de gérer un ensemble de processus de même priorité et inter communiquant entre eux. Graphiquement, cette architecture se résume de la façon suivante figure 10:

**Figure 10: Gestion de processus par Micro-Kernel**

Le micronoyau est au centre de cette structure. Il joue le rôle de passerelle entre les différents processus en cours. Il n'occupe que 10 Ko de mémoire. Ainsi, il peut être tenu dans de nombreuses applications embarquées.

Cette compacité extrême du noyau ainsi que cette structure permet à QNX une certaine adaptabilité. En effet, il est envisageable de faire fonctionner le système sans avoir besoin de certains de ces gestionnaires comme par exemple dans le cas des applications embarquées où l'interface graphique est tout bonnement enlevée du système.

Selon les besoins, les développeurs n'ont alors plus qu'à supprimer ou rajouter des modules au micronoyau pour former le système le plus adapté à ce que nous souhaitons réaliser; c'est la grande force de QNX.

#### **4.3.1- Caractéristiques techniques**

- Système de type UNIX respectant les spécifications POSIX.

- QNX supporte les architectures MIPS, PowerPC, SH4, StrongArm et x86.

- Compatible POSIX.

- Supporte le multiprocesseurs et le multitâche.

- Reconnaît les partitions FAT 16 et FAT 32, ext2, UNIX, OS/2 HPFS, NFS, ainsi que les partitions issues des versions 1.x à 4.x de QNX.

- Interpréteur de commandes standard dans le monde UNIX

#### **4.3.2- Caractéristiques de spécification de QNXv6.1**

Le tableau 2 ci-dessous présente les principales caractéristiques de spécification concernant le système d'exploitation QNX v6.1 [22].

| <b>Critères de classification</b> | <b>QNX v6.1</b>                                                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ROM-RAM Footprint                 | 12 Ko                                                                                                                                |

| Caractéristiques                  | Le RTOS QNX supporte le multiprocesseurs, le traitement distribué transparent, la gestion de réseau avec tolérance aux défaillances. |

| Modèle                            | Threads et Processus.                                                                                                                |

| Priorité                          | 64 niveaux                                                                                                                           |

| Nombre maximum de tâches          | 4095 processus. Chaque processus peut avoir 32 767 threads.                                                                          |

|                                     |                                                                                                                                                       |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Politique d'ordonnancement          | <ul style="list-style-type: none"> <li>- FIFO prioritaire</li> <li>- Ordonnancement Round-Robin</li> <li>- Adaptatif</li> <li>- Sporadique</li> </ul> |

| Soutien MMU <sup>16</sup>           | Oui                                                                                                                                                   |

| Taille de la page physique          | Dépend de l'architecture supportée.                                                                                                                   |

| Mémoire virtuelle                   | Chaque processus s'exécute dans son propre espace mémoire virtuelle.                                                                                  |

| Modèles de protection de la mémoire | Protection de la mémoire virtuelle.                                                                                                                   |

| Contexte                            | L'ISR s'exécute dans le contexte du thread qui lui est attaché.                                                                                       |

| Pile                                | L'ISR a sa propre pile.                                                                                                                               |

Tableau 2: Caractéristiques de QNXv6.1

#### 4.4- Windows CE

Windows CE prend en charge une multitude de fonctionnalités et peut être compilé sur une grande variété de processeurs. Il supporte un environnement multitâche et inclut, en option, une interface utilisateur graphique (GUI). Windows CE reprend l'architecture de la famille Windows, de sorte que tout programmeur de Windows peut facilement passer à la programmation de Windows CE.

Windows CE 3.0 est un système d'exploitation embarqué modulaire et temps réel pour la configuration 32bits légère. Il combine la compatibilité Windows et les services d'applications avancées. Il supporte aussi de multiples architectures à base de processeurs, ainsi que des options de communication et de réseaux. Il permet donc de construire un système adaptable pour développer une large gamme d'équipements.

Cet OS soutient des terminaux Web, des contrôleurs industriels spécialisés, des équipements d'acquisition de données portables et des appareils communicants embarqués. Cette plate-forme particulièrement modulaire permet aux développeurs de concevoir des configurations 32-bits légères compatibles Windows et Internet.

<sup>16</sup> Memory Management Unit

Le tableau 3 ci-dessous présente les principales caractéristiques de spécification concernant le système d'exploitation Windows CE [22] :

| Critères de classification         | Windows CE                                                                                                                                                                   |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM-RAM Footprint                  | 400 Ko de RAM<br>au grosso modo 200 Ko de ROM                                                                                                                                |

| PVM <sup>17</sup>                  | Fiabilité par la protection des services d'application critiques.                                                                                                            |

| Processus et Threads               | Le nombre maximum de threads dans un processus est seulement limité par la quantité disponible de mémoire. Ce processus peut exécuter simultanément au maximum 32 processus. |

| Priorité                           | 256 niveaux                                                                                                                                                                  |

| SIM <sup>18</sup>                  | Réponses très rapides face aux événements avec les ISRs.                                                                                                                     |

| Advanced Power Management          | Batterie longue durée et dissipation de chaleur réduite.                                                                                                                     |

| Support pour le débogage "On-Chip" | Autorise le débogage de l'OAL avant que le noyau de l'OS ne se mette en route.                                                                                               |

| Politique d'ordonnancement         | Round Robin en adoptant un quantum (time slice). Quand ce quantum prend la valeur 0, le thread s'exécute alors jusqu'à son achèvement.                                       |

| Soutien MMU                        | Oui                                                                                                                                                                          |

<sup>17</sup> Protected Virtual Memory

<sup>18</sup> Sophisticated Interrupt Management

|                                     |                                                                                                                                                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Taille de la page physique          | Dépend de l'architecture supportée.                                                                                                                                                                |

| Mémoire virtuelle                   | Oui                                                                                                                                                                                                |

| Modèles de protection de la mémoire | Protection de la mémoire virtuelle.                                                                                                                                                                |

| Contexte                            | L'ISR s'exécute dans un contexte spécial, et utilise des adresses virtuelles statiquement tracées par l'OEM <sup>19</sup> . L'IST est un thread normal d'application, et il a son propre contexte. |

| Pile                                | L'IST est un thread normal d'application, et a son propre contexte.                                                                                                                                |

Tableau 3: Caractéristiques de Windows CE

## 5- Estimation de performance dans les systèmes embarqués temps réel

La complexité des Systèmes sur Puce rend la place des RTOS de plus en plus importante. De plus, leur prix, qui reste relativement élevé, rend indispensable de bonnes performances et une bonne fiabilité, pour que ces systèmes soient compétitifs.

Parmi ces systèmes sur puce, nous citons les systèmes réactifs. En effet, Les systèmes réactifs embarqués tels que définis par Harel et Pnueli [10] sont des systèmes qui maintiennent une relation permanante avec leur environnement physique, à une vitesse déterminée par cet environnement.

Etant très contraints au niveau des ressources matérielles, ils doivent aussi réagir à des sollicitations de leur environnement en un temps fini et spécifié (contraintes temporelles) [11]. D'un point de vue logiciel, de très nombreux systèmes réactifs embarqués font appel à un ou plusieurs systèmes d'exploitation temps réel pour faciliter la gestion d'événements. Un système d'exploitation apporte une souplesse dans l'organisation du contrôle de l'application mais se traduit aussi par un surcoût en mémoire, en ressources de calcul, en consommation et en temps d'exécution. En fait, Le concepteur d'un SoC est donc confronté à de multiples choix pour architecturer son système tout en optimisant une fonction multicritères : performances, coûts, consommation, temps d'exécution et durée de conception (**Time to Market**) [12].

<sup>19</sup> Original Equipment Manufacture

L'objectif est, donc, de trouver une méthode d'estimation de performance des systèmes sur puce temps réel qui soit rapide et précise et qui s'intègre facilement dans un flot de codesign pour assister le concepteur dans son choix architectural.

## 5.1- Approches d'estimation du temps d'exécution :

Les méthodes d'estimations que l'on trouve dans la littérature peuvent être classées dans trois catégories : statiques, dynamiques et mixtes

**Dynamique** : les mesures de performance d'une solution est le résultat d'une analyse statique d'une spécification, (exemple : simulation).

**Statique** : l'estimation de performance d'une solution est le résultat d'une analyse statique d'une spécification, (exemple : analyse de chemins dans une spécification de flots de contrôle).

**Mixte dynamique/statique** : C'est l'utilisation de quelques éléments des deux approches précédentes pour l'analyse de performance d'une solution.

Les approches dynamiques sont en général très précises. Leur inconvénient majeur est le temps nécessaire pour l'obtention du modèle à simuler (synthèse, génération, compilation...), ainsi que le temps de la simulation. Ce qui les rend, en pratique, inutilisable dans le contexte particulier de l'exploration où le nombre de modèles à analyser est énorme. D'un autre coté, les approches statiques sont certes très rapides (pas de génération de modèles à simuler, ni de simulation), mais les tâches de modélisation et d'estimation sont complexes à cause de la distance qui sépare les concepts de spécification de l'implémentation.

### 5.1.1- Travaux visant des architectures cibles monoprocesseur :

Dans cette catégorie, on peut citer PMOSS [30], COSYMA [31] and LYCOS [32]. L'architecture cible est monoprocesseur (une seule unité de contrôle). Il n'y a donc pas de difficultés liées au parallélisme par rapport aux architectures multiprocesseurs. Cependant, les analyses de performance des parties logicielles et matérielles sont réalisées conjointement.

**PMOSS** se contente de calculer l'accélération due au coprocesseur (partie matérielle), sur la performance globale du système. Pour cela, il utilise, pour le logiciel, des analyses statiques (calcul du temps d'exécution basé sur le code assembleur) et dynamiques (profilage). Pour le matériel, il utilise des analyses statiques (calcul du temps d'exécution basé sur la description de la machine de contrôle). Et pour les communications, des analyses dynamiques (profilage), sont utilisées.

**COSYMA** calcule des métriques séparées pour le logiciel, le matériel et la communication. Ensuite, ces métriques sont combinées dans des équations particulières pour procéder à une partition basée sur une méthode de recuit simulé (simulated annealing). Des mesures de temps dans le pire cas sont calculées pour les implémentations logicielles en utilisant plusieurs variantes de techniques d'analyse de chemins. Le temps de communication est estimé pour son modèle particulier (mémoire partagée).

**LYCOS** procède à des estimations de performance en utilisant des techniques de profilage et d'estimations de temps d'exécution à bas niveau pour le matériel, le logiciel et la communication.

Malgré leur performance, ces méthodes ne permettent pas de traiter des architectures complexes pouvant contenir plus qu'un seul processeur.

### 5.1.2- *Travaux visant des architectures cibles multiprocesseurs :*

Dans cette catégorie nous trouvons SpecSyn [33], POLIS [34] et la méthode créée par Yen et al [35]. L'architecture cible est multiprocesseurs complexe.

**SpecSyn** admet des architectures avec un nombre quelconque de microprocesseurs et de coprocesseurs. L'approche utilisée pour l'estimation de performance est mixte statique/dynamique. Elle est faite en deux étapes :

- **Pre-estimation** : elle est réalisée avant la phase d'exploration d'architectures. Un profilage de la description du système est réalisé pour obtenir des temps d'exécution pour différents niveaux (processus, bloc de base, communication).

- **Estimation en ligne** : elle est faite durant la phase d'exploration d'architectures. Les résultats obtenus durant la phase de pre-estimation sont utilisés dans des expressions complexes pour le calcul de la performance globale du système.