République Tunisienne

Ministère de l'Enseignement Supérieur et

de la Recherche Scientifique

Université de Sfax

Ecole Nationale d'Ingénieurs de Sfax

Département de Génie Informatique

Cycle de Formation doctorale dans

la discipline *Ingénierie des

Systèmes Informatiques*

**Kaïs Loukil**

**Thèse Doctorat**

**N° d'ordre:**

# THESE

*présentée à*

**L'Ecole Nationale d'Ingénieurs de Sfax**

*en vue de l'obtention du*

**DOCTORAT**

**Dans la discipline**

**Ingénierie des Systèmes Informatiques**

*par*

**Kaïs LOUKIL**

**Approche de gestion de

performances/contraintes pour les systèmes

embarqués temps réel**

*Soutenu le 06/12/2011, devant la commission d'examen:*

|    |                      |                  |

|----|----------------------|------------------|

| M. | Mohamed Jmaiel       | <i>Président</i> |

| M. | Habib Youssef        | <i>Membre</i>    |

| M. | Samir Ben Ahmed      | <i>Membre</i>    |

| M. | Jean Philippe Diguet | <i>Membre</i>    |

| M. | Mohamed Abid         | <i>Membre</i>    |

# ***Remerciements***

*Cette thèse a été réalisée au sein du laboratoire Computer & Embedded System, (CES) dirigé par **Pr.***

***Mohamed Abid.***

*Il m'est agréable de saisir cette occasion pour adresser mes sincères remerciements et ma gratitude la plus profonde à mon directeur de thèse **Pr. Mohamed Abid**, professeur à l'ENIS pour son aide précieuse, ses conseils bienveillants, ses compétences, ses grandes expériences et ses qualités humaines m'ont été d'une grande importance et m'ont permis de mener à bien ce travail. Qu'il trouve ici l'expression de mes profondes reconnaissances.*

*Je tiens à remercier chaleureusement mon encadrant et ami **Nader Ben Amor** maître assistant à l'ENIS. Merci Nader pour l'intérêt que tu as porté à mon travail, tes remarques et tes conseils utiles pour la réussite de cette thèse.*

*Mes remerciements s'adressent à **Pr. Samir Ben Ahmed** et **Pr. Habib Youssef** d'avoir accepté d'être les rapporteurs de cette thèse. Je tiens à remercier également, **Pr Mohamed Jmaïl** qui a accepté de présider le jury et **Pr Jean Philippe Diguet**, qui a bien voulu juger ce travail et pour l'attention qu'il m'a accordée.*

*Je remercie également **Mouna Ben Saïd** et **Lina Jarboui** pour leurs contributions ainsi que tous les membres du laboratoire CES pour leurs coopérations et encouragements.*

*Une pensée particulière à tous mes **enseignants** qui ont participé à ma formation.*

*Je n'oublierai jamais tous ceux qui partagent ma vie personnelle et qui m'ont soutenu durant cette thèse, et bien souvent durant les années antérieures. Je pense évidemment à mes **parents** et ma **famille** proche.*

# *Table des matières*

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| <i>Glossaire</i> .....                                                              | 0  |

| <b>CHAPITRE 1: Introduction générale</b> .....                                      | 1  |

| <b>1 Motivation</b> .....                                                           | 2  |

| <b>2 Contribution de la thèse</b> .....                                             | 4  |

| <b>3 Organisation du document</b> .....                                             | 6  |

| <b>CHAPITRE 2 : Conception de système sur puce adaptatif : état de l'art.</b> ..... | 8  |

| <b>1 Introduction</b> .....                                                         | 9  |

| <b>2 Système embarqué</b> .....                                                     | 9  |

| 2.1 Domaines d'application .....                                                    | 10 |

| 2.2 Caractéristiques des systèmes embarqués .....                                   | 10 |

| 2.2.1 Encombrement .....                                                            | 10 |

| 2.2.2 L'autonomie .....                                                             | 10 |

| 2.2.3 Le temps réel .....                                                           | 11 |

| 2.2.4 Qualité de service .....                                                      | 11 |

| 2.2.5 Complexité .....                                                              | 12 |

| <b>3 Conception de système embarqué</b> .....                                       | 12 |

| 3.1 Flot de conception Logiciel/Matériel .....                                      | 13 |

| 3.1.1 Spécification haut niveau .....                                               | 14 |

| 3.1.2 Partitionnement logiciel / matériel .....                                     | 15 |

| 3.1.3 Validation .....                                                              | 16 |

| 3.2 Gestion de la consommation .....                                                | 16 |

| 3.3 Techniques de réduction de la consommation .....                                | 17 |

| 3.3.1 Technique matérielle .....                                                    | 18 |

| 3.3.2 Technique logicielle .....                                                    | 19 |

| 3.3.3 Technique mixte .....                                                         | 19 |

| 3.4 Approches de codesign faible consommation .....                                 | 20 |

| 3.5 Limitations des approches présentées .....                                      | 21 |

| 3.5.1 Le comportement de la batterie du système .....                               | 21 |

| 3.5.2 La variabilité des données et des applications .....                          | 22 |

| 3.5.3 Préférences de l'utilisateur .....                                            | 22 |

| 3.5.4 Choix architectural .....                                                     | 22 |

| 3.5.5 Influence de l'environnement .....                                            | 23 |

| <b>4 Méthodologies d'adaptation</b> .....                                           | 23 |

| 4.1 Adaptation au niveau matériel .....                                             | 24 |

| 4.1.1 Technique DVS .....                                                           | 24 |

| 4.1.2 Gestion dynamique de la consommation « DPM » .....                            | 25 |

| 4.2 Adaptation au niveau système d'exploitation .....                               | 25 |

| 4.3 Adaptation au niveau applications .....                                         | 26 |

| 4.4 Approches d'adaptation existantes .....                                         | 27 |

| 4.4.1 Gestion de la QoS pour assurer une interaction de trames .....                | 27 |

| 4.4.2 Adaptation à base d'affectation de budget de ressource .....                  | 28 |

| 4.4.3 Gestion de la QoS basée sur le partitionnement HW/SW .....                    | 30 |

| 4.4.4 Approche d'adaptation multicouche « GRACE » .....                             | 30 |

| 4.4.5 Approche d'adaptation du Lab-STICC .....                                      | 31 |

| 4.4.6 Approche d'adaptation multi contrainte « class » .....                        | 32 |

| 4.5 Discussion .....                                                                | 33 |

| <b>5 Conclusion</b> .....                                                           | 33 |

| <b>CHAPITRE 3 : Approche d'adaptation multicouche</b> .....                         | 35 |

| <b>1 Introduction</b> .....                                                         | 36 |

| <b>2 Activité d'observation</b> .....                                               | 37 |

| 2.1 Paramètres de l'activité d'observation .....                                    | 38 |

|                                                                           |           |

|---------------------------------------------------------------------------|-----------|

| 2.2 Ajustement dynamique de Pobs.....                                     | 38        |

| <b>3 Activité d'adaptation.....</b>                                       | <b>39</b> |

| 3.1 Modèle d'adaptation niveau application.....                           | 39        |

| 3.2 Adaptation niveau architectural .....                                 | 40        |

| 3.3 Modèle d'adaptation niveau système d'exploitation .....               | 40        |

| <b>4 Adaptation multicouche .....</b>                                     | <b>42</b> |

| 4.1 Vue d'ensemble .....                                                  | 42        |

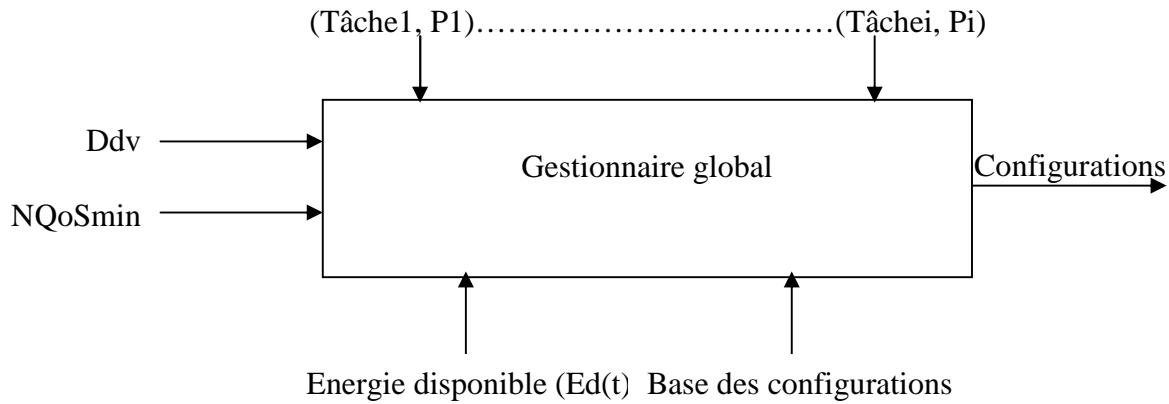

| 4.2 Gestionnaire global « GM » .....                                      | 43        |

| 4.2.1 Formulation mathématique du problème.....                           | 44        |

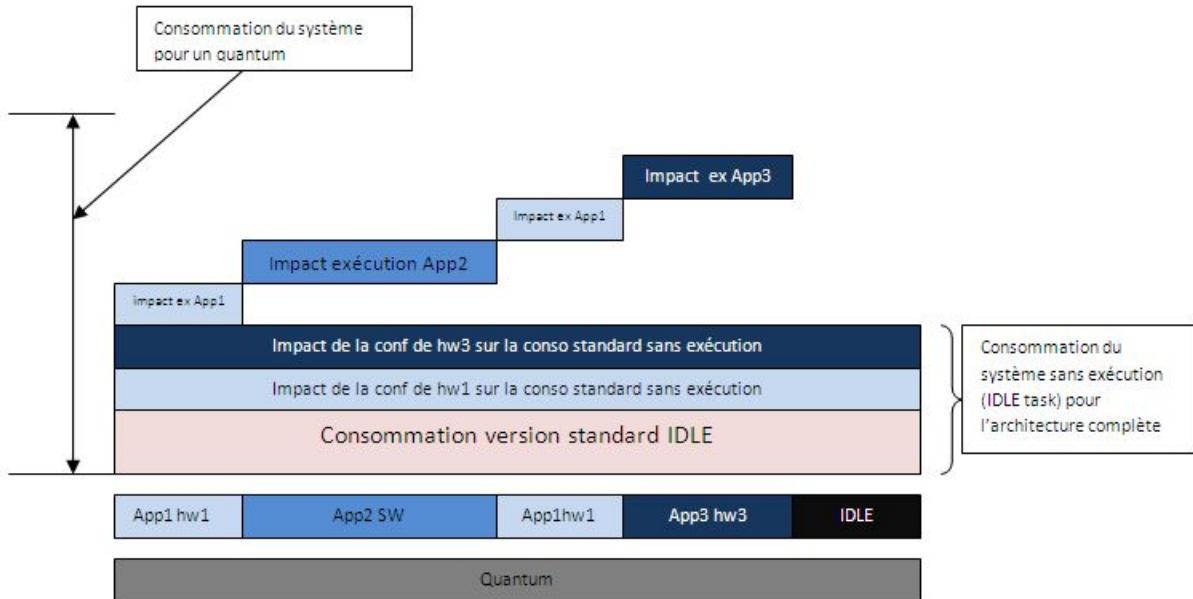

| 4.2.2 Quantification de la consommation en énergie électrique.....        | 46        |

| 4.2.3 Recherche de la solution.....                                       | 47        |

| 4.2.4 Présentation des méthodes d'optimisation .....                      | 48        |

| 4.2.5 Algorithme génétique .....                                          | 51        |

| 4.2.6 Algorithme du recuit simulé.....                                    | 53        |

| 4.3 Le gestionnaire local.....                                            | 56        |

| 4.3.1 Principe de fonctionnement .....                                    | 56        |

| 4.3.2 Choix de l'algorithme d'ordonnancement.....                         | 58        |

| 4.3.3 Les algorithmes d'ordonnancement pour les systèmes temps réel ..... | 59        |

| 4.3.4 Choix de l'ordonnanceur .....                                       | 60        |

| <b>5 Etape de caractérisation des configurations.....</b>                 | <b>62</b> |

| 5.1 Mise en place des configurations.....                                 | 62        |

| 5.2 Partitionnement logiciel/matériel.....                                | 62        |

| 5.2.1 Profilage de l'application :(Profiling).....                        | 63        |

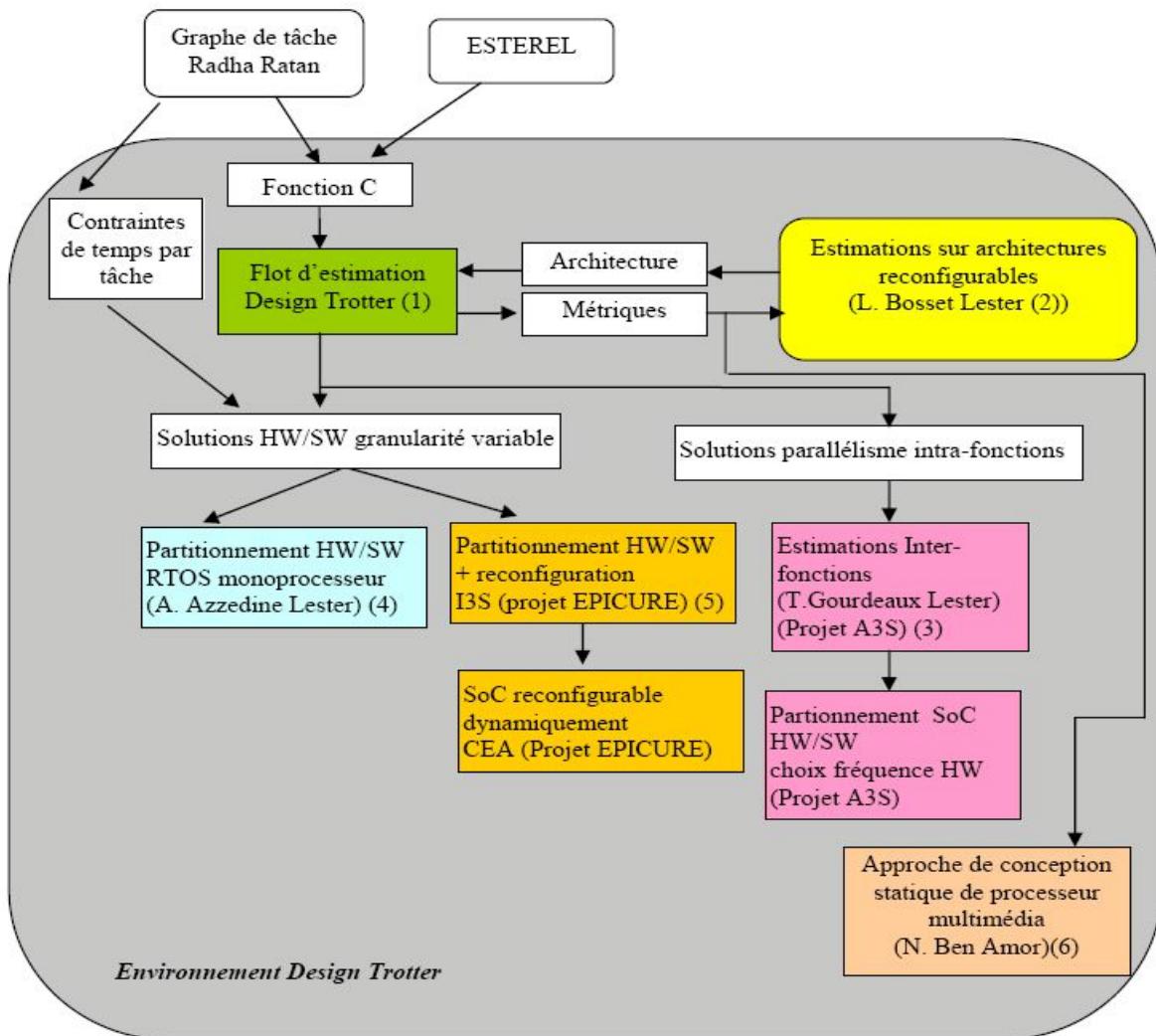

| 5.2.2 Analyse par design trotter.....                                     | 63        |

| 5.3 Caractérisation des configurations.....                               | 65        |

| 5.3.1 Calcul de Texe .....                                                | 65        |

| 5.3.2 Mesure de la consommation .....                                     | 65        |

| 5.3.3 Quantification de la QoS .....                                      | 66        |

| <b>6 Conclusion.....</b>                                                  | <b>66</b> |

| <b>CHAPITRE 4 : Etude de cas &amp; Environnement de validation .....</b>  | <b>67</b> |

| <b>1 Introduction .....</b>                                               | <b>68</b> |

| <b>2 Aperçu sur l'application synthèse d'image 3D.....</b>                | <b>68</b> |

| 2.1 Différentes étapes du pipeline.....                                   | 68        |

| 2.1.1 Transformations .....                                               | 69        |

| 2.1.2 Test de visibilité.....                                             | 69        |

| 2.1.3 Calculs des lumières .....                                          | 71        |

| 2.1.4 Transformations des textures .....                                  | 73        |

| 2.1.5 Clipping (fenêtrage).....                                           | 73        |

| 2.1.6 Projection .....                                                    | 73        |

| 2.1.7 Rastérisation .....                                                 | 74        |

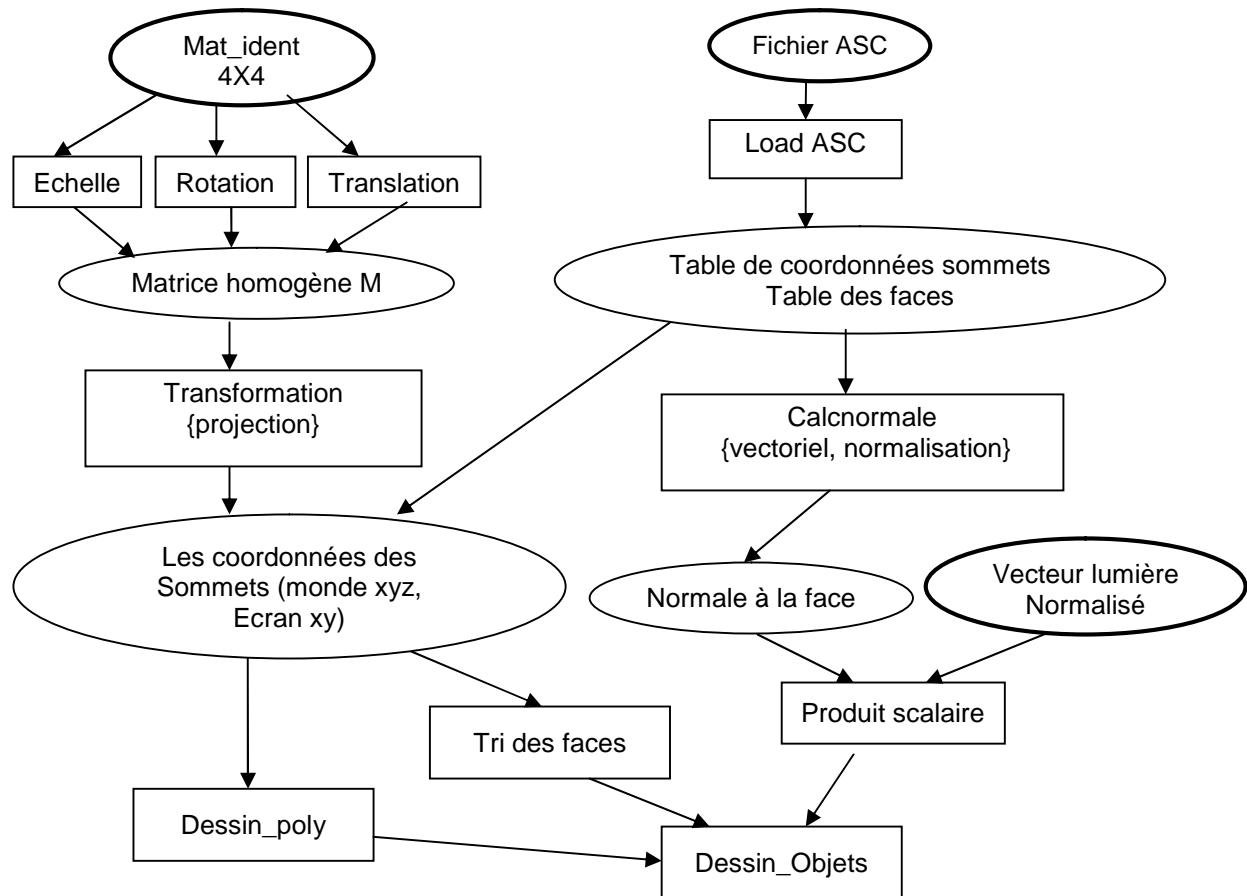

| 2.2 Graphe de tâches de l'application 3D .....                            | 77        |

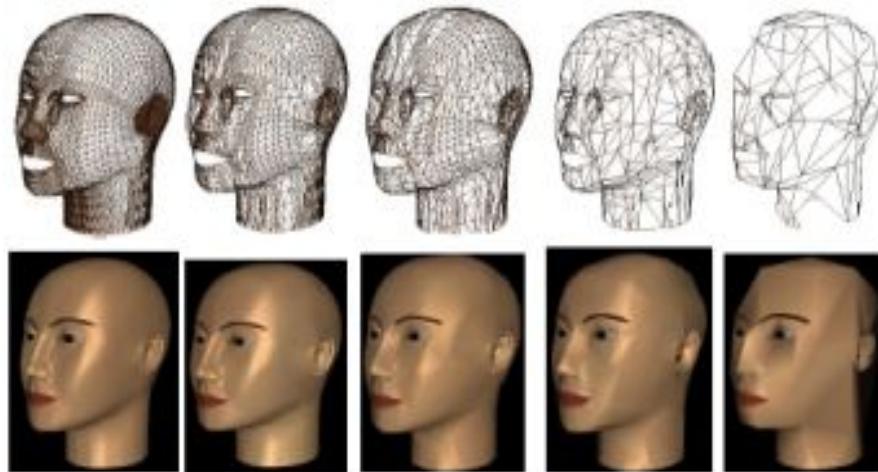

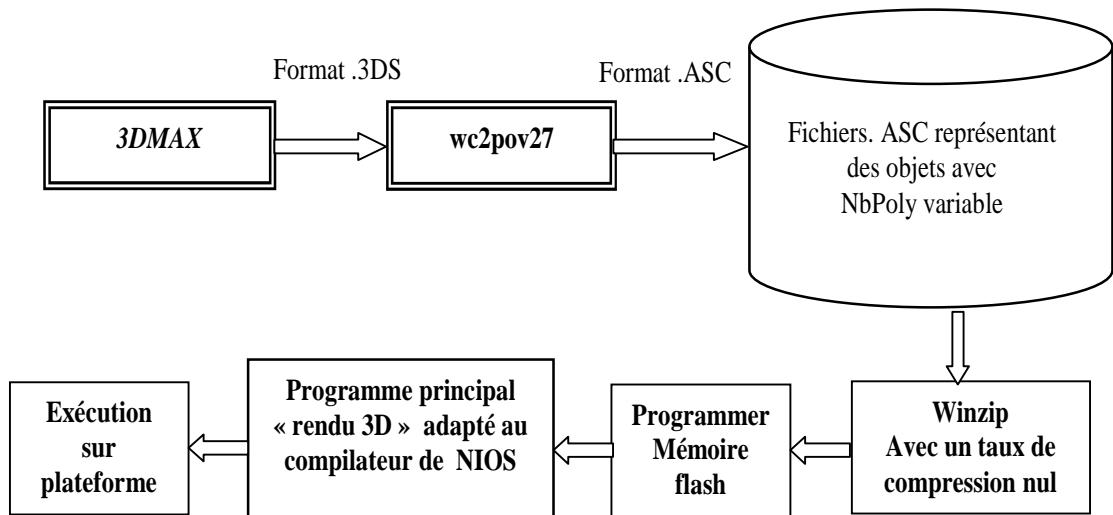

| 2.3 Modification de l'application « synthèse 3D » .....                   | 78        |

| 2.3.1 Construction des configurations logicielles.....                    | 78        |

| 2.3.2 Développement d'une version multi-applications .....                | 80        |

| 2.4 Intégration des services de MicroC/OS-II .....                        | 80        |

| <b>3 Environnement de conception des configurations mixtes .....</b>      | <b>81</b> |

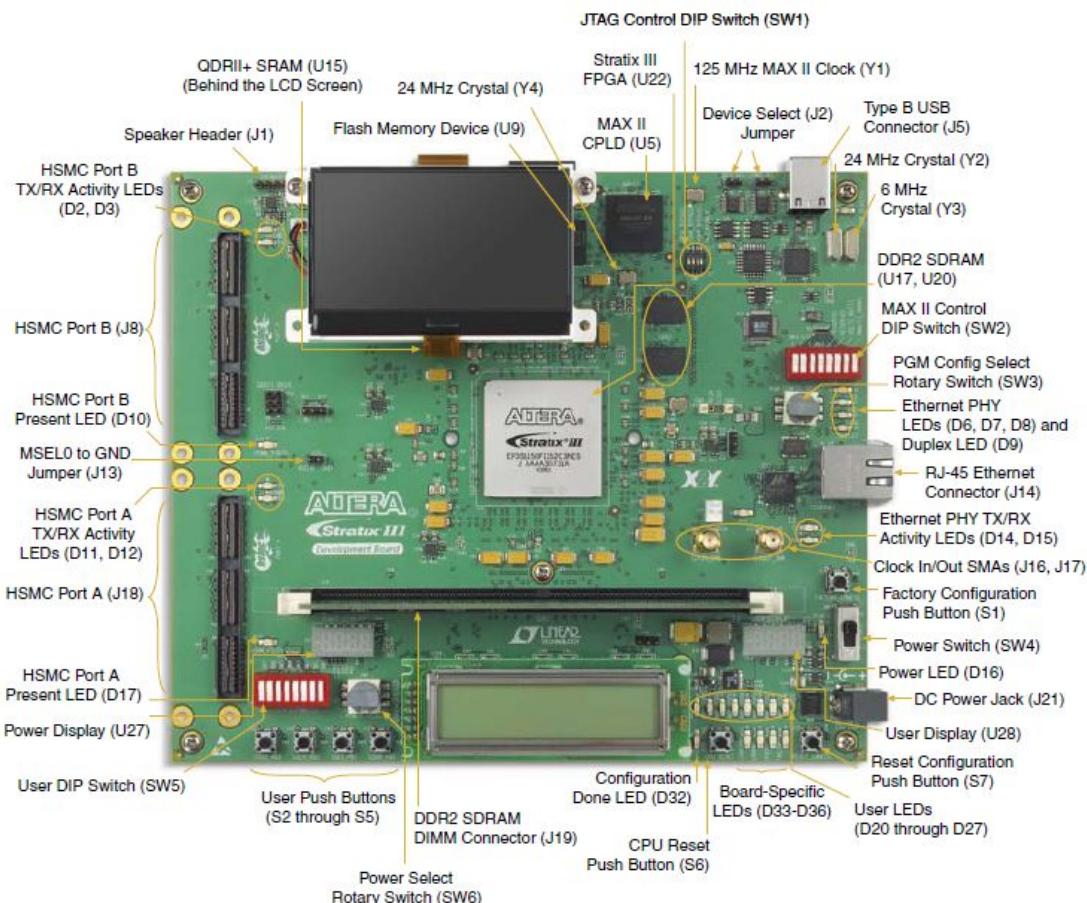

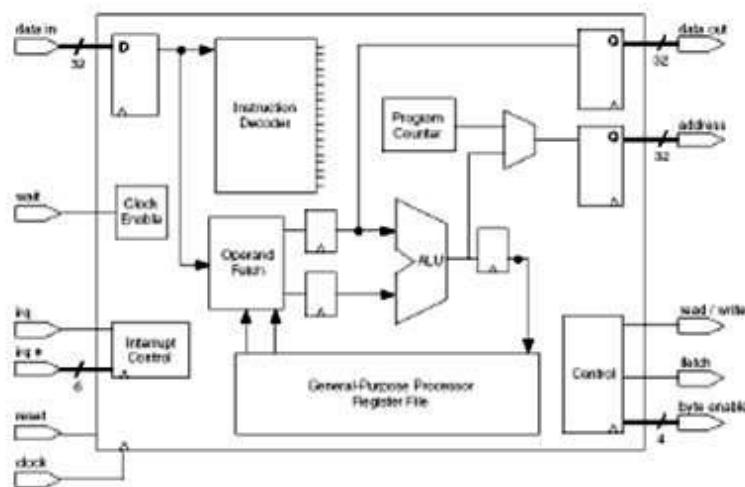

| 3.1 Le processeur embarqué NIOS .....                                     | 83        |

| 3.2 Etude du bus Avalon.....                                              | 83        |

| 3.2.1 Caractéristiques .....                                              | 84        |

| 3.2.2 Modes de transfert .....                                            | 85        |

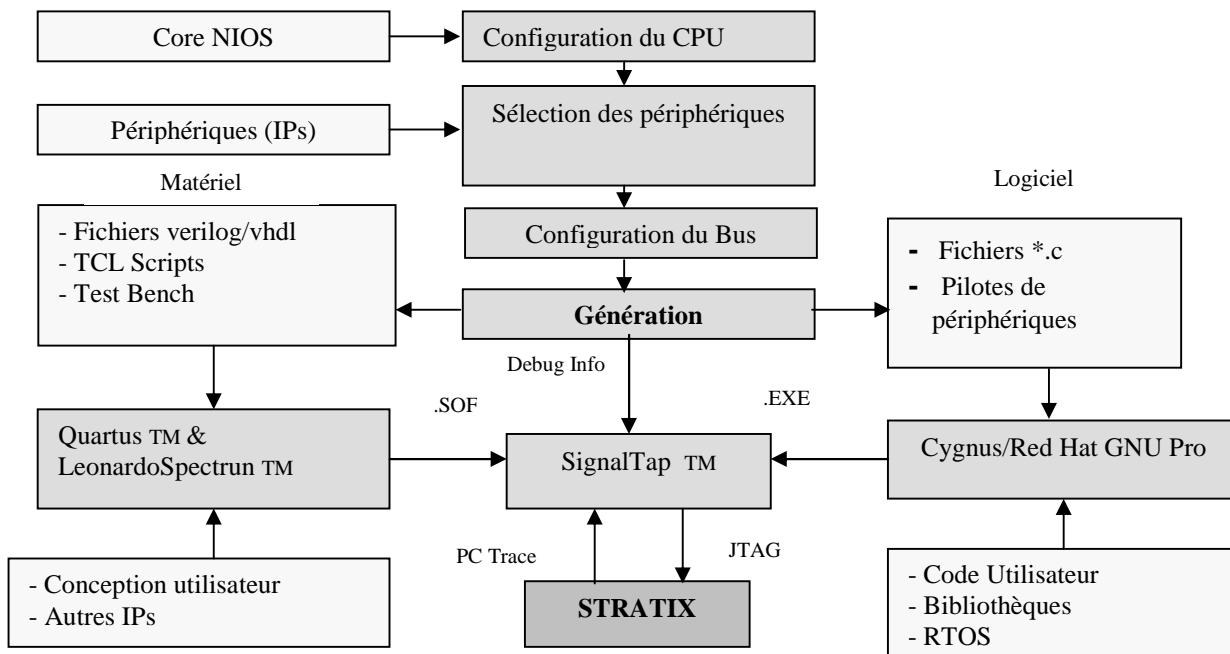

| 3.3 Flot de conception de l'environnement d'Altera .....                  | 85        |

| <b>4 Etude du système d'exploitation temps réel : MicroC/OS-II.....</b>   | <b>86</b> |

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

| 4.1 Capacités et caractéristiques .....                                         | 86  |

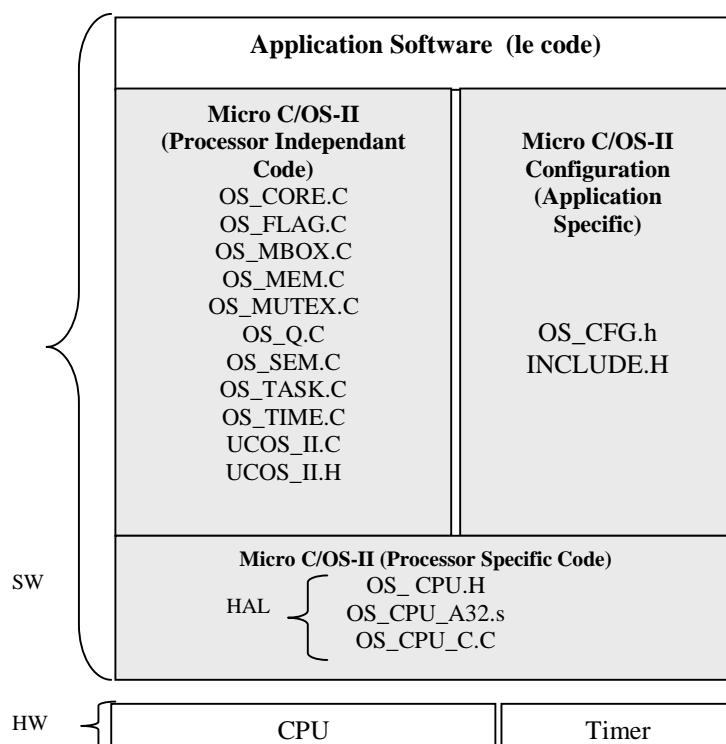

| 4.2 Structure de MicroC/OS-II .....                                             | 87  |

| 4.3 Fonctionnement de MicroC/OS-II.....                                         | 88  |

| 4.3.1 Création d'une tâche .....                                                | 88  |

| 4.3.2 Fonctions de base.....                                                    | 88  |

| 4.3.3 Communication inter tâches .....                                          | 89  |

| 5 Conclusion .....                                                              | 90  |

| Chapitre 5 : Expérimentation et validation .....                                | 92  |

| 1 Introduction .....                                                            | 93  |

| 2 Construction de la base des configurations .....                              | 93  |

| 2.1 Configuration purement logicielles .....                                    | 93  |

| 2.1.1 Etude de l'effet des attributs applicatifs sur le temps d'exécution ..... | 95  |

| 2.2 Conception des configurations mixtes HW/SW .....                            | 96  |

| 2.2.1 Conception d'accélérateurs dédiés à la synthèse 3D .....                  | 96  |

| 2.2.2 Implémentation des accélérateurs.....                                     | 102 |

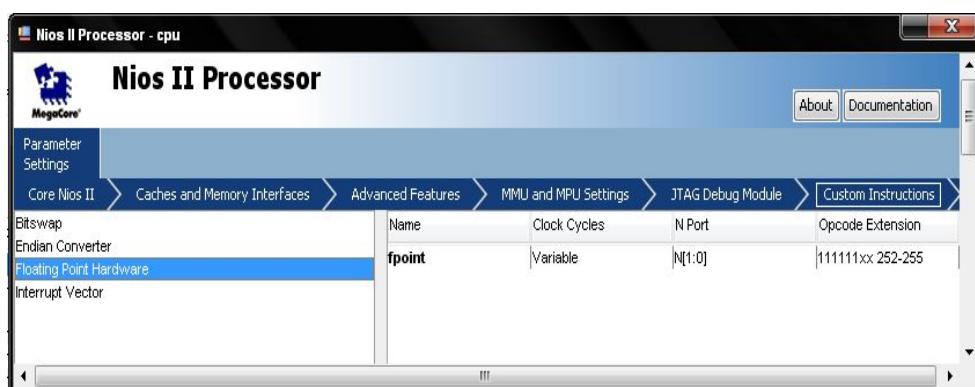

| 2.3 Ajout des coprocesseurs hardwares .....                                     | 107 |

| 2.4 Etude de l'effet des paramètres architecturaux sur Texe .....               | 108 |

| 2.5 Mesure de la consommation .....                                             | 109 |

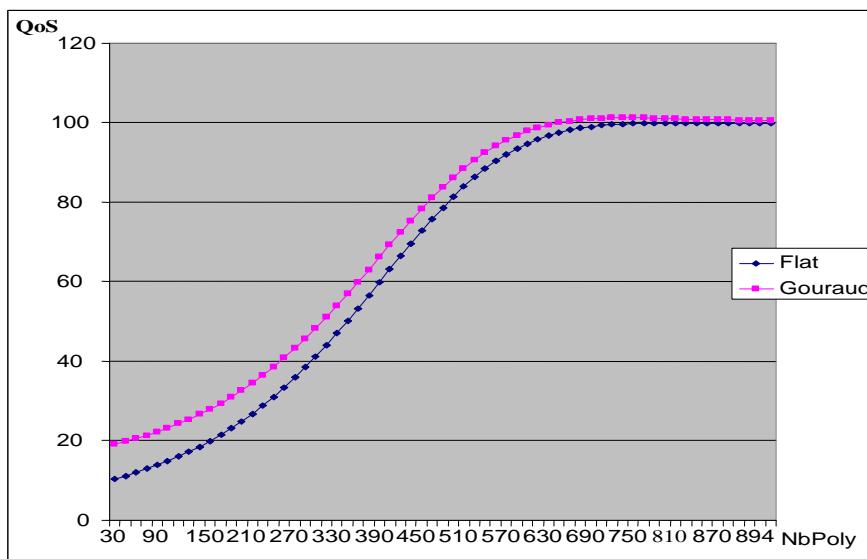

| 2.6 Mise en place du modèle de QoS .....                                        | 110 |

| 2.7 Configurations retenues .....                                               | 112 |

| 3 Mise en place d'un système d'exploitation temps réel.....                     | 113 |

| 3.1 Description de l'EDF ( <i>Earliest Deadline First</i> ).....                | 113 |

| 3.2 Implémentation de l'EDF sous µC_OS-II .....                                 | 113 |

| 3.2.1 Gestion de la périodicité .....                                           | 114 |

| 3.2.2 Mise en œuvre de EDF .....                                                | 116 |

| 4 Test de l'approche proposée .....                                             | 118 |

| 5 Apport de l'approche .....                                                    | 121 |

| 6 Mise en œuvre des algorithmes d'optimisation.....                             | 124 |

| 6.1 Premier scénario .....                                                      | 125 |

| 6.2 Deuxième scénario.....                                                      | 126 |

| 6.3 Méthode mixte .....                                                         | 127 |

| 7 Conclusion .....                                                              | 129 |

| Conclusions générales .....                                                     | 130 |

| 1 Conclusion.....                                                               | 131 |

| 2 Réponse à la problématique et travail réalisé .....                           | 131 |

| 3 Perspectives.....                                                             | 133 |

| Références .....                                                                | 134 |

| Webographie.....                                                                | 139 |

# ***Liste des figures***

|                                                                                                                                  |     |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

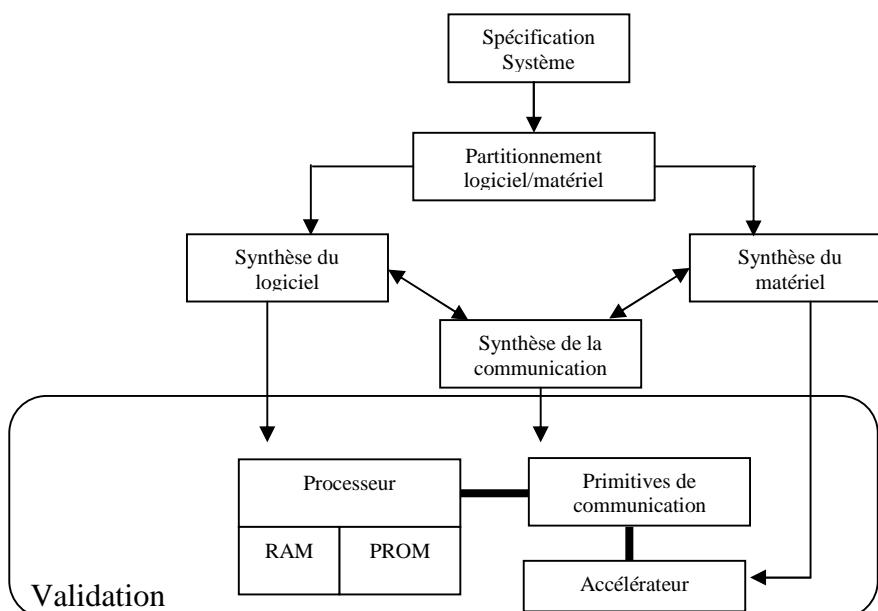

| Figure 1: Flot de conception .....                                                                                               | 13  |

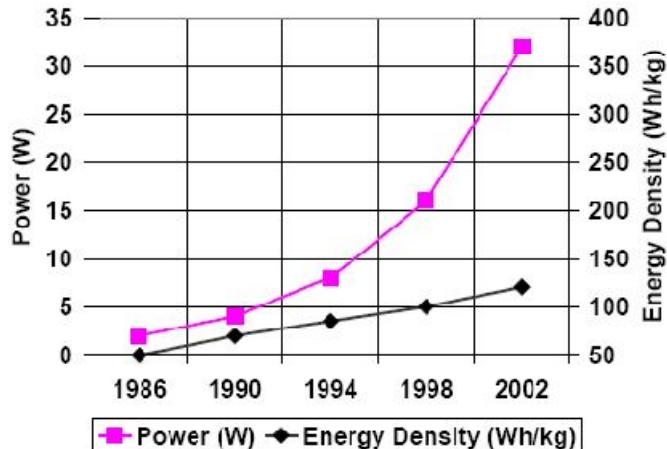

| Figure 2: "Gap" entre l'évolution des batteries et l'évolution des semi-conducteurs [Kan02].                                     | 17  |

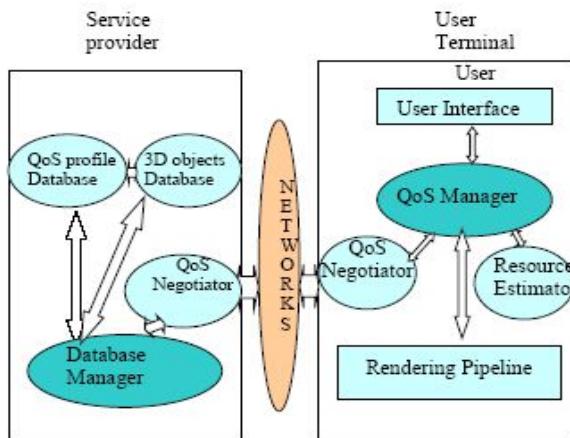

| Figure 3: Schéma du système d'adaptation [Pha04].....                                                                            | 27  |

| Figure 4: Structure de la couche d'adaptation [Van02].....                                                                       | 29  |

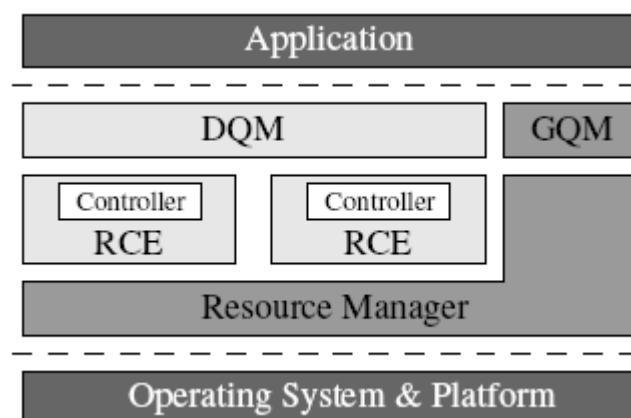

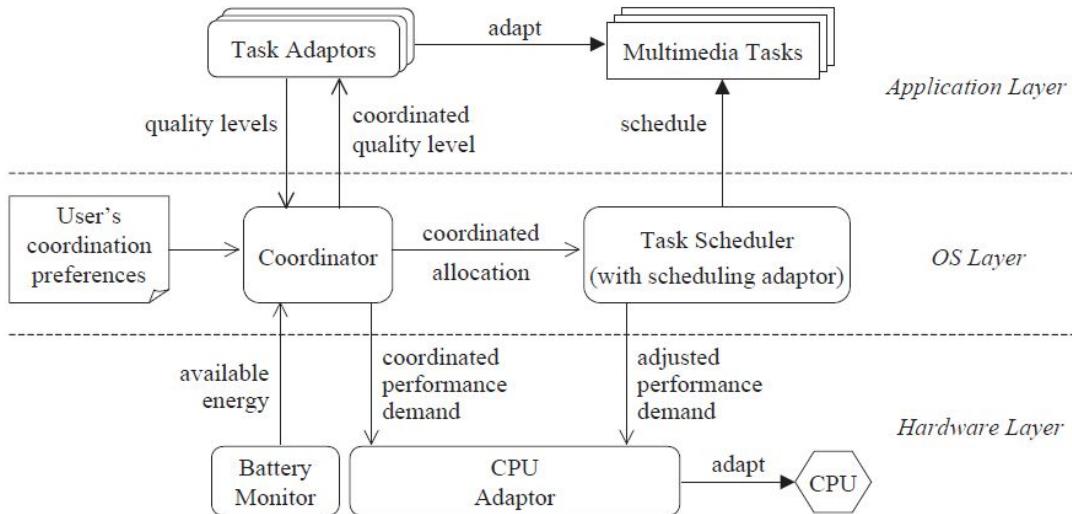

| Figure 5: Schéma de l'approche Grace [Wan03] .....                                                                               | 31  |

| Figure 6: Principe de fonctionnement de l'approche du Lab-STICC .....                                                            | 31  |

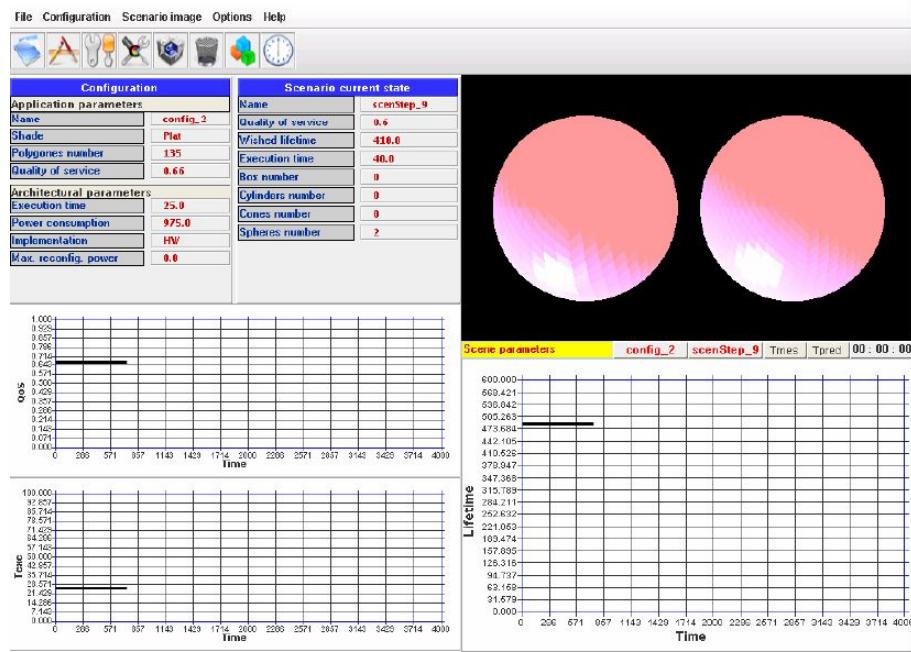

| Figure 7: Interface du simulateur « class » .....                                                                                | 33  |

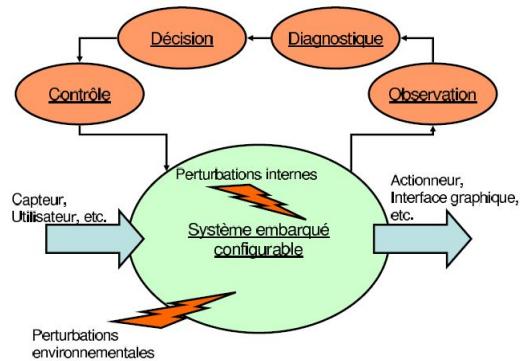

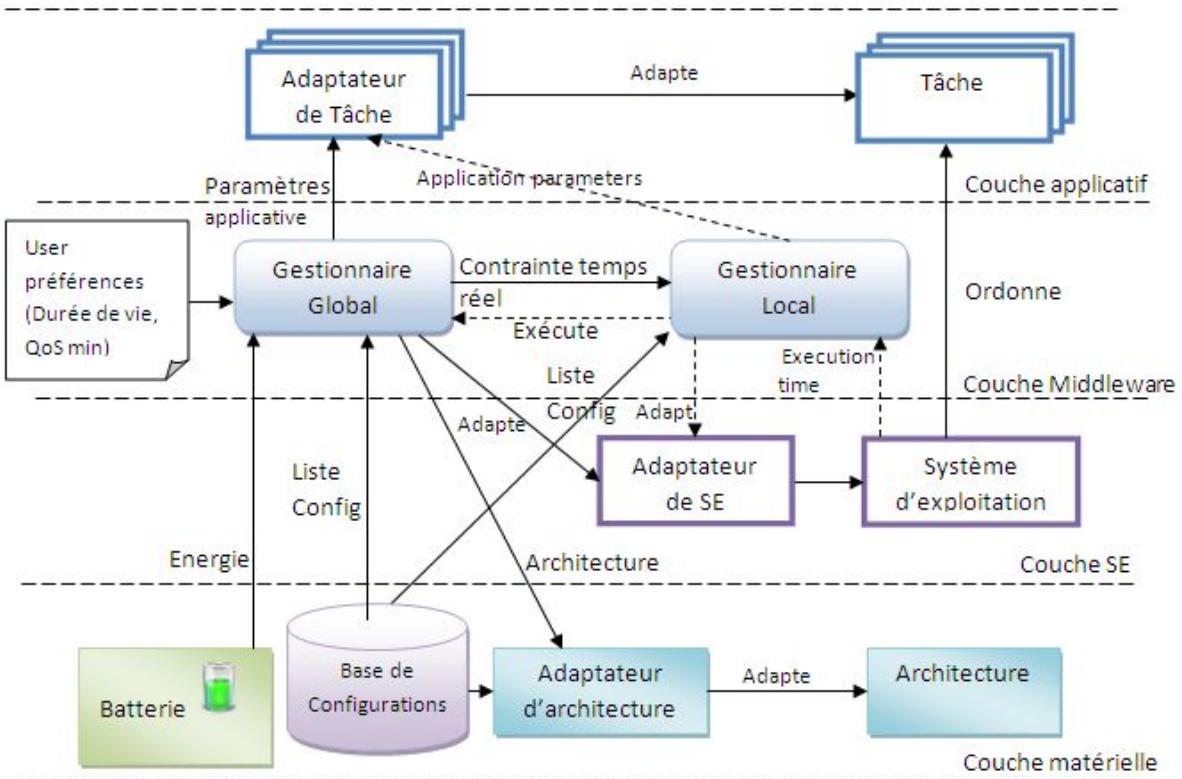

| Figure 8: Schéma du système d'adaptation.....                                                                                    | 37  |

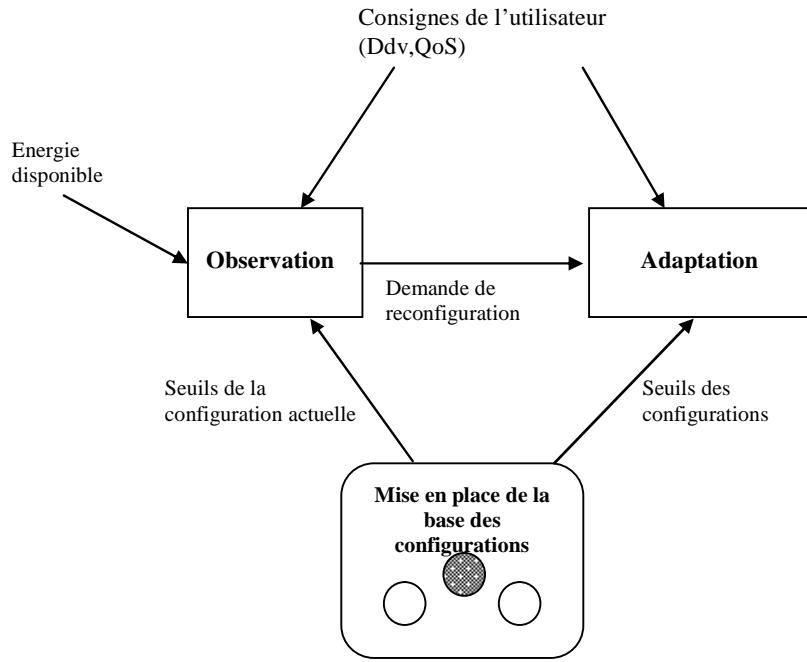

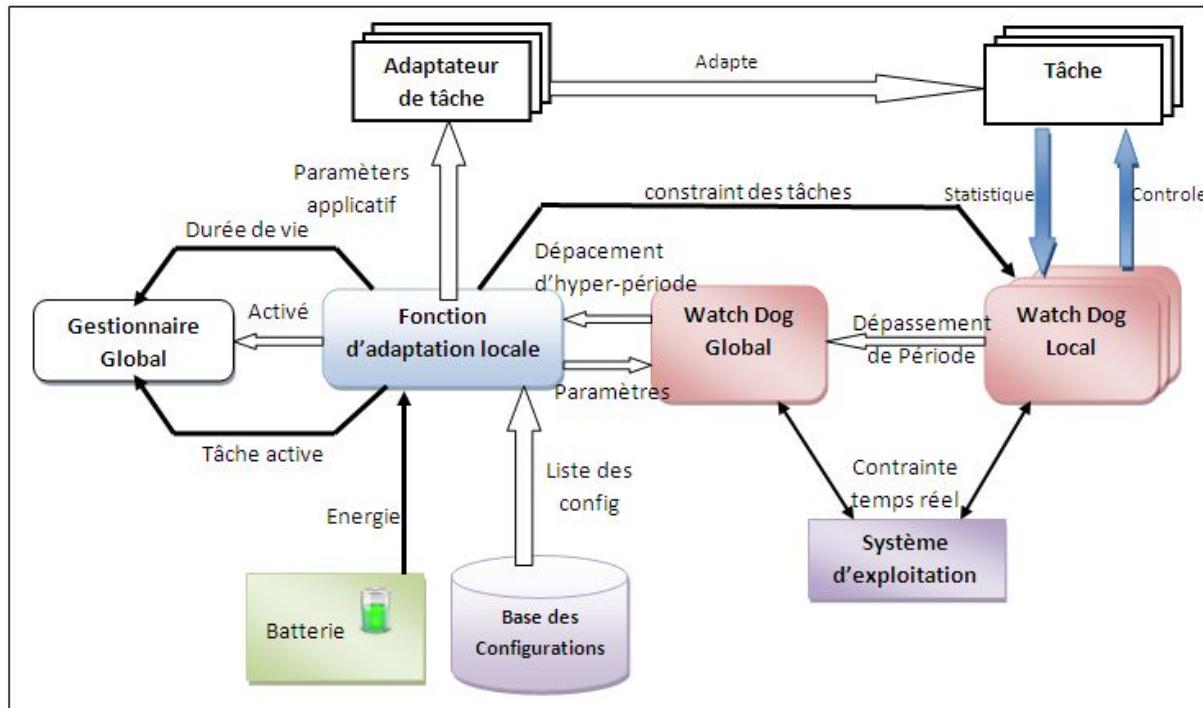

| Figure 9: Approche d'adaptation .....                                                                                            | 43  |

| Figure 10: Le gestionnaire global .....                                                                                          | 44  |

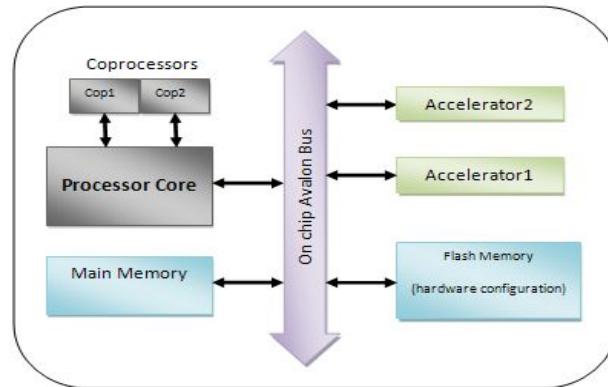

| Figure 11 : Architecture d'un SoC .....                                                                                          | 46  |

| Figure 12 : Modélisation de la consommation.....                                                                                 | 47  |

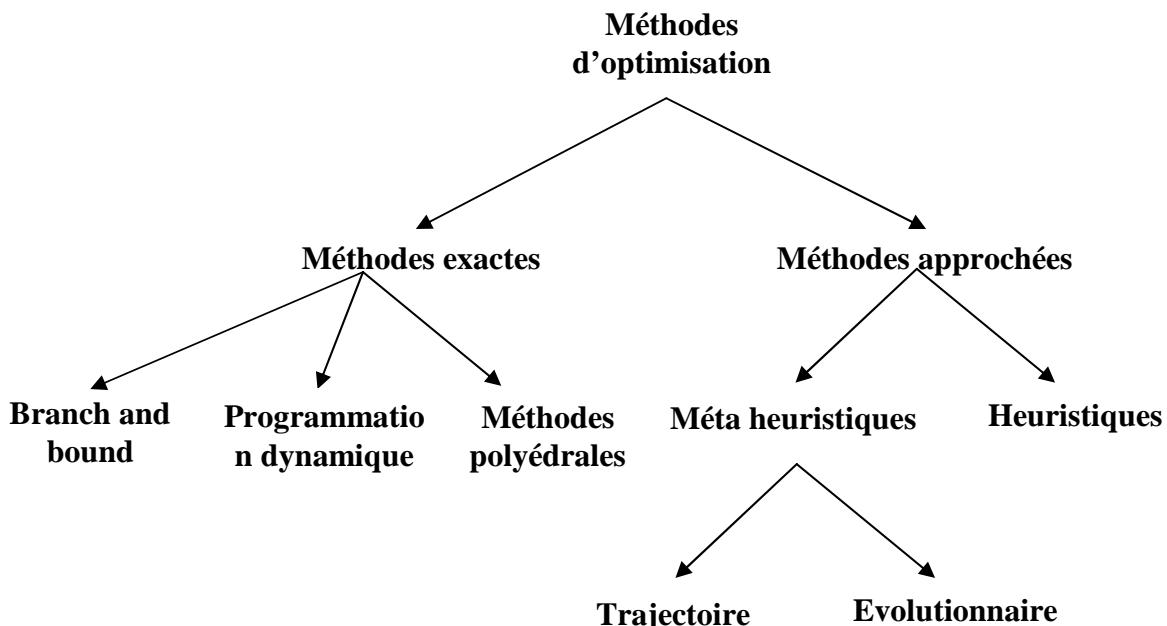

| Figure 13:Classification des algorithmes d'optimisation.....                                                                     | 48  |

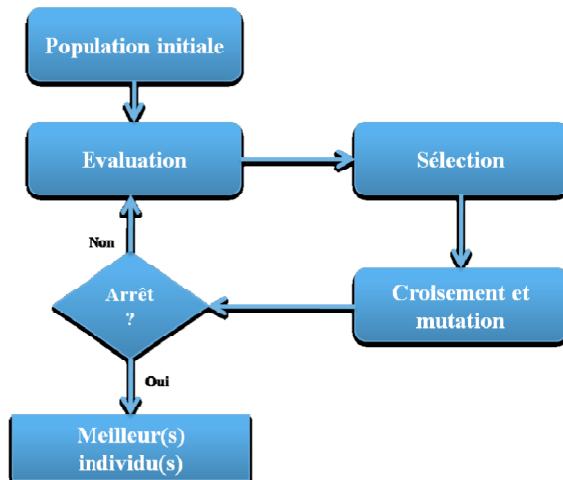

| Figure 14: Principe de base d'un algorithme génétique .....                                                                      | 52  |

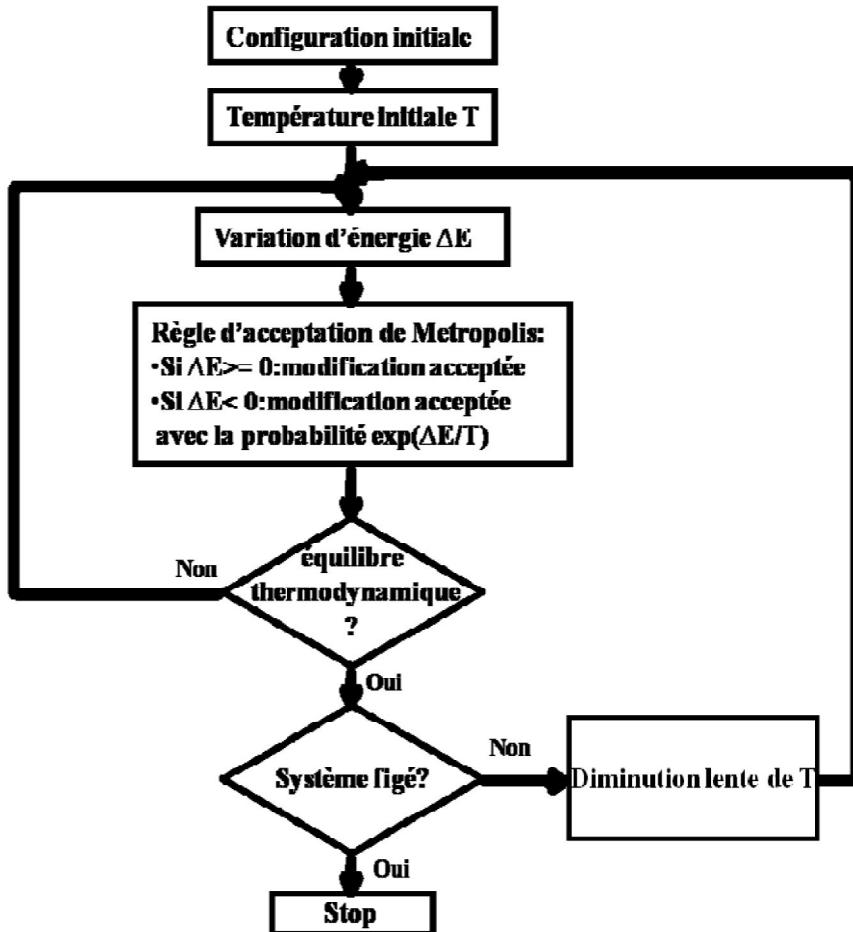

| Figure 15: Organigramme de l'algorithme du recuit simulé.....                                                                    | 55  |

| Figure 16:Schéma de principe du gestionnaire local .....                                                                         | 57  |

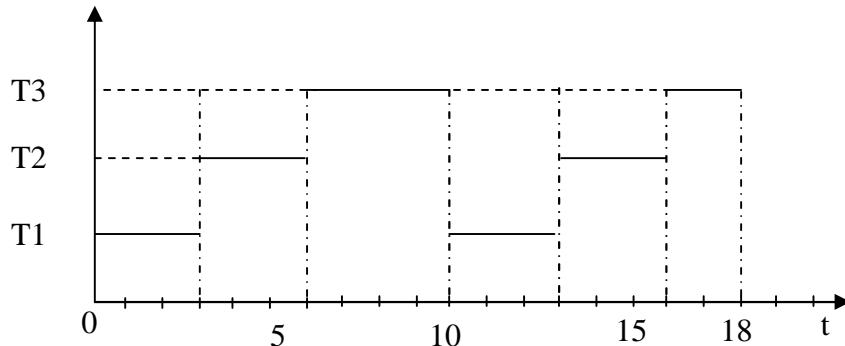

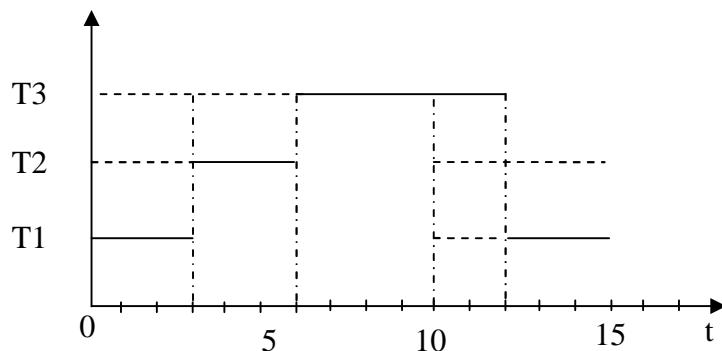

| Figure 17: Graphe de séquences avec MicroC.....                                                                                  | 61  |

| Figure 18: Graphe de séquences avec EDF.....                                                                                     | 62  |

| Figure 19: Approche de partitionnement SW/HW.....                                                                                | 63  |

| Figure 20: Environnement Design Trotter .....                                                                                    | 64  |

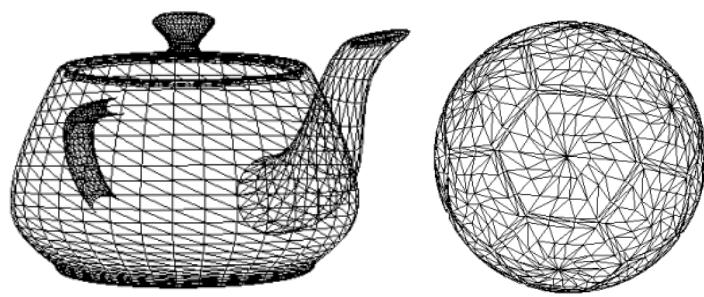

| Figure 21: Objets transformés en un ensemble de triangles .....                                                                  | 69  |

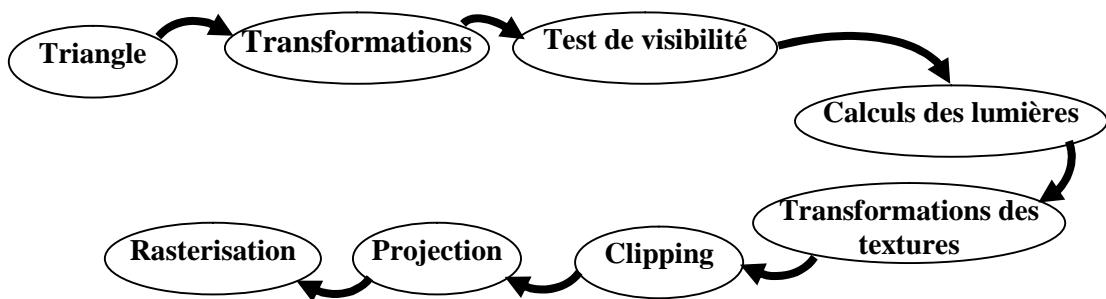

| Figure 22: Les différentes étapes du pipeline [lou04].....                                                                       | 69  |

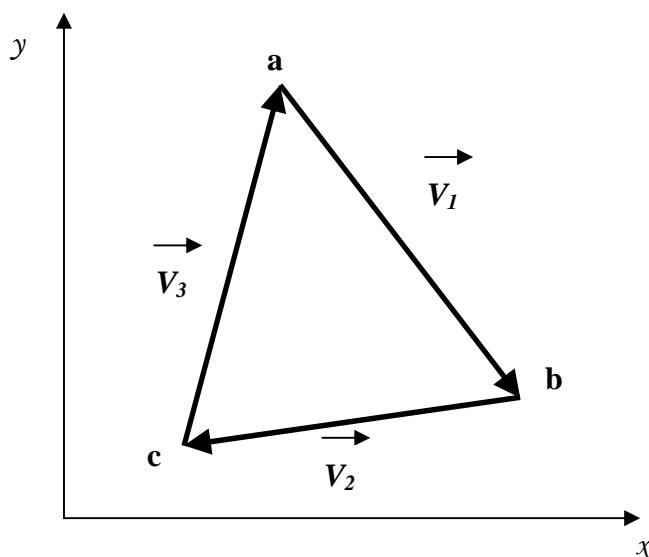

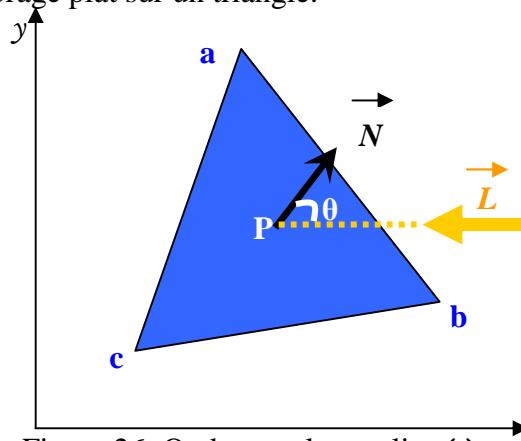

| Figure 23 : Détermination de la normale .....                                                                                    | 70  |

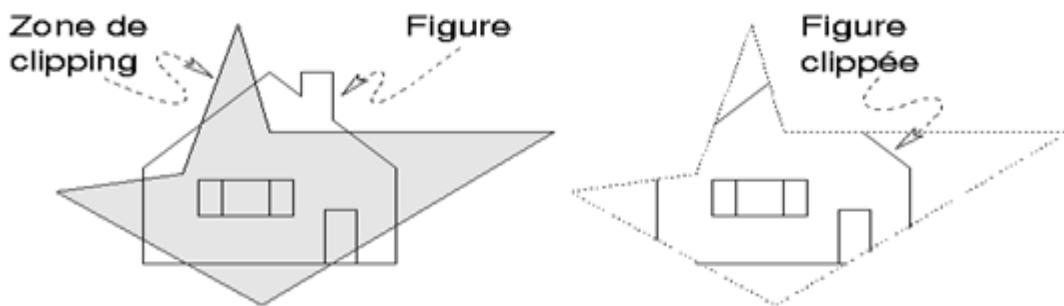

| Figure 24: Clipping d'une figure.....                                                                                            | 73  |

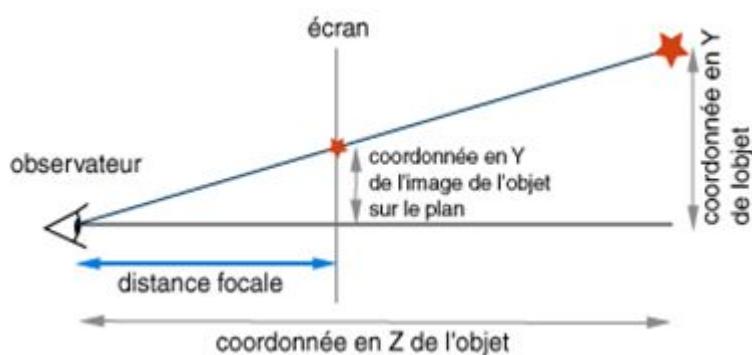

| Figure 25: Projection .....                                                                                                      | 73  |

| Figure 26: Ombrage plat appliqué à un triangle.....                                                                              | 74  |

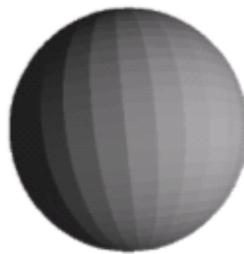

| Figure 27: Ombrage plat appliqué à une sphère.....                                                                               | 75  |

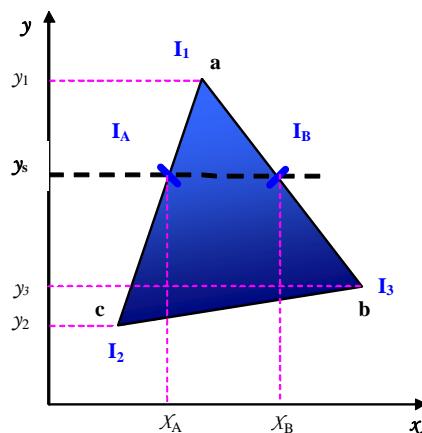

| Figure 28: Ombrage de Gouraud appliqué à un triangle.....                                                                        | 76  |

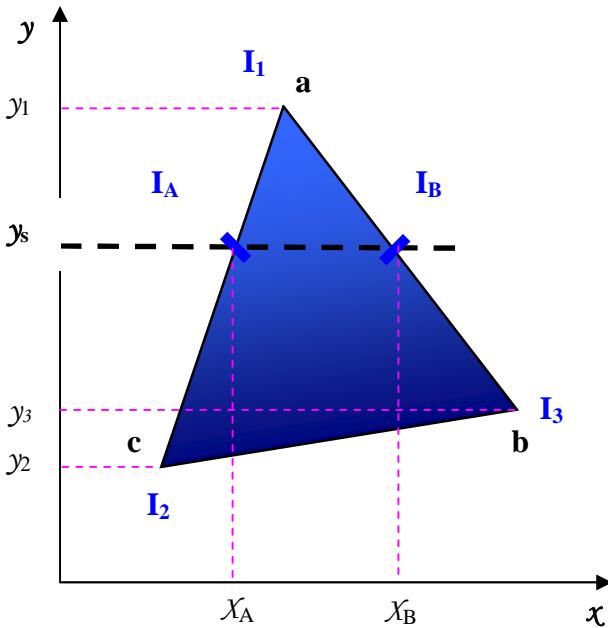

| Figure 29 : Ombrage de Gouraud appliqué à une sphère .....                                                                       | 77  |

| Figure 30: Graphe de tâche de l'application synthèse 3D.....                                                                     | 78  |

| Figure 31 : Objets 3D avec qualités différentes .....                                                                            | 79  |

| Figure 32 : Scénario du fonctionnement de l'application 3D avec les services MicroC/OS....                                       | 80  |

| Figure 33 : Schéma de la carte de développement Stratix III .....                                                                | 82  |

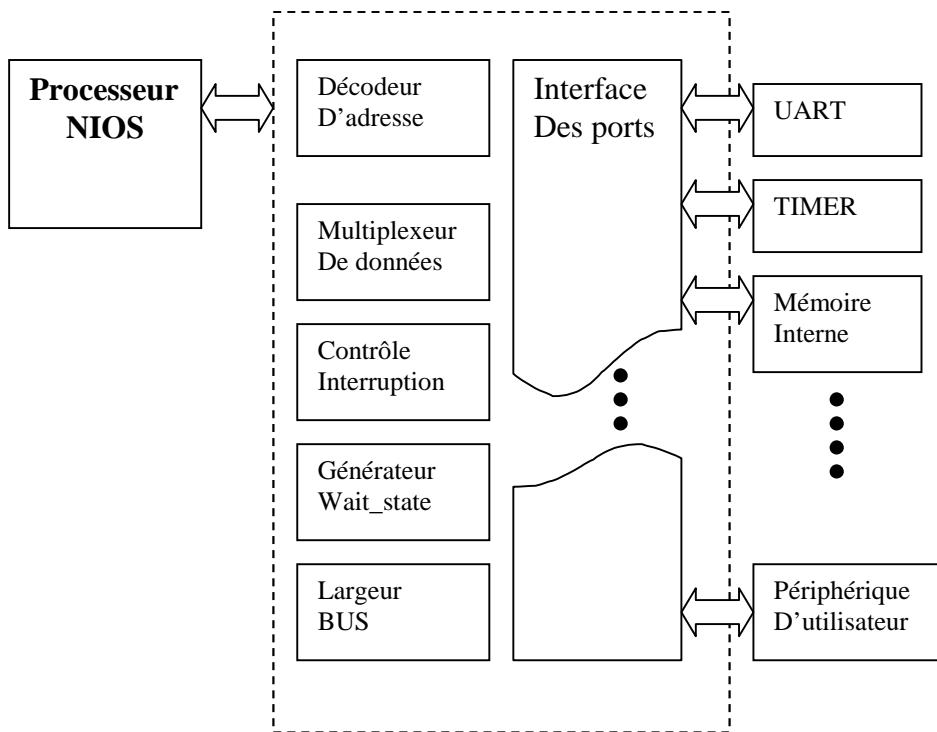

| Figure 34: CPU NIOS .....                                                                                                        | 83  |

| Figure 35: Architecture de bus Avalon .....                                                                                      | 84  |

| Figure 36: Flot de conception logiciel et matériel .....                                                                         | 86  |

| Figure 37: Structure de MicroC/OS-II .....                                                                                       | 87  |

| Figure 38: Procédure d'exécution de l'application synthèse d'images 3D .....                                                     | 94  |

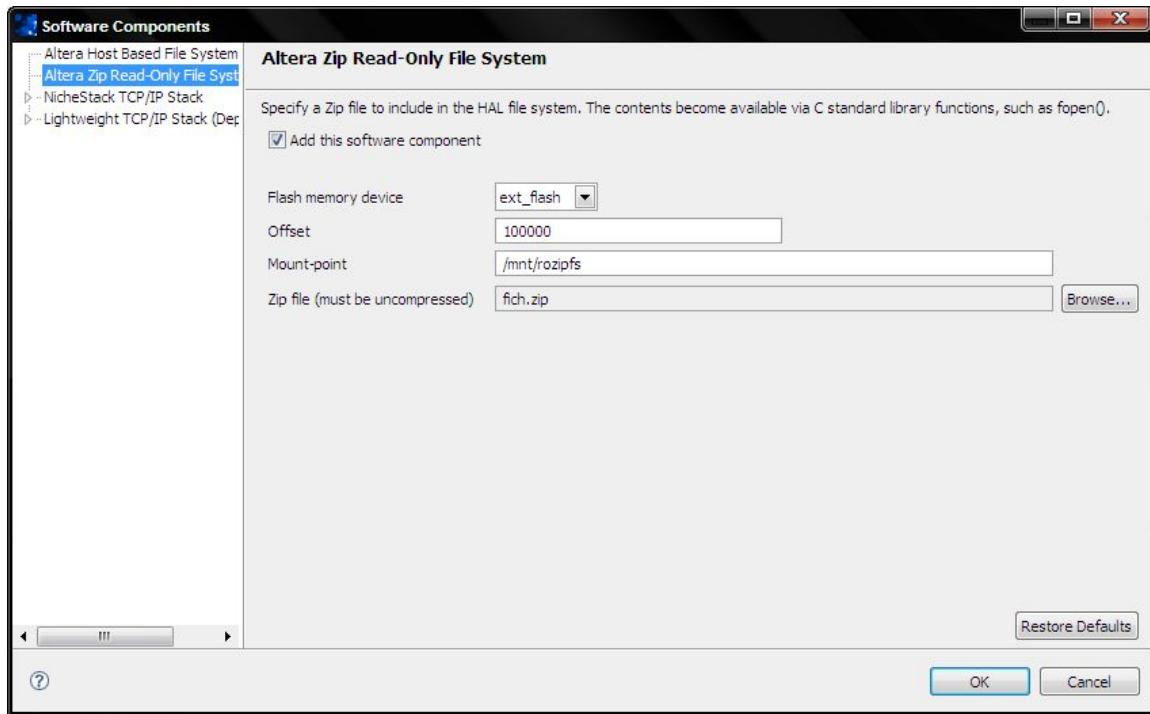

| Figure 39 : Configuration des composants logiciels .....                                                                         | 94  |

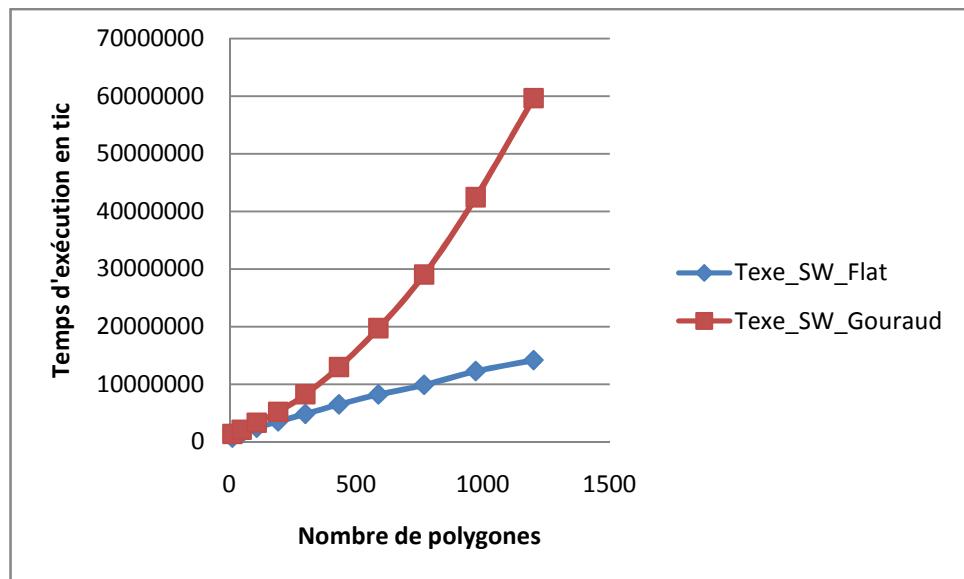

| Figure 40: Impact du changement du nombre de polygones et de l'algorithme d'ombrage sur temps d'exécution de l'application ..... | 95  |

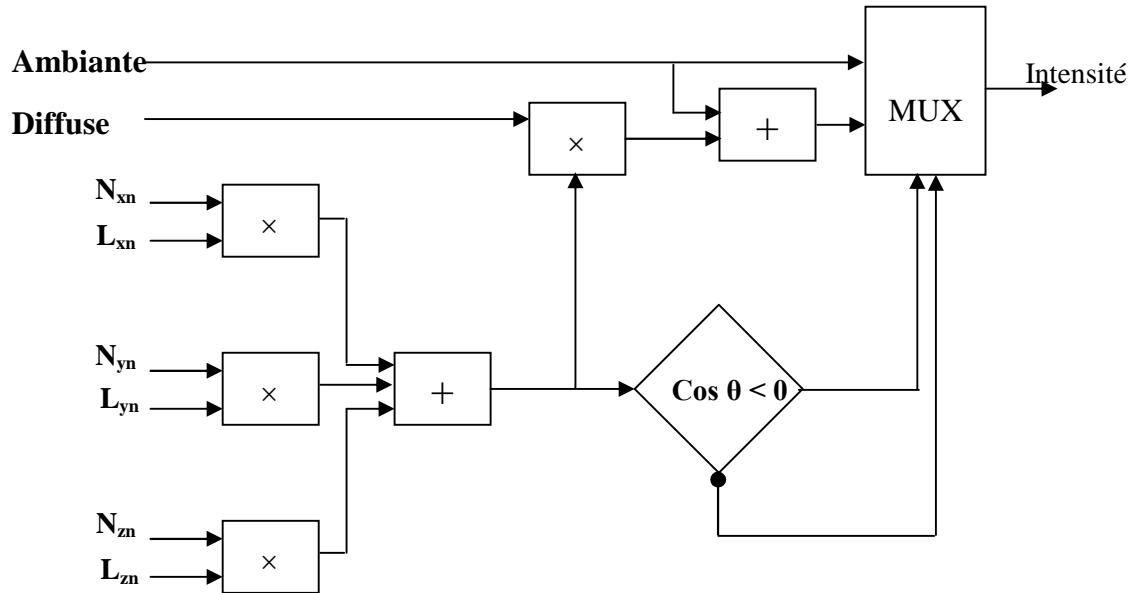

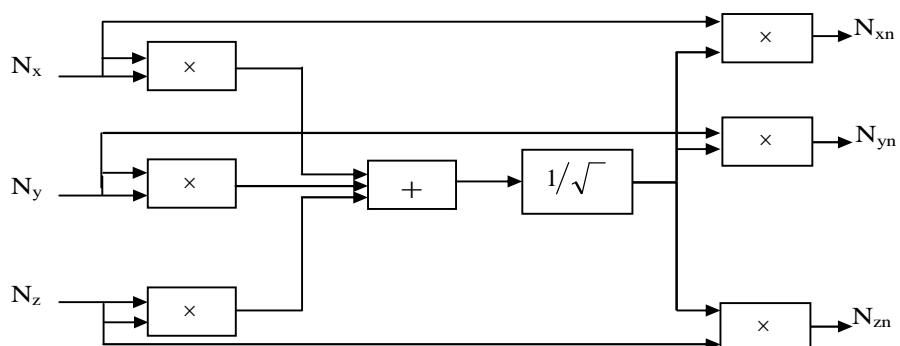

| Figure 41: Module de calcul de l'équation d'illumination de Lambert .....                                                        | 99  |

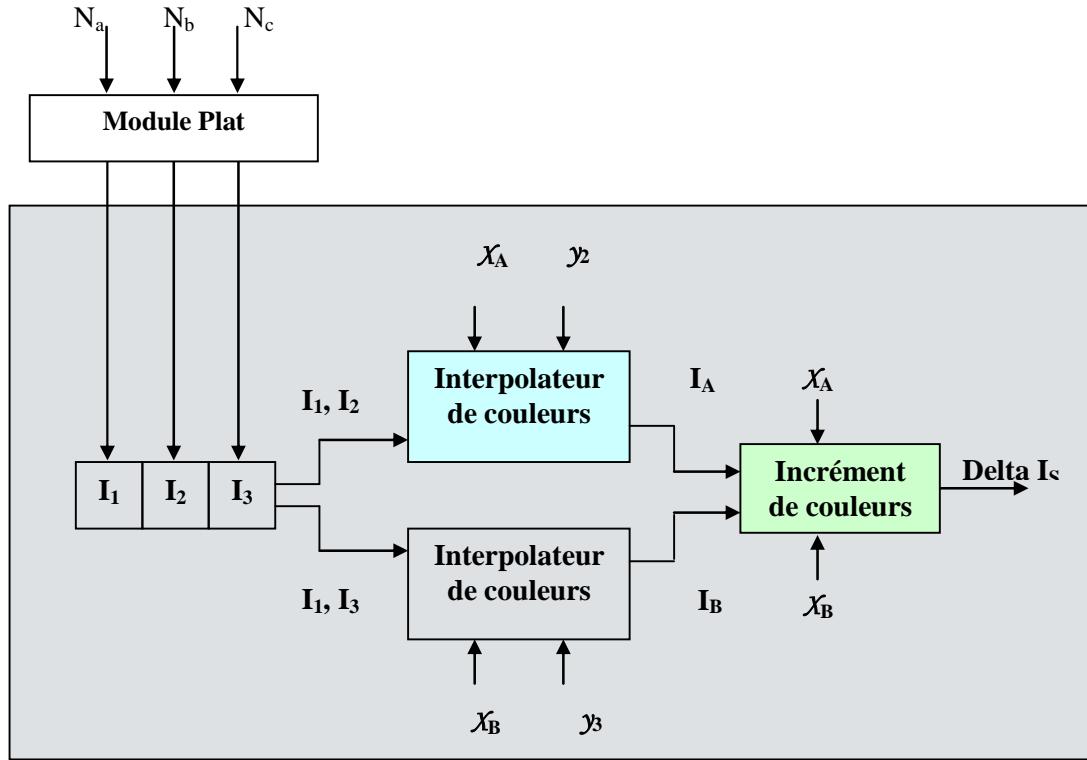

| Figure 42: Ombrage Gouraud .....                                                                                                 | 99  |

| Figure 43: Le schéma bloc d'un module d'ombrage de Gouraud.....                                                                  | 100 |

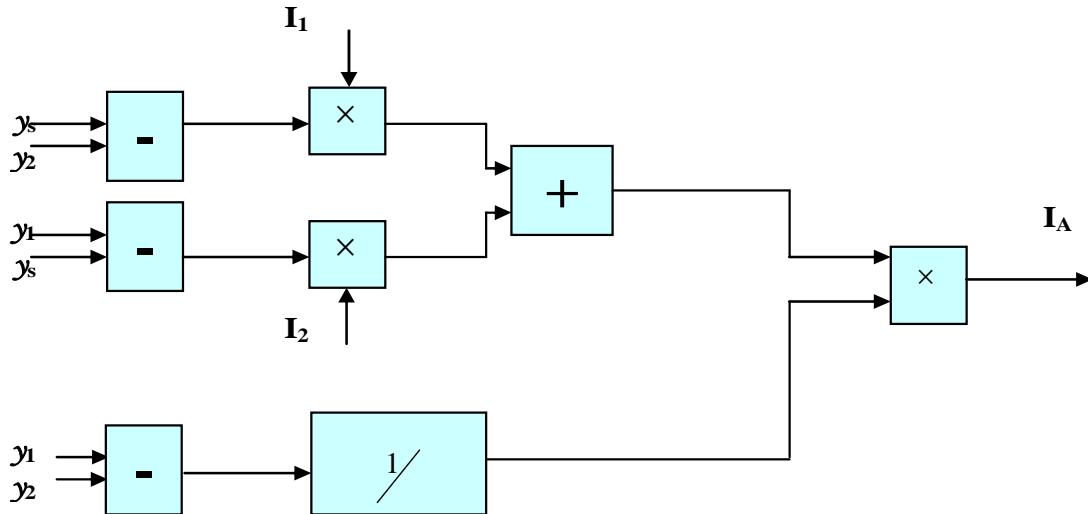

| Figure 44: Interpolateur de couleurs .....                                                                                       | 100 |

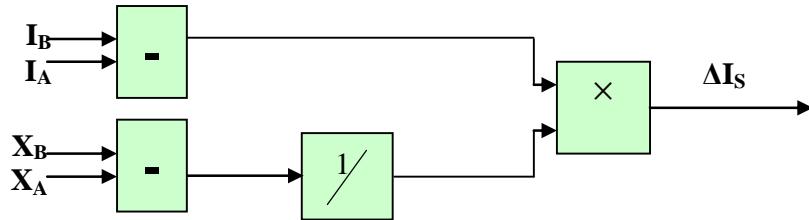

| Figure 45: Incrémentation de couleurs.....                                                                                       | 101 |

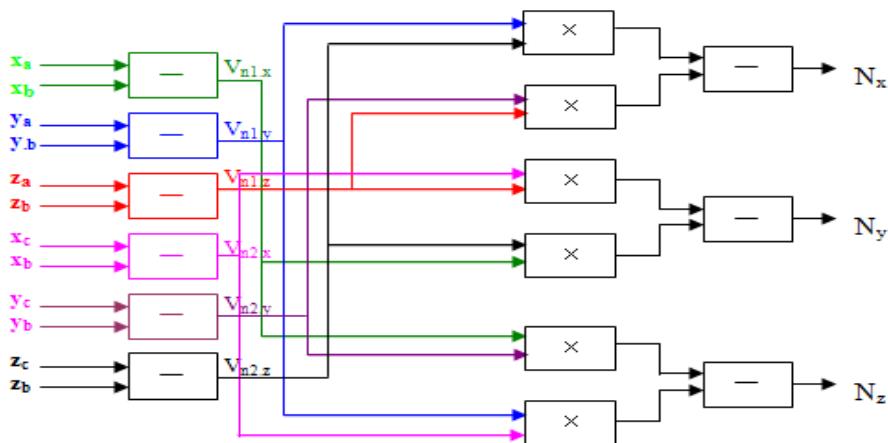

| Figure 46: Schema bloc du circuit de calcul de la normale .....                                                                  | 101 |

| Figure 47: Schéma de bloc de la normalisation d'une normale .....                                                                | 101 |

|                                                                                                                   |     |

|-------------------------------------------------------------------------------------------------------------------|-----|

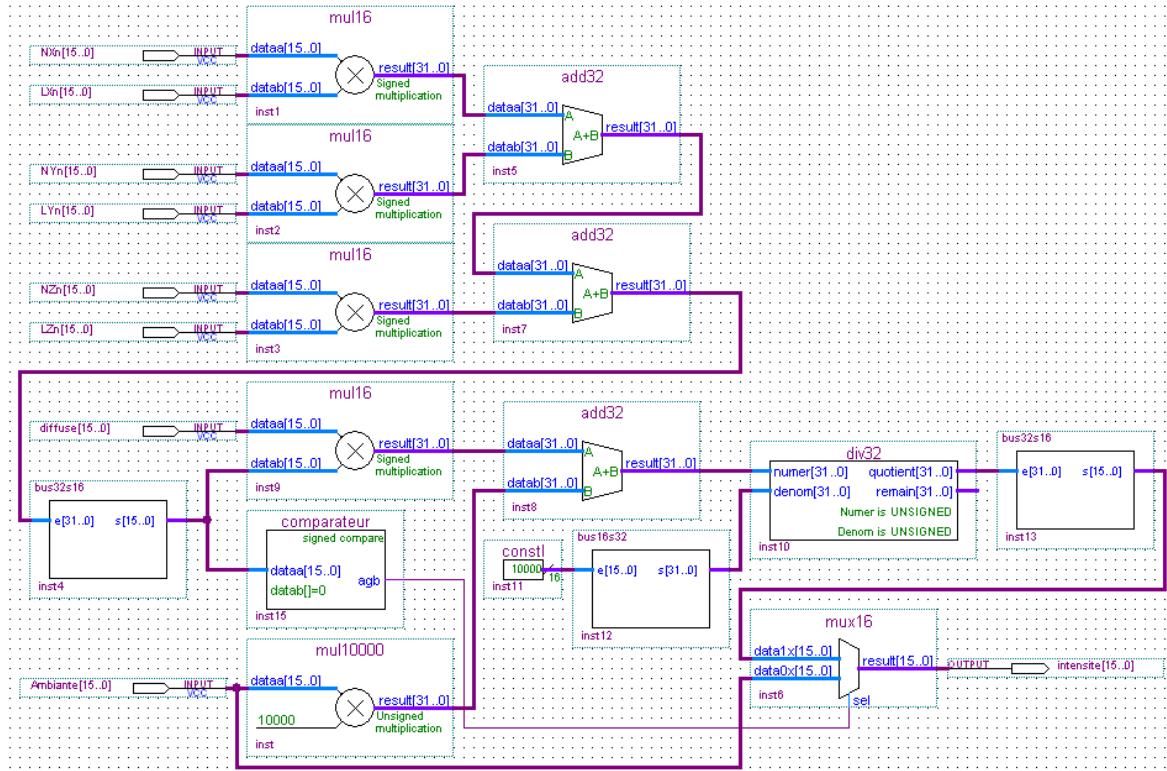

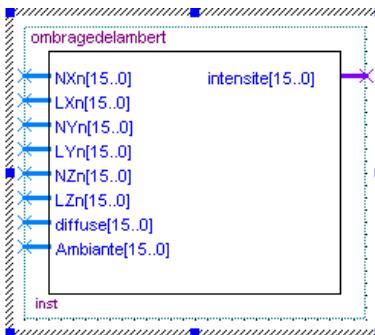

| Figure 48:Circuit de Lambert .....                                                                                | 103 |

| Figure 49: Schéma bloc de la fonction Lambert .....                                                               | 103 |

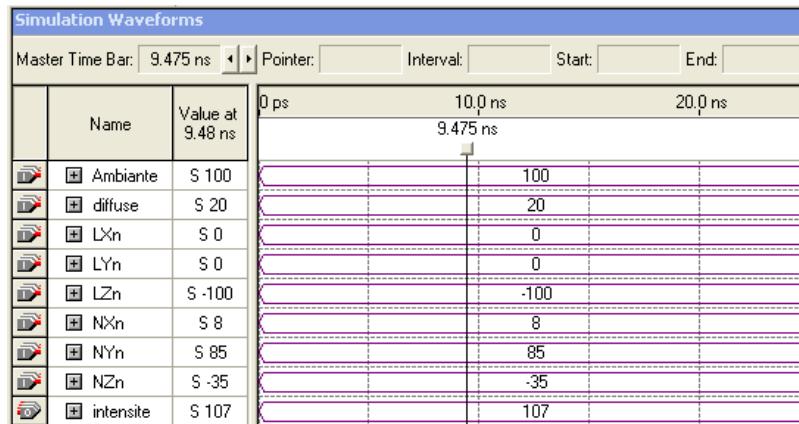

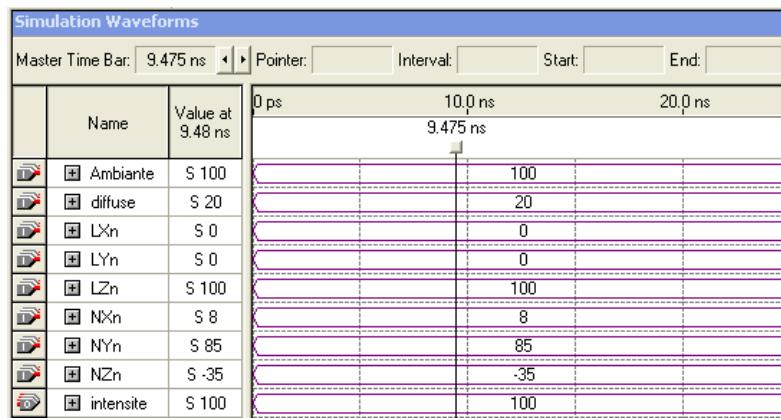

| Figure 50:Résultat de simulation du circuit de Lambert avec $\theta$ négative .....                               | 104 |

| Figure 51:Résultat de simulation du circuit de Lambert avec $\theta$ positive .....                               | 104 |

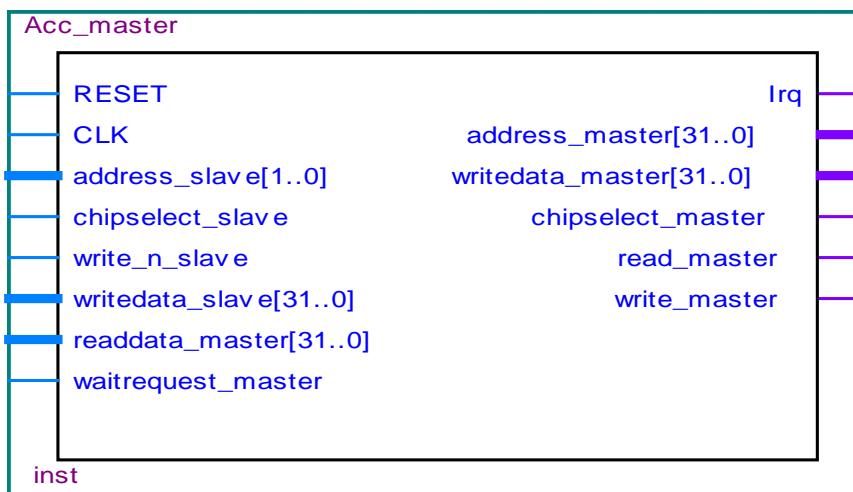

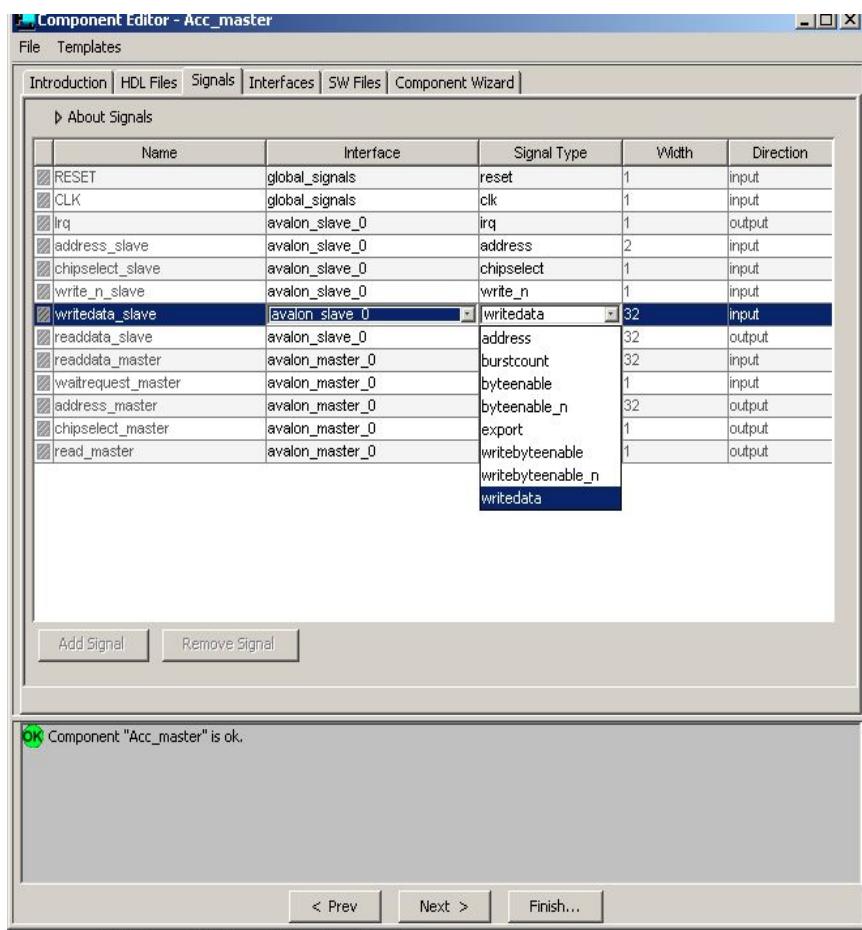

| Figure 52: Structure de l'interface de l'accélérateur maître.....                                                 | 105 |

| Figure 53: Mise au point des signaux Avalon.....                                                                  | 106 |

| Figure 54:Interface d'ajout d'accélérateur .....                                                                  | 107 |

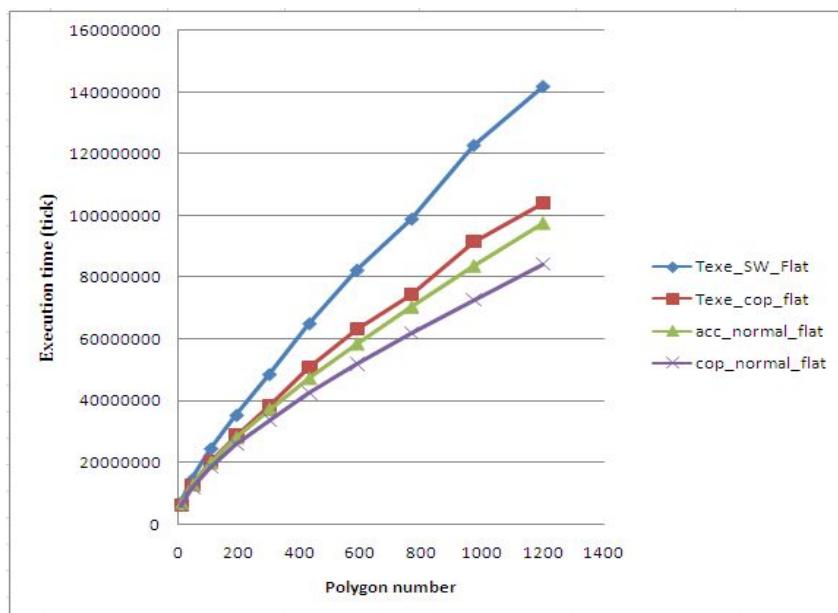

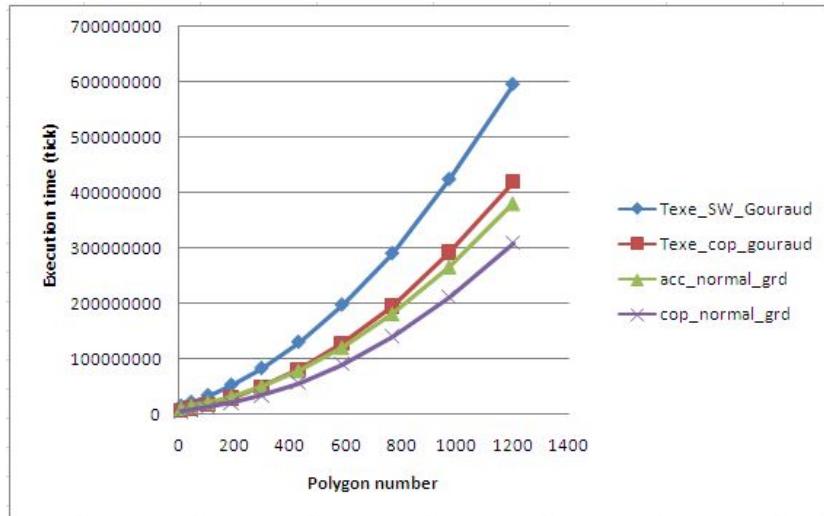

| Figure 55: Impact du changement de l'architecture sur le temps d'exécution(Plat).....                             | 108 |

| Figure 56: Impact du changement de l'architecture sur le temps d'exécution(Gouraud).....                          | 109 |

| Figure 57 : Modèle de QoS .....                                                                                   | 111 |

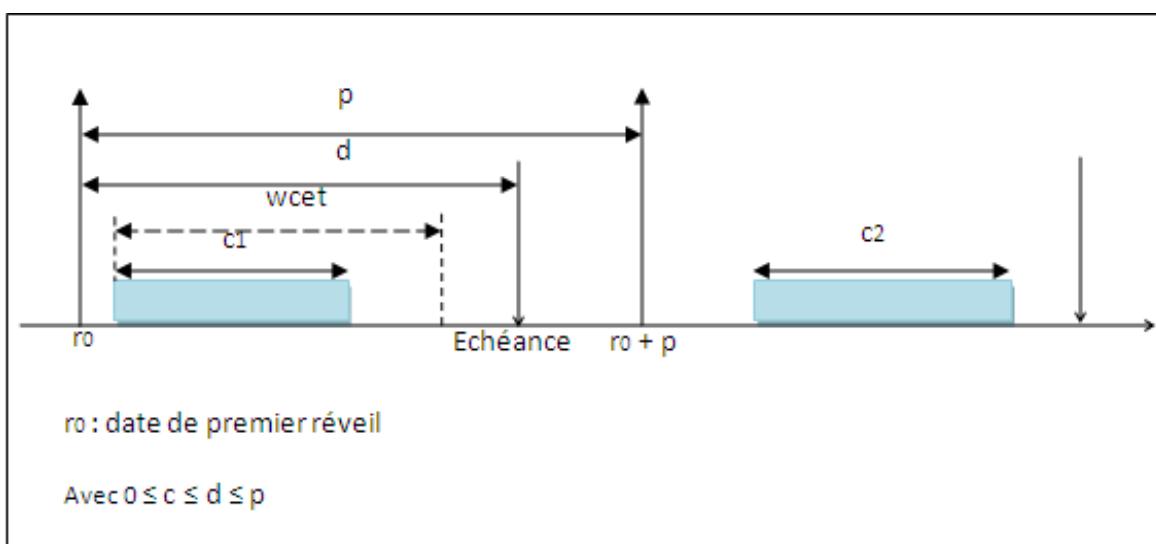

| Figure 58 : Paramètres des tâches périodiques .....                                                               | 114 |

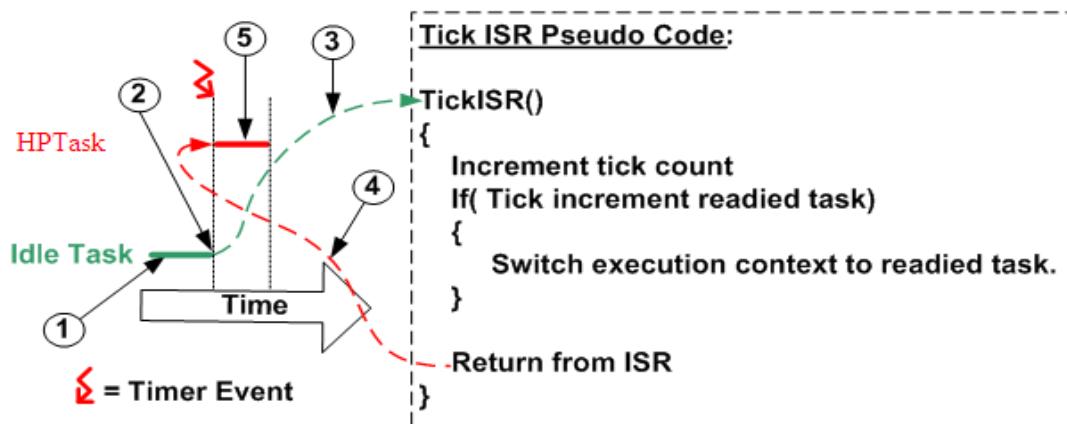

| Figure 59:Gestion du temps .....                                                                                  | 115 |

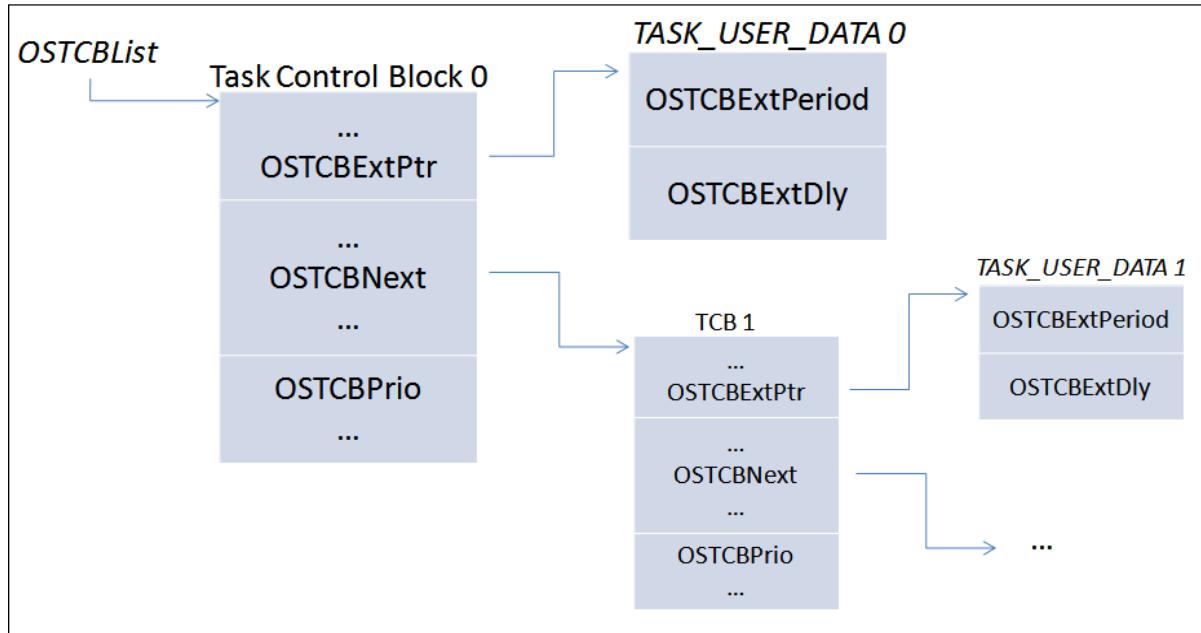

| Figure 60: Structure étendue du TCB pour le support de la périodicité des tâches .....                            | 116 |

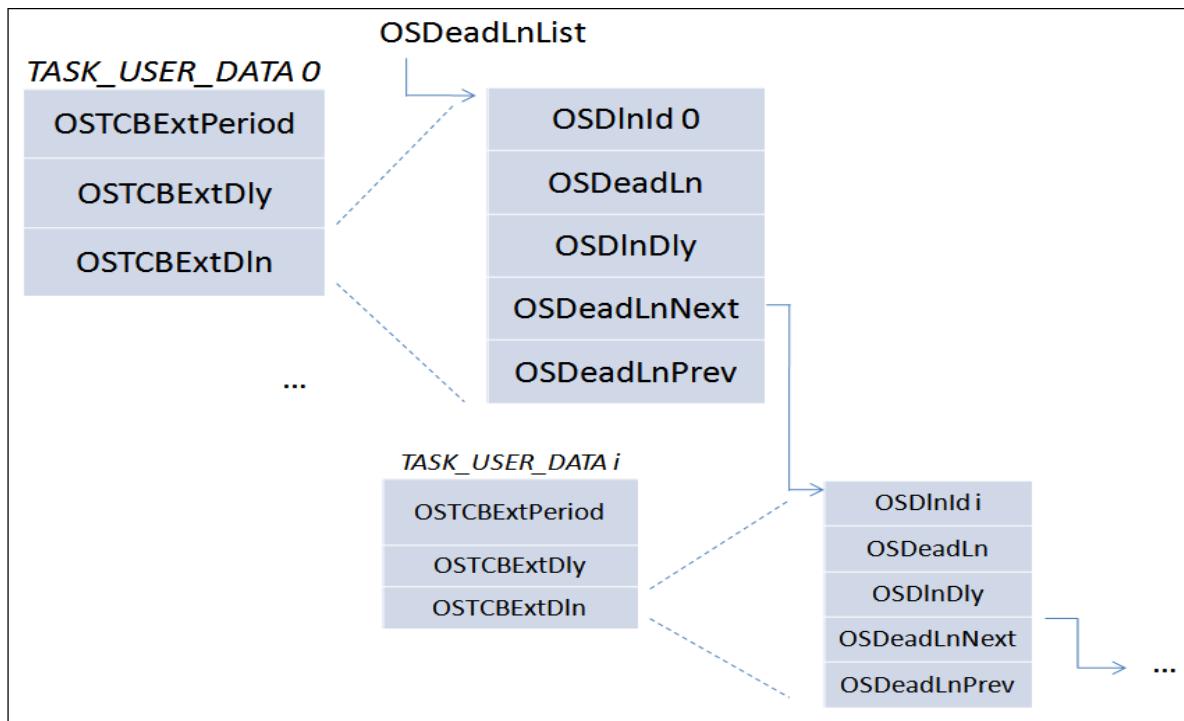

| Figure 61: Structure du deadline dans la zone d'extension du TCB pour le support d'EDF.                           | 117 |

| Figure 62 : Démarrage de l'approche d'adaptation.....                                                             | 119 |

| Figure 63: Appel de la fonction d'adaptation locale .....                                                         | 119 |

| Figure 64: Modification du nombre de tâches .....                                                                 | 120 |

| Figure 65: Activation du gestionnaire global par le gestionnaire local .....                                      | 121 |

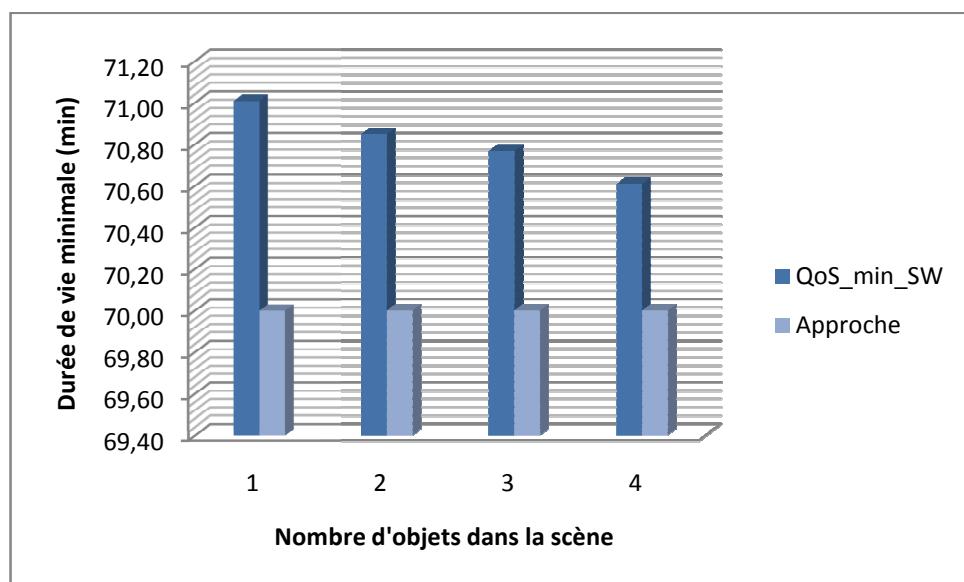

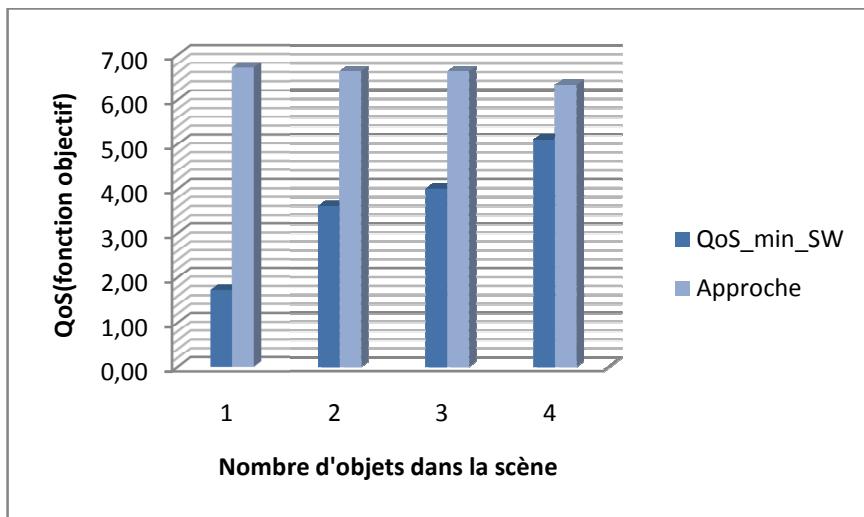

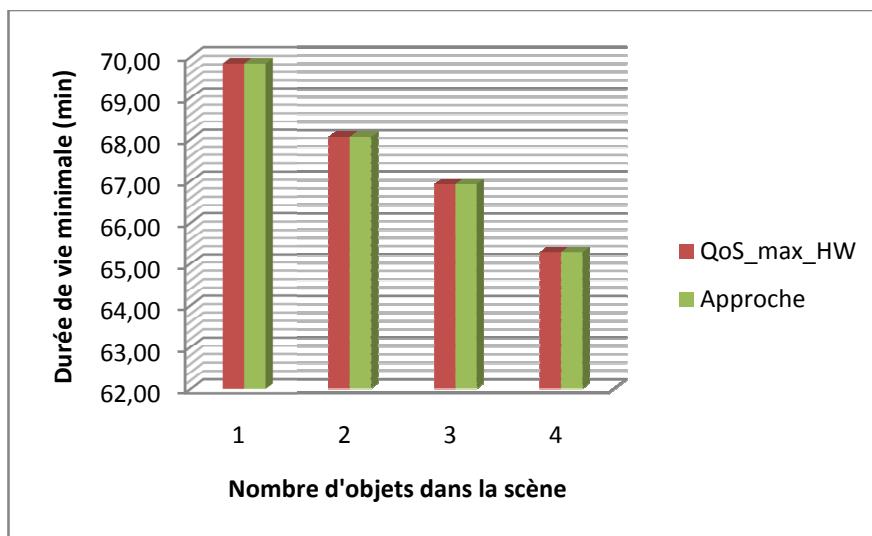

| Figure 66: Durée de vie du système version minimale .....                                                         | 122 |

| Figure 67: Variation de QoS pour une version minimale/Approche .....                                              | 123 |

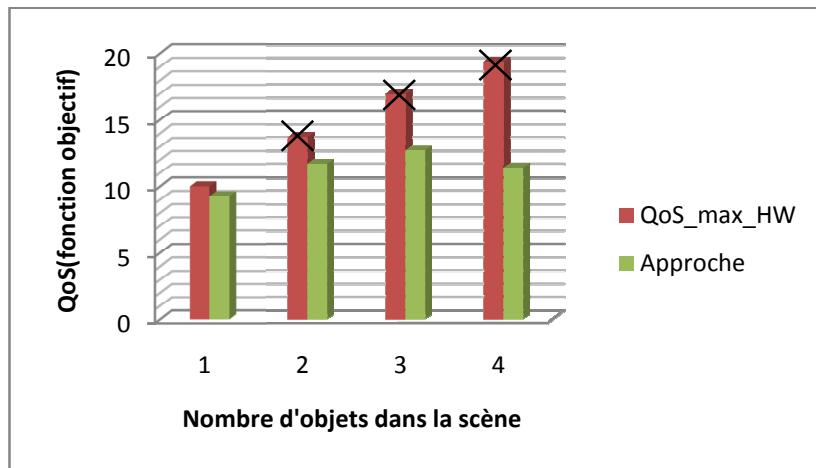

| Figure 68: Durée de vie du système version maximale .....                                                         | 123 |

| Figure 69: Variation QoS pour une version maximale/Approche .....                                                 | 124 |

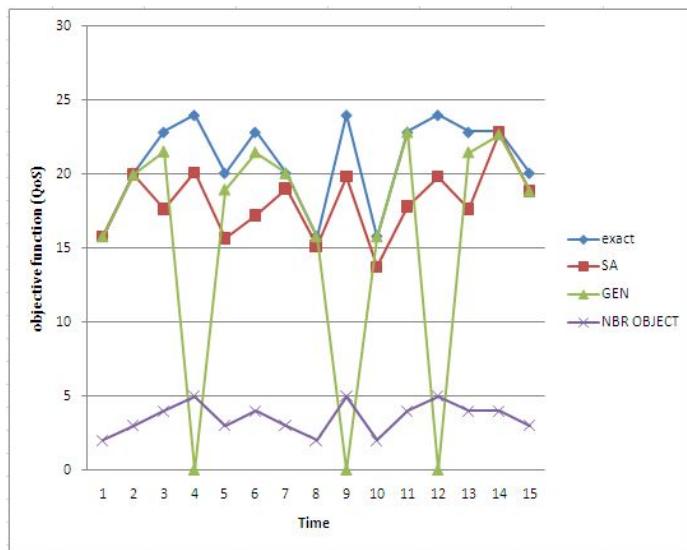

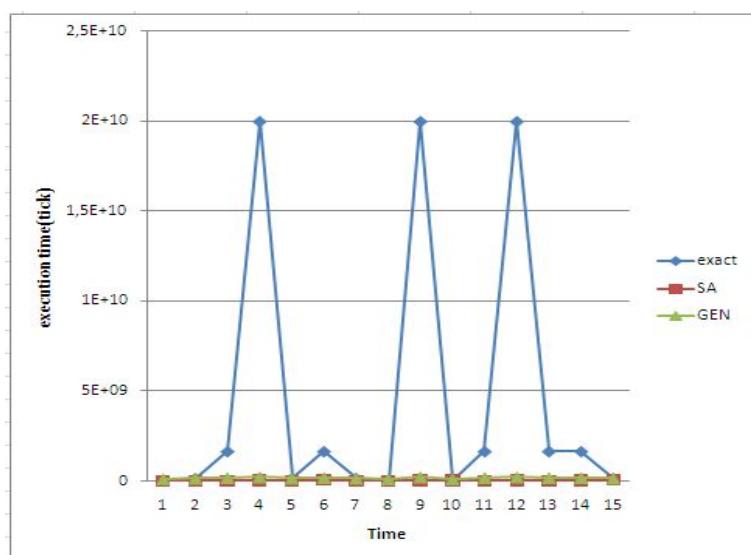

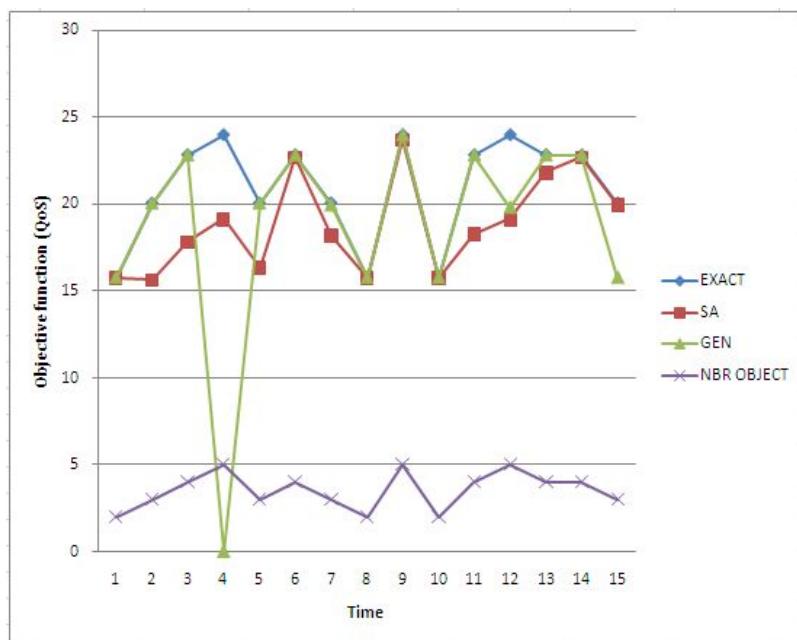

| Figure 70: Variation nbr_objet/QoS pour l'algorithme génétique (nb_it=50) et le recuit simulé (fact=0.8) .....    | 125 |

| Figure 71: Variation nbr_objet/Texe pour l'algorithme génétique (nb_it=50) et le recuit simulé (fact=0.8) .....   | 125 |

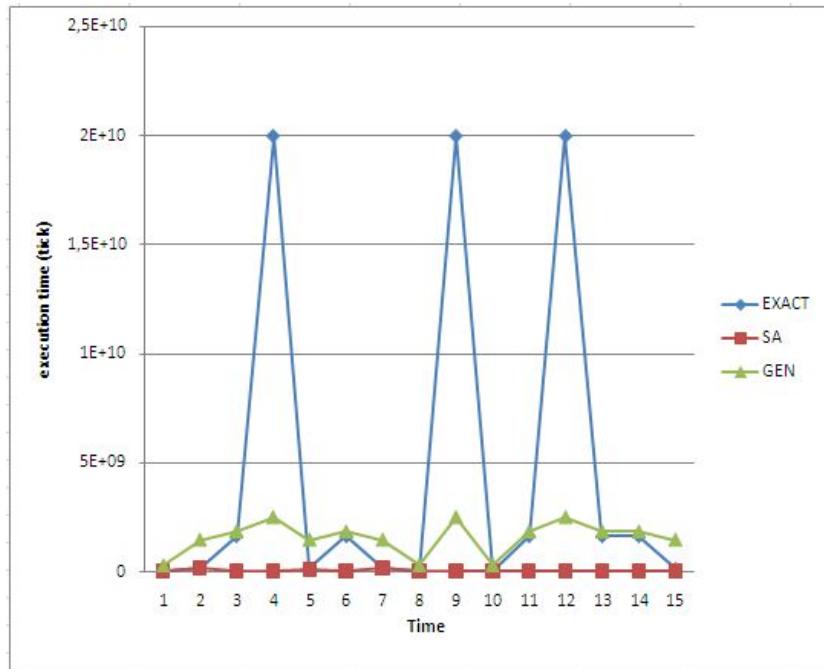

| Figure 72: Variation nbr_objet/QoS pour l'algorithme génétique (nb_it=200) et le recuit simulé (fact=0.95) .....  | 126 |

| Figure 73: Variation nbr_objet/Texe pour l'algorithme génétique (nb_it=200) et le recuit simulé (fact=0.95) ..... | 127 |

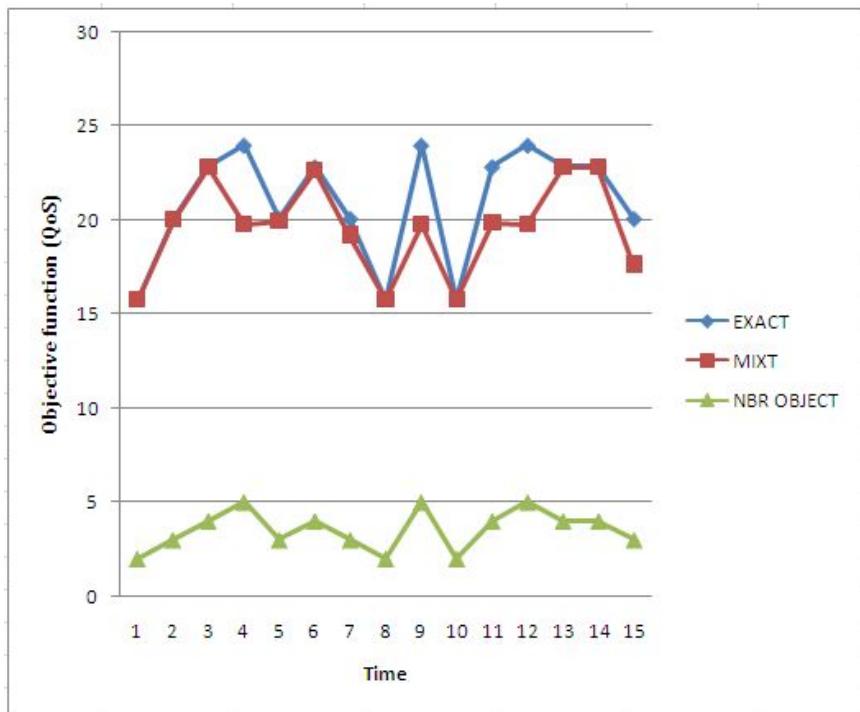

| Figure 74: Variation nbr_objet/QoS pour la méthode mixte .....                                                    | 128 |

| Figure 75 : Variation nbr_objet/QoS pour la méthode mixte .....                                                   | 128 |

## ***Liste des tableaux***

|                                                                               |     |

|-------------------------------------------------------------------------------|-----|

| Tableau 1 : Résultat de la fonction objectif avec la fonction F1 .....        | 45  |

| Tableau 2 : Résultat de la fonction objectif avec la fonction F2.....         | 46  |

| Tableau 3: Le résultat de profilage par l'outil « Performance Counter » ..... | 97  |

| Tableau 4: Les résultats des métriques par « Design Trotter ».....            | 98  |

| Tableau 5: Caractérisation de la puissance des configurations .....           | 110 |

| Tableau 6: Exemple de configurations retenues .....                           | 112 |

# **Glossaire**

- SoC System-On-a-chip

- ASIC Application Specific Integrated Circuit

- ASIP Application Specific Integrated Processor

- FPGA Field programmable gate array

- DSP Digital Signal Processing

- MIPS Million d'instructions par seconde

- QoS Quality of service

- 3D Trois dimensions

- PDA Personal Digital Assistant

- RTOS Real time operating system

- VHDL Very High Description language

- OS Operating System

- SW software

- HW hardware

- Texe Temps d'exécution

- IP Intellectual Properties

- VSIA Virtual Identification Soft IP

- TTM Time To Market

- SOPC System on programmable chip

- DDV Durée de vie

- ISR Interrupt Service Request

- EDF Earliest deadline first

# ***CHAPITRE 1: Introduction générale***

|                                         |          |

|-----------------------------------------|----------|

| <b>1 Motivation .....</b>               | <b>2</b> |

| <b>2 Contribution de la thèse .....</b> | <b>4</b> |

| <b>3 Organisation du document .....</b> | <b>6</b> |

## 1 Motivation

Depuis longtemps, on assiste à un fort accroissement du rythme des innovations technologiques dans le domaine des systèmes électroniques. Ce progrès technologique permet de répondre aux exigences des applications de plus en plus complexes de traitement de l'information (notamment dans le domaine multimédia). Il rend possible l'utilisation de ces applications non seulement sur les ordinateurs de bureau, mais aussi sur des systèmes embarqués nomades de faible encombrement. La conception de ce type de systèmes très populaire est actuellement au cœur d'enjeux économiques très importants, liés à l'expansion du marché des applications « mobiles » (téléphones portables, tablette, terminaux vidéos, etc.), à la réduction des délais de mise sur le marché et la concurrence farouche du domaine.

Jouissant des progrès scientifiques dans les domaines du traitement multimédia, et du traitement du signal, les fonctionnalités offertes par ces systèmes sont devenues de plus en plus variées et complexes. Elles demandent par conséquent des capacités de calcul de plus en plus importantes. Cet accroissement persistant en complexité est également justifié par l'évolution de la technologie qui permet de réaliser de tels systèmes sur une seule puce de silicium. En effet, selon la loi de Moore [Moo65], la densité d'intégration augmente de 50% chaque année. Ce qui permet de créer des systèmes mixtes (logiciel/matériel) hétérogènes comportant divers modules (comme des processeurs, des DSP, des ASIP, etc) sur une même puce (SoC).

Ces nouvelles générations de systèmes posent néanmoins de nouveaux défis aux concepteurs. Avec un tel niveau de complexité, les phases de conception de ces systèmes sur puce deviennent de plus en plus ardues (spécification initiale, simulation, fabrication, tests ...) vu le nombre et la nature des applications à gérer, la nature hétérogène de l'architecture et surtout les délais courts de temps de mise sur le marché (time to market) avec toujours la nécessité d'un « zero default ».

Afin de mettre en place un système informatique, les concepteurs ont longtemps disposé d'un choix restreint à deux alternatives. La première consiste à mettre en place un système multiprogrammé via un microprocesseur [Zhi08]. Cette solution est moins couteuse mais elle n'arrive pas assurer l'exécution de toutes les fonctionnalités du système avec la qualité requise. La seconde, se base sur la réalisation d'un circuit spécifique à l'application développée (ASIC) [Kri09]. De même cette solution souffre de quelques handicaps tels que la complexité de la phase de conception et le temps de fabrication du produit final. Comme solution la technologie programmable offre plus de flexibilité au produit final avec un temps de conception et un coût

assez réduit.

Les circuits reconfigurables correspondent à des circuits matériels dont l'architecture peut être modifiée en fonction de l'application à développer [Gan10, Kon05]. Les plus populaires sont les circuits FPGA. Ces circuits permettent de faciliter la phase de mise en place d'un nouveau système multimédia (de la spécification au prototypage). En effet, leur architecture est riche et répond aux besoins des applications actuelles. De plus, leur nature reconfigurable réduit les phases de test, le coût associé aux erreurs de conception et le temps de mise sur le marché. Ces architectures se présentent comme une solution intéressante au défi des systèmes sur puce. Elles ont permis la conception de nouvelles applications bénéficiant de leurs caractéristiques propres telles qu'un fort parallélisme matériel et des possibilités de reconfiguration statique et/ou dynamique.

Malgré toutes ces améliorations technologiques, l'implémentation d'applications multimédia sur un système embarqué reste une tâche compliquée qui doit répondre à un ensemble de contraintes antagonistes.

L'une des contraintes est la complexité des applications supportées. En effet, ces nouvelles fonctionnalités sont exigeantes aussi bien au niveau puissance de calcul que capacité mémoire. Elles sont en même temps très consommatrices d'énergie. La norme de compression MPEG4 par exemple est d'une complexité beaucoup plus importante que ses deux prédecesseurs MPEG1 ou MPEG2 puisqu'elle est destinée à couvrir un ensemble plus vaste d'applications [Tou00]. A titre d'exemple, l'encodage (profil simple) de la séquence "Weather" à 10 image/s au format QCIF (qualité moyenne de vidéo) demande un total de 1500 MIPS avec plus de 250 millions d'accès mémoire [Kim03]. Cette augmentation de la complexité implique aussi une consommation en énergie plus importante, ce qui limite l'autonomie des systèmes embarqués.

Une autre contrainte est la gestion de la consommation. C'est une tâche très difficile compte tenu le nombre de facteurs favorisant son augmentation. D'une part, le nombre et la nature des fonctionnalités multimédia supportées par un système embarqué ne cessent d'évoluer. D'autre part, le progrès technologique n'a pas apporté de solutions acceptables à ce problème. En effet, si la technologie autorise la réduction de la taille des transistors permettant ainsi de diminuer les tensions d'alimentation et donc la consommation dynamique, elle entraînera une augmentation relative des courants de fuite et donc de la consommation statique négligée auparavant. En plus l'augmentation de la densité d'intégration sur la même puce permet de réaliser des architectures assez complexes ; ce qui favorise la consommation [Kuh98].

L'exécution temps réel est une contrainte pour les systèmes temps réel. Diverses applications nécessitent une exécution en un temps limité et continu dans le temps pour des raisons de sécurité (dans le cas par exemple d'un système de navigation aérien) où pour des raisons de confort visuel (dans le cas de la compression vidéo par exemple, il faut assurer une cadence de 25 image/s soit un temps de traitement de 40 ms/image).

Une autre contrainte des systèmes embarqués est liée à la nature mobile des systèmes électroniques actuels. Il est nécessaire de tenir en compte un autre paramètre externe cette fois qui est l'environnement où évolue le système mobile. Perturbations atmosphériques, liaison radio variable, flux de données changeant sont des exemples de paramètres qui peuvent influencer de façon importante sur le fonctionnement du système et la qualité des services offerts (QoS).

De ce fait, ces systèmes doivent être d'une part performants pour pouvoir traiter les applications multimédia complexes et d'autre part flexibles pour s'adapter à l'environnement externe variable non seulement pour respecter les contraintes temps réel, mais aussi afin de préserver les ressources d'énergie du système et respecter ainsi la contrainte de durée de vie [Lic06, Kri08]. Le challenge consiste à concevoir des systèmes qui donnent une bonne qualité de service avec une consommation limitée d'énergie. Mais ce but de conception est difficile à atteindre puisque pour avoir une meilleure qualité de service il faut utiliser au maximum les ressources du système ce qui augmente la consommation du système. Il apparaît ainsi important de pouvoir moduler l'utilisation des ressources matérielles selon les besoins de l'application d'une part et également en tenant compte des paramètres externes au système d'autre part.

Tirant partie de ce fait, les concepteurs des systèmes embarqués se trouvent devant un compromis entre la QoS à fournir et l'utilisation des ressources d'énergie et de calcul. Il est alors nécessaire de définir des systèmes adaptatifs qui permettent d'adapter leur fonctionnement non seulement suivant les contraintes du système mais aussi suivant les préférences de l'utilisateur et l'état de l'environnement externe.

## **2 Contribution de la thèse**

Le but de la thèse est de définir un système multimédia adaptatif capable de gérer de façon autonome et efficace ces ressources d'énergie et de calcul pour produire un maximum de QoS tout en respectant les contraintes d'énergie et performance.

Notre approche prend en compte un certain nombre de contraintes qui agissent sur les performances d'un système multimédia embarqué pendant son exécution. Elles se situent à

différents niveaux:

- Type de données traitées. Une tâche peut voir ces caractéristiques (temps d'exécution, occupation mémoire, consommation) changer en fonction des données traitées (valeur, quantité, type).

- Influence du contexte dans lequel évolue le système embarqué. L'augmentation du taux d'erreur de transmission par exemple des données peut imposer le changement de l'algorithme de décodage et de correction utilisé et donc une augmentation de la consommation.

- Influence des choix d'applications. L'utilisateur peut privilégier l'exécution de certaines fonctionnalités de son système mobile aux dépends d'autres qu'il peut désactiver. Ceci engendre des changements de la consommation d'énergie à une sollicitation plus importante des ressources du système.

- Influence du niveau d'énergie de la batterie. La quantité d'énergie disponible dans le système peut imposer un mode de fonctionnement particulier ayant un niveau de performance limité.

Diverses techniques ont été proposées [Kan11, Pha04, Yua06] pour le respect des contraintes du système tout en donnant une meilleure qualité de service. Ces techniques peuvent intervenir dans l'une des couches application, système d'exploitation ou architecturale telles que l'ajustement de la tension d'alimentation ou la fréquence de fonctionnement du système, la gestion optimisée des accès mémoires, l'utilisation des techniques d'ordonnancement de basse consommation et la modification de l'apparence d'un objet 3D sur l'écran.

Nous proposons dans cette thèse une nouvelle approche multi couches combinant l'adaptation au niveau RTOS, applicatif et architectural.

Le modèle d'adaptation proposé doit être performant sans pour autant être trop complexe pour ne pas contribuer à dégrader les performances du système et ses ressources d'énergie.

Dans ce contexte se situe notre travail qui consiste à ajouter une couche middleware (couche intergiciel entre la couche système exploitation et application) permettant l'auto adaptation du système. Nous proposons une approche originale et générique d'adaptation qui comporte essentiellement deux gestionnaires (global manager and local manager). Le gestionnaire global peut intervenir dans les trois couches afin de répondre aux grandes variations des contraintes du système (QoS et énergie). Le gestionnaire local intervient seulement dans les couches application et système d'exploitation. Il est mis en place pour contrôler le respect de la contrainte temps réel

du système. En cas de besoin ce dernier peut interroger le gestionnaire global pour reconfigurer la totalité du système s'il ne peut plus modifier les paramètres applicatifs de l'application pour résoudre le problème localement.

Le principe de fonctionnement de cette approche se base sur l'utilisation d'un jeu de configurations pour chaque application, pré-caractérisées hors ligne. A chaque fois que cette approche détecte un non respect des contraintes du système, elle intervient pour choisir une nouvelle configuration pour chaque application présente sur le système. Compte tenu du nombre croissant d'applications que les systèmes actuels peuvent exécuter simultanément et la présence de plusieurs configurations pour chaque application notre approche doit résoudre un problème NP-complet pour trouver une combinaison de configuration qui lui permet de respecter ses contraintes. Partant du fait que la tâche d'adaptation ne doit pas dégrader les performances du système on a eu recours à des méthodes d'optimisation (algorithme génétique et recuit simulé) pour résoudre ce problème NP-complet.

### **3 Organisation du document**

Le manuscrit de cette thèse est organisé en six chapitres :

#### **Chapitre 2: conception des systèmes sur puce adaptatifs : état de l'art**

La première partie du deuxième chapitre est consacrée à la présentation du flot de conception traditionnel des systèmes sur puce ainsi que les facteurs qui ont favorisé l'ajout de l'aspect adaptatif. Dans la deuxième partie de ce chapitre, une étude sur les approches d'adaptations existantes dans la littérature sera présentée ; nous présentons aussi l'apport et les limites de chacune d'entre elles. Nous clôturons cette partie par une synthèse des travaux existants et l'introduction de l'approche d'adaptation multicouche proposée.

#### **Chapitre 3 : approche d'adaptation multicouche**

Ce chapitre est consacré à la description des étapes et les différentes techniques qui ont conduit à la mise en place de l'approche d'adaptation. A ce niveau, nous détaillons les trois étapes (observation, adaptation et mise en place de la base des configurations) nécessaires pour la mise en place de l'approche d'adaptation proposée. Au niveau de la tâche d'observation, une nouvelle technique de contrôle du respect de la contrainte temps réel est proposée. Pour la réalisation de l'étape d'adaptation, on a présenté quelques méthodes d'optimisation pour le choix des configurations adéquates du système. Afin de mettre en place la base des configurations, une approche de partitionnement hardware software a été proposée ainsi qu'un ensemble de modèles qui permet de caractériser chaque configuration en termes de consommation, temps d'exécution et

niveau de qualité de service qui ont été développés.

#### **Chapitre 4 : étude de cas**

Le quatrième chapitre présente les éléments nécessaires de notre étude de cas faite à travers l'application de synthèse d'images 3D et l'environnement de conception Hardware/software d'Altera. Nous clôturons ce chapitre par la présentation du système d'exploitation temps réel MicroC\_OS-II.

#### **Chapitre 5 : expérimentation et validation**

Le cinquième chapitre illustre, dans sa première partie, les étapes nécessaires pour la mise en place de l'approche décrite dans le troisième chapitre sur la plateforme de conception. La deuxième partie illustre les résultats expérimentaux de l'exécution de l'application de synthèse d'images 3D sur la plateforme conçue.

#### **Chapitre 6 : conclusions et perspectives**

Nous concluons cette thèse par le bilan des travaux effectués et nous détaillons les contributions apportées ainsi que la réponse à la problématique abordée avant de proposer quelques perspectives à nos travaux.

# ***CHAPITRE 2 : Conception de système sur puce adaptatif : état de l'art***

|          |                                                  |           |

|----------|--------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction .....</b>                        | <b>9</b>  |

| <b>2</b> | <b>Système embarqué.....</b>                     | <b>9</b>  |

| 2.1      | Domaines d'application .....                     | 10        |

| 2.2      | Caractéristiques des systèmes embarqués.....     | 10        |

| <b>3</b> | <b>Conception de système embarqué .....</b>      | <b>12</b> |

| 3.1      | Flot de conception Logiciel/Matériel.....        | 13        |

| 3.2      | Gestion de la consommation.....                  | 16        |

| 3.3      | Techniques de réduction de la consommation ..... | 17        |

| 3.4      | Approches de codesign faible consommation .....  | 20        |

| 3.5      | Limitations des approches présentées.....        | 21        |

| <b>4</b> | <b>Méthodologies d'adaptation .....</b>          | <b>23</b> |

| 4.1      | Adaptation au niveau matériel .....              | 24        |

| 4.2      | Adaptation au niveau système d'exploitation..... | 25        |

| 4.3      | Adaptation au niveau applications .....          | 26        |

| 4.4      | Approches d'adaptation existantes .....          | 27        |

| 4.5      | Discussion.....                                  | 33        |

| <b>5</b> | <b>Conclusion.....</b>                           | <b>33</b> |

## 1 Introduction

La complexité croissante des applications actuelles nécessite des performances de plus en plus importantes, par ailleurs, afin de répondre à la contrainte imposée par le marché (time to market), la conception des systèmes embarqués multimédia impose l'utilisation des méthodes de conception spécifiques et performantes. Ces méthodes s'intègrent dans les méthodes de conception mixte logiciel/matériel (codesign).

Par ailleurs la diversité des contraintes auxquelles doivent répondre les systèmes embarqués (augmentation de la puissance de calcul, diminution de la consommation d'énergie, réduction des coûts, flexibilité), l'utilisation des méthodes de conception traditionnelle ne répond plus aux besoins des concepteurs. Des travaux de recherche sont menés afin de combler les limites en ajoutant de nouveaux facteurs dans les méthodes de conception traditionnelle.

Le but de ce chapitre est de présenter les notions de base reliées au domaine de conception des systèmes sur puce. Nous énumérons également, les limites du flot de conception traditionnelle. Nous terminons la première partie de ce chapitre par la présentation de nouvelles tendances pour la conception des systèmes embarqués. La deuxième partie de ce chapitre sera consacrée à la présentation des différents niveaux d'adaptation ainsi que quelques approches existantes qui traitent la notion d'adaptation dans les systèmes embarqués.

## 2 Système embarqué

Tout d'abord nous définissons l'élément de base de notre travail qui est le système embarqué (plus spécifiquement un système sur puce « SoC en anglais System-on-Chip »).

Un SoC est un système complexe et indépendant sur une seule puce. Il contient au moins un processeur (partie SW), de la mémoire sur puce, des composants spécifiques pour un traitement donné (accélérateur ou coprocesseur matériel HW), des périphériques externes (clavier, écran, interface d'entrées, sorties) peuvent compléter le fonctionnement du système [Hen99]. Il intègre dans la plupart des cas une interface homme/machine et il est géré par un système d'exploitation puisqu'un SOC peut être interfacé avec le monde réel. Il peut souvent incorporer des composants analogiques.

## **2.1 Domaines d'application**

Actuellement, les systèmes embarqués ont envahi beaucoup de domaines tels que l'astronautique (satellite artificiel, fusée, sonde spatiale), le militaire (fusée), le transport (aéronautique, automobile, avionique) et surtout la télécommunication (téléphonie, routeur, pare-feu, serveur de temps, téléphone portable). Cette large gamme de domaine d'utilisation englobe aussi les produits d'électroménager (télévision, four à micro-ondes), d'impression (imprimante multifonctions, photocopieur), d'informatique (disque dur, lecteur de disquette), le multimédia (console de jeux vidéo, tablette). D'autres domaines d'application prospèrent de l'évolution des systèmes embarqués dont on peut citer les guichets automatiques bancaires, l'équipement médical, l'automate programmable industriel ou la métrologie [Fré00].

## **2.2 Caractéristiques des systèmes embarqués**

### **2.2.1 Encombrement**

La plupart des systèmes embarqués actuels sont conçus pour répondre à une contrainte d'encombrement (petite taille et faible poids) tels que les téléphones portables les PDA etc). La fabrication de ces systèmes fait appel à une technologie d'électronique et de logiciel portable qui favorise la réduction aussi bien de l'encombrement que de la consommation. Par conséquent, la mise en place d'un système embarqué de faible surface qui englobe de l'électronique numérique, analogique et des composants radio fréquence est une tâche assez complexe [Ben07].

Cette caractéristique peut limiter les fonctionnalités offertes vu que les composants doivent être d'une taille assez petite. Par exemple on ne peut pas utiliser un ventilateur pour le refroidissement des composants.

### **2.2.2 L'autonomie**

On dit qu'un système est autonome lorsqu'il dispose de toutes les ressources qui assurent son fonctionnement. Il s'agit de ressources matérielles (processeur, mémoire, etc), de ressources logicielles (OS, applications) et de ressources d'énergie qui peuvent être continues ou rechargeables à travers des accumulateurs d'énergie pour pouvoir fonctionner [Fré00, Jal09].

Un grand nombre de systèmes sur puce actuels sont mobiles et fonctionnent avec des ressources d'énergie limitées, il est donc extrêmement important de réduire au

maximum leur consommation afin d'augmenter leur durée de vie.

### **2.2.3 Le temps réel**

La plupart des systèmes sur puce actuels communiquent avec leur environnement externe afin de recevoir les données à traiter ou d'envoyer des consignes suite à un traitement effectué. Dans certains cas, la validité d'un résultat dépend de l'instant de son arrivée (échéance). Ce type de système est appelé système temps réel [Aud 04, Bru06].

On distingue le temps réel dur qui correspond à un résultat catastrophique lors du non respect des échéances comme dans le cas des systèmes de transport. On parle de temps réel mou si le non respect des échéances s'accompagne par une dégradation de la qualité du service fourni par le système. Par exemple un GSM fait un retard à chaque décodage de trame le système devient inexploitable et les paroles des utilisateurs ne peuvent pas être synchrones.

Deux techniques peuvent être distinguées [Fré00]: le développement monolithique et l'utilisation d'un système d'exploitation temps réel. Le développement monolithique est fait dans un langage de bas niveau. Il consiste à écrire un seul programme dans le système qui aura la totalité de la charge de travail du système. Les contraintes temporelles sont prises en compte lors de l'écriture du programme. L'utilisation des systèmes d'exploitation temps réel vient pour combler les défauts de la première technique. Elle permet l'exécution de plusieurs applications dans le système et elle offre les mécanismes nécessaires pour garantir le respect des contraintes du système. Cette deuxième méthode souffre aussi de quelques limites car la plupart des RTOS existants sont spécifiques et avec un code source fermé et non extensible.

### **2.2.4 Qualité de service**

Les systèmes embarqués évoluent généralement dans des conditions environnementales imprévisibles et souvent non maitrisables vu qu'ils sont portables. La plupart d'entre eux sont incorporés dans des systèmes mobiles. Ils sont donc, soumis à des variations et à d'autres contraintes environnementales qui peuvent causer des défaillances : radiation, vibration, corrosion, chocs, variation d'alimentation, interférences radio fréquence, humidité, température etc. Il est donc nécessaire de prendre en compte l'impact de la variation des conditions environnementales lors de la conception de ces systèmes.

Les systèmes embarqués sont de plus en plus sophistiqués et utilisés dans des domaines assez critiques dans lesquels un disfonctionnement peut causer des nuisances, des pertes économiques et voir même des catastrophes sur la vie de l'être humain et l'environnement notamment dans le domaine médical, ou le nucléaire ou le domaine de transport.

Généralement, les utilisateurs des systèmes embarqués sont très exigeants en termes de fiabilité, de robustesse et de QoS. La plupart des utilisateurs acceptent un temps de disfonctionnement de l'ordinateur par exemple pour quelques heures à cause d'une panne ou de coupure de tension électrique. Par contre, ils sont généralement beaucoup moins patients vis-à-vis du disfonctionnement des systèmes incorporés sous forme de système embarqué et surtout dans le domaine de télécommunication par exemple.

### **2.2.5 Complexité**

Grâce à l'augmentation du taux d'intégration, les systèmes embarqués peuvent avoir des architectures matérielles trop complexes suivant les besoins de l'application. Un système embarqué peut contenir un processeur, de la mémoire et d'autres composants pour assurer les performances exigées par les applications. Il peut contenir plus qu'un processeur dans une seule puce voire des dizaines de processeurs. Toutes ces évolutions ont poussé les concepteurs à mettre en place des outils de conception plus sophistiqués pour pouvoir mettre en place ce type d'architecture assez complexe.

## **3 Conception de système embarqué**

La conception des systèmes embarqués nécessite généralement une très grande quantité de travail manuel et une grande expertise pour choisir l'architecture adéquate, écrire les modules de gestion de périphériques, concevoir les interfaces de communication et/ou configurer les systèmes d'exploitation commerciaux. A ce stade, le concepteur se trouve face à la tâche la plus difficile qui consiste à faire fonctionner l'ensemble de ces éléments qui sont conçus sur mesure pour répondre aux exigences d'une application.

Afin de réduire l'effort de conception et les risques d'erreurs de conception, une des techniques adoptées est l'utilisation des composants prédéfinis (IP). L'organisation VSIA (VSI Alliance) a proposé une méthodologie basée sur l'assemblage d'IPs préconçus [Seo10]. Malgré les inconvénients de ce type d'approche un grand nombre de méthodologies adopte ce concept en utilisant des IP et des interfaces de communication

standard de HW et de SW standard et paramétrables. Les pénalités de performances de cette solution architecturale sont acceptables et ce afin de répondre à une autre contrainte plus importante qui est bien évidemment le temps de mise sur le marché TTM et le prix final du produit.

Dans le but d'accélérer le flot de conception des systèmes embarqués, plusieurs travaux ont été menés. Ces travaux se basent sur l'utilisation de nouveaux outils capables d'automatiser le processus de conception. Ces outils se concentrent sur l'automatisation du raffinement de la communication et la réutilisation de blocs préconçus avec la génération automatique des interfaces. Ces outils utilisent différents flots de conception. On se contente ici de présenter le flot traditionnel.

Le flot de conception traditionnel est généralement constitué de trois étapes principales: (1) la spécification, (2) le partitionnement, et (3) la validation conjointe HW/SW.

### 3.1 Flot de conception Logiciel/Matériel

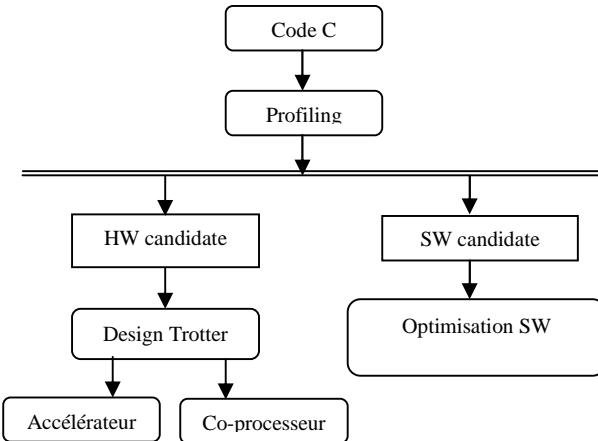

Le flot de conception SOPC traditionnelle est représenté par la Figure 1. Il admet comme entrée une spécification fonctionnelle de l'application et fournit en sortie une architecture adéquate qui répond aux différentes contraintes de l'application.

Figure 1: Flot de conception

Le flot de conception des SOPCs de la Figure 1 regroupe essentiellement trois étapes :

1. En partant d'une spécification fonctionnelle complète du design, le concepteur partitionne l'application en utilisant les outils adéquats ou manuellement en une partie logicielle et une autre matérielle. L'optimisation des techniques de partitionnement constitue un thème de recherche très sollicité par les scientifiques [Ara05, Cat01]. Ces activités de recherche s'intéressent surtout à l'automatisation de cette étape.

2. Une fois le partitionnement effectué, on implémente la partie matérielle en utilisant un langage de description matérielle telle que VHDL, VERILOG ou SystemC. La synthèse de la partie matérielle est réalisée par des outils de conception assistée par ordinateur (CAO) tels que Design Compiler de Synopsys [Syn], Allegro de Cadence [Cad] et Agility Compiler de Celoxica [Cel]. La partie logicielle en revanche, sera implantée en langage évolué par exemple C/C++. La compilation de la partie logicielle dépend du processeur cible. Ensuite, on passe à la synthèse de la communication des différents blocs du système. La plus part des systèmes sont conçus à base d'IP qui sont des composants matériels et logiciels déjà existants dans la bibliothèque d'IPs de l'environnement de conception il est donc nécessaire de mettre en place les mécanismes de communication entre eux. La synthèse des communications permet de raffiner les interfaces des sous-systèmes communicants. Ce raffinement se fait d'une manière interactive jusqu'à figer les mécanismes de communication (protocole, contrôleur, interface).

3. Dans la phase finale du flot, on injecte le SOPC sur une plateforme adaptée de type FPGA. Cette plateforme représente un environnement idéal pour l'implémentation des SOPC contenant un ou plusieurs processeurs qui supportent la partie logicielle, une surface de portes logiques (pour supporter la partie matérielle et les bus de communication), des blocs mémoires et des interfaces de communication.

Dans les paragraphes qui suivent, nous allons détailler les différentes étapes du flot de conception comme présentées dans la Figure 1.

### **3.1.1 Spécification haut niveau**

La spécification d'un système fixe les fonctions principales exigées par l'utilisateur. En spécifiant le système, le concepteur doit tenir compte des performances techniques (paramètres architecturales) et économiques (coût de fabrication) du système sur puce. L'objectif de l'étape de spécification est de fixer un modèle fonctionnel et de le tester tout en vérifiant les contraintes d'implémentation de l'application. La création d'un modèle fonctionnel s'intéresse à la

structuration ou l'organisation du comportement du système au cours du temps. La spécification de l'application dépend des paramètres imposés par la plateforme d'implémentation.

Divers types de modèles de spécification fonctionnelle existent dans la littérature tels que Statechart, les réseaux de pétri et UML (Unified Modeling Language). Ces modèles de spécification, restent inadaptés pour exprimer les contraintes non fonctionnelles de l'application telles que les performances temporelles (durée, latence et débit) et les ressources d'implémentation nécessaires (énergie, mémoire et surface d'implémentation). La vérification de l'intégrité fonctionnelle de l'application nécessite l'utilisation d'un langage de description de haut niveau associé à un noyau de simulation comme SystemC [Sys].

### **3.1.2 Partitionnement logiciel / matériel**

L'étape de partitionnement logiciel/matériel détermine les tâches qui vont être implémentées sur un ou plusieurs processeurs et les tâches de traitement effectuées par des accélérateurs matériels. Durant cette étape de partitionnement, le concepteur fixe également les interfaces entre la partie HW et SW [Ara05, Ana05].

L'étape de partitionnement automatique d'une spécification est un problème complexe (un problème NP-complet). Afin de décomposer ce problème, on peut subdiviser ce processus en trois parties principales :

- Une partie qui effectue l'allocation des différentes ressources matérielles et logicielles en fixant leurs types et nombres. Dans le cas d'un processus d'allocation statique, le concepteur dimensionne à un niveau d'abstraction très haut l'architecture globale de l'application embarquée. Le concepteur fixe ainsi la limite de performance du design qui dépend des composants déployés dans l'architecture.

- Une autre partie qui effectue le partitionnement spatial ou temporel en affectant les tâches qui constituent l'application sur la partie matérielle ou logicielle. Dans les architectures statiquement reconfigurables, cette partie se limite souvent à un problème de partitionnement spatial dans lequel on affecte les différentes tâches aux différents composants fonctionnels. Cependant, dans le cas des architectures reconfigurables dynamiquement, le partitionnement temporel est devenu une étape indispensable dans la conception du système.

- Une troisième partie qui effectue l'ordonnancement de l'exécution et de la reconfiguration des différentes tâches ainsi que la communication entre elles. A ce niveau, le concepteur doit explorer l'espace de solution afin de sélectionner une

architecture qui respecte les contraintes de traitement temps réel imposées.

### **3.1.3 Validation**

Une fois qu'un partitionnement satisfaisant a été trouvé et que l'architecture a été définie, l'étape de synthèse post-exploratoire permet de générer le système. Il y a ici deux étapes, d'une part la synthèse matérielle dont le but est de générer soit un « netlist » pour la création d'un ASIC soit le code à télécharger « bitstream » dans un composant programmable de type FPGA, et d'autre part la synthèse logicielle (compilation) dont le but est de générer le code qui sera exécuté par un ou plusieurs microprocesseurs du système.

Dans cette partie, nous avons présenté les étapes essentielles du flot de conception mixte typique. Le but des approches de conception existantes est de proposer des architectures le mieux adaptées au traitement requis afin d'optimiser la surface des architectures et leur temps de développement. Toutefois, avec l'apparition des systèmes embarqués, avec des ressources d'énergie limitées, la consommation est devenue une contrainte prioritaire qui doit être prise en compte dans la conception des systèmes multimédia. Ce sera l'objet du paragraphe suivant.

## **3.2 Gestion de la consommation**

La maîtrise de la consommation de puissance et d'énergie est un problème souvent rencontré dans le domaine des systèmes embarqués autonomes. Elle est devenue, ces dernières années, un facteur essentiel dans l'étape de conception. Ceci est dû au fait que les nouvelles applications deviennent de plus en plus complexes, et requièrent des architectures très complexes et par conséquent un nombre croissant de transistors sur la puce.

L'augmentation des puissances consommées rend l'amélioration de l'autonomie du système embarqué un objectif principal dès sa conception. Elle est aussi un facteur déterminant pour son succès commercial. Cet objectif peut être atteint par diverses techniques :

- Augmentation de la capacité de stockage d'énergie des piles : cet objectif est très difficile à atteindre et l'évolution dans ce domaine ne suit pas le progrès des besoins des systèmes actuels. Ceci a causé un « gap » entre l'évolution de la complexité des applications et l'évolution de la densité d'énergie des piles (exprimée en Wh/kg) comme le montre la Figure 2. En effet, la loi d'Eveready prévoit une lente évolution de la capacité des piles ne dépassant pas 40 %, évolution 4 fois moins élevée que celle de la capacité

d'intégration des circuits prédictes par la loi de Moore [Tur03]. Cette évolution ne permet plus de suivre la complexité croissante des applications prédictes par la loi de Shannon [Kar03].

- Diminution de la consommation du système embarqué. Diverses méthodes situées à différents niveaux d'abstraction peuvent être investiguées : au niveau algorithmique et au niveau architectural.

Comme il reste toujours difficile d'augmenter la capacité de stockage d'une batterie sans en augmenter le poids, le volume et le prix, il est donc nécessaire d'investir d'avantage dans la deuxième solution. Par conséquent, des méthodes de gestion d'énergie efficaces doivent être définies et incluses dans les différentes phases de conception des systèmes [Ben07].

Figure 2: "Gap" entre l'évolution des batteries et l'évolution des semi-conducteurs [Kan02]

### 3.3 Techniques de réduction de la consommation

Cette partie présente quelques techniques utilisées pour concevoir un système embarqué à faible consommation. Ces techniques peuvent être réparties en trois catégories : des techniques matérielles, d'autres logicielles et celles qui combinent les deux techniques précédentes, logicielles et matérielles.

Diverses techniques ont été proposées pour mettre en place un système à faible consommation. La plus répandue est celle qui conçoit des composants spécifiques qui consomment le moins possible. La seconde méthode consiste à fournir la partie logicielle qui consomme la faible quantité d'énergie et ce à travers des méthodes d'optimisation du code de l'application à exécuter. La dernière méthode consiste à combiner les deux techniques

précédentes c'est-à-dire, utiliser des composants qui consomment le moins et adapter le code de l'application suivant l'architecture utilisée.

### **3.3.1 Technique matérielle**

#### **3.3.1.1 Au niveau composant**

Actuellement, on assiste à une très forte évolution dans le domaine de fabrication des circuits électroniques. Ceci est dû à l'augmentation du taux d'intégration et de la fréquence de fonctionnement des circuits actuels. Ce qui implique une augmentation au niveau de la consommation du système.

Il est à noter que la consommation du système est la somme de deux types [Nab10] :

- la consommation statique qui est proportionnelle au nombre de transistors et au courant de fuite

- la consommation dynamique qui est proportionnelle à la fréquence de fonctionnement et la tension d'alimentation du système

Diverses techniques ont été proposées pour remédier à ce problème, telles que la diminution de la tension d'alimentation, l'activation séparée des blocs logiques et le contrôle du taux de basculement des bits.

- **Diminution de la tension d'alimentation**

La tension d'alimentation est un facteur qui a un impact très important sur la puissance dissipée par un circuit qui peut être calculé par la formule suivante:

$$P_{dyn} = \alpha \cdot C \cdot f \cdot V^2$$

Avec :

C : la capacité équivalente

F : la fréquence de fonctionnement

V : la tension d'alimentation

Ces dernières années, la tension d'alimentation des circuits intégrés n'a cessé de diminuer. Au début, cette valeur était fixée à 5v ; alors que, actuellement, la plupart des circuits travaillent avec une valeur de 3.3v ou 1.1v. Il est à noter qu'il y a des composants qui utilisent 0.5v et ceci est dû non seulement aux progrès de la conception des circuits intégrés mais aussi à la maîtrise des techniques de fabrication ; on parle maintenant de la technologie 45nm [Mat09].

- **Activation séparée de composants**

La deuxième technique proposée consiste à activer séparément les composants d'un circuit suivant les besoins de l'application [Koi06]. Cette technique n'est pas toujours réalisable et peut envisager des traitements supplémentaires pour l'activation des parties nécessaires au

bon moment. Cette technique a été utilisée pour diminuer la consommation de la mémoire cache. Elle consiste à diviser la mémoire en un ensemble de blocs qui peuvent être activés indépendamment les uns des autres.

- **Diminution du basculement des bits**

La troisième technique consiste à diminuer le nombre de basculements des bits entre 0 et 1, et ce, à travers la réutilisation des informations existantes sur le bus. Il est à noter que ce nombre intervient dans le facteur  $\alpha$  déjà cité pour le calcul de la puissance dissipée par un circuit.

### **3.3.1.2 Au niveau système**

La réduction de la consommation d'un système n'intervient pas seulement aux niveaux des composants mais aussi au niveau du choix de l'architecture du système complet [Jul04]. Parfois, là où la consommation du système coûte cher, on sera obligé à choisir des composants moins performants que d'autres et qui consomment bien entendu beaucoup moins d'énergie. Par exemple la plupart des systèmes actuels utilisent des supports de stockage de type mémoire flash bien que leur capacité de stockage soit beaucoup plus faible que celle d'un disque dur. Ce choix est notamment fait à cause de la faible consommation qui peut atteindre jusqu'à 90% de gain par rapport au disque dur [Lor98].

### **3.3.2 Technique logicielle**

Cette technique consiste à modifier le code susceptible d'être exécuté sur le système dans le but de diminuer la consommation induite à son exécution. Cette technique s'avère facile, mais en pratique, c'est très difficile de mettre en place des outils qui permettent l'automatisation de cette technique car elle demande une connaissance très précise de l'application ainsi que les spécificités de l'architecture du système [Mat07].

Cependant, des travaux d'optimisation du code de l'application peuvent avoir lieu manuellement pour minimiser la consommation du système ; le programmeur peut utiliser des langages de bas niveau tel que l'assembleur pour faire des instructions spécifiques d'une manière précise qui consomme moins. Une deuxième technique a été proposée ; elle consiste à remplacer l'appel des fonctions par des fonctions en lignes.

### **3.3.3 Technique mixte**

Cette technique est basée sur la collaboration entre les composants matériels et logiciels. Les mécanismes utilisés pour la réduction de la consommation proviennent aussi bien du matériel que du logiciel. Ce dernier prend en charge la prise de décision d'activation des mécanismes matériels nécessaires pour la réduction de la consommation [Chr11].

Ces techniques de réduction de la consommation sont très efficaces et permettent un gain très important au niveau d'énergie. Le problème avec ces techniques est que le concepteur se trouve parfois devant un compromis performance/consommation d'où la nécessité d'intégrer la gestion de la consommation dans le flot de conception afin de guider le concepteur dans son choix. Dans le paragraphe suivant nous présentons quelques approches classiques de codesign faible consommation.

### **3.4 Approches de codesign faible consommation**

Les méthodes de réduction de puissance et d'énergie sont plus efficaces, plus qu'elles sont adressées le plus tôt possible dans le processus de conception (globalement au niveau système). Cependant, la majorité des travaux existants sur l'optimisation de puissance adresse séparément les parties matérielles, logicielles et de communications après avoir fixé l'architecture du système. Seules quelques approches de codesign tiennent compte de la gestion de la consommation à un niveau d'abstraction plus élevé. Ces approches commencent en général par une étape d'estimation de la consommation des parties du système (tâches, fonctions, communications etc.) [Mou03a] pour déterminer ensuite, et le plutôt possible, la consommation totale du système. Parmi ces méthodes, on trouve:

1. Dave et Al. Ils ont présenté l'environnement COSYN-LP [Dav97], qui est l'extension de l'environnement COSYN pour faire l'optimisation de la consommation au niveau système. Leur méthode inclut une première étape d'estimation de la consommation et des temps d'exécution des tâches du système. Ensuite, un algorithme de type heuristique fait le partitionnement/ordonnancement des tâches du système sur l'architecture cible multiprocesseur. Cette approche permet de réduire la consommation dans le système jusqu'à 25%.

2. Fornaciari et Al dans [For98] présentent des métriques de consommation efficaces pour guider le partitionnement Hw/Sw au niveau système. Les métriques d'évaluation de la consommation ont été définies pour explorer largement l'espace de solutions au niveau élevé d'abstraction.

3. Dans [Jal09] les auteurs s'intéressent à l'exploration d'architecture basse consommation. Pour ceci ils ont proposé un flot de conception qui dispose d'une librairie d'IP modélisés en consommation à l'aide de paramètres de haut niveau. Par ailleurs des modèles

de performances riches et une technique d'exploration basse consommation est proposée. Cette approche permet de considérer un certain nombre de paramètres algorithmiques et architecturaux sur la consommation. Un modèle complet est proposé afin de déduire les performances globales du système qui seront utilisées lors de l'exploration à travers une technique basée sur le recuit simulé.

### **3.5 Limitations des approches présentées**

Le codesign faible consommation permet la création de systèmes à basse consommation en tenant compte des caractéristiques de l'application et de l'architecture cible. Cependant, ces approches ne tiennent pas compte d'un ensemble de paramètres « dynamiques » imprévisibles à l'avance et donc difficilement analysables hors ligne.

En effet, un certain nombre de paramètres peuvent modifier les performances d'un système multimédia embarqué pendant son exécution. Ils se situent à différents niveaux, certains étant aléatoires et non liés à une application cible :

- Le comportement de la batterie du système

- La variabilité des données et des applications

- Préférences de l'utilisateur

- Adéquation algorithme architecture

- Influence de l'environnement

#### **3.5.1 Le comportement de la batterie du système**

La plupart des systèmes multimédia mobiles opèrent avec des batteries. Leur évolution reste lente par rapport à la demande des nouvelles applications. Il est en effet toujours difficile d'augmenter la capacité de stockage d'une batterie sans en augmenter le poids, le volume et essentiellement le prix [Azz04]. Ceci a poussé les chercheurs à opter pour l'optimisation de l'utilisation de l'énergie de ces batteries puisque la durée de vie du système en dépend directement. Dans ce contexte, les travaux de [kan02] ont montré que l'augmentation de la durée de vie de la batterie du système n'est pas en liaison directe avec la réduction de la puissance moyenne consommée. En effet, le profil de courant instantané influe sur la capacité de la batterie. Ainsi l'exploration basse consommation est insuffisante pour augmenter la durée de vie du système. Il faudrait plutôt suivre en ligne l'évolution des ressources disponibles et agir en conséquence sur les éléments (architecture, application...) du système.

### **3.5.2 La variabilité des données et des applications**

Le progrès des systèmes informatiques mobiles et embarqués (téléphones mobiles et les PDAs) impose l'utilisation de plusieurs applications multimédia complexes [Ram05]. Ces applications, traitent un nombre variable de données, et la première source de variabilité de la performance de tels systèmes. En effet, la diversité des applications exécutées sur la même plateforme produit une variabilité au niveau de la charge de travail du système complet. La caractérisation de l'évolution instantanée de la charge de travail des différentes applications est une étape nécessaire pour estimer les performances d'exécution du système implanté sur la plateforme. Par ailleurs, la variabilité des performances de traitement associée à une application dépend largement de la nature du flux de données traitées [Rut02]. Une architecture embarquée qui implémente une application traitant des données multimédias, comme les applications de vision artificielle, d'imagerie 3D et de codage audio, représente un exemple significatif qui illustre cette variabilité temporelle. Dans le cas des applications multimédias, l'origine principale de cette variabilité de performance est l'instabilité au niveau des propriétés des données traitées (images ou séquence vidéo) [Var04].

### **3.5.3 Préférences de l'utilisateur**

L'utilisateur, maître de cet environnement, peut donner ses consignes au système, tels que la durée de vie souhaitée du système et le niveau de qualité de service acceptable pour le fonctionnement du système. Ces exigences peuvent être modifiées à n'importe quel moment. Par ailleurs, l'utilisateur peut privilégier l'exécution de certaines fonctionnalités de son système mobile au dépend d'autres qu'il peut désactiver ou dégrader leur qualité de service. Ceci engendre des changements de la consommation d'énergie et de l'allocation des charges de travail des différentes applications du système.

### **3.5.4 Choix architectural**

Une architecture système typique qui traite des données multimédias comporte des accélérateurs matériels spécifiques, un ou plusieurs composants programmables (processeurs, DSP ou contrôleurs) et de la mémoire [Sof07]. Une telle architecture permet d'améliorer les performances du système en termes de temps d'exécution et par conséquent en termes de qualité de service. Mais cette amélioration est pénalisée par l'augmentation de la consommation du système. D'une part, puisque ces composants ont des consommations dites statiques càd puisqu'ils consomment de l'énergie même s'ils ne sont pas en cours d'utilisation. D'autre part, il est évident qu'une tâche implantée en hardware s'exécute plus rapidement que celle en

software. Mais il faut tenir en compte qu'ils consomment aussi plus que la tâche software [Ben07]. Par conséquent, le concepteur se trouve devant plusieurs choix architecturaux qui peuvent être utiles pour le système dans un contexte de fonctionnement, mais lorsque les exigences du système changent au cours du fonctionnement l'utilisation de ces composants devient inutile compte tenu de leur influence sur la consommation du système.

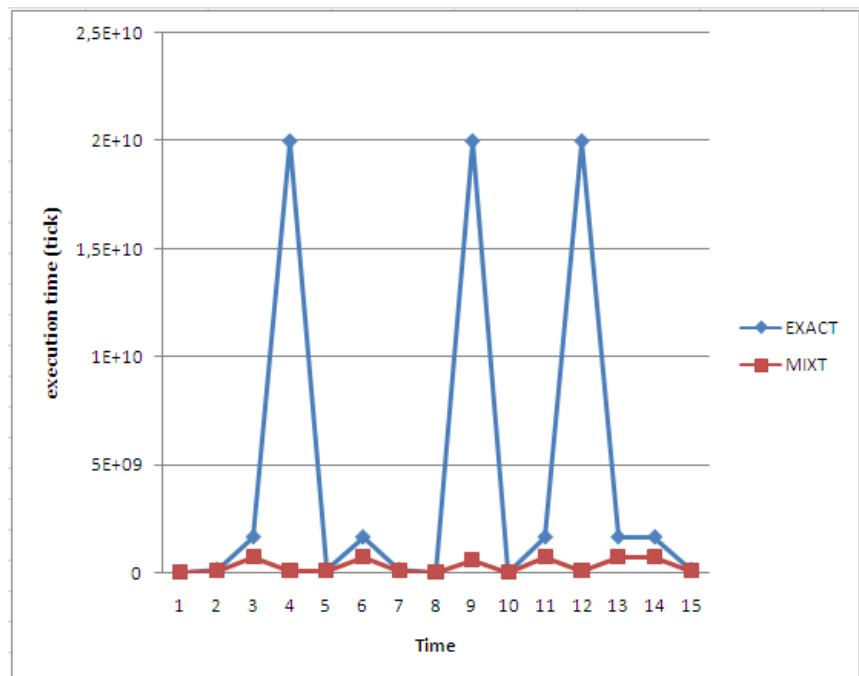

### **3.5.5 Influence de l'environnement**