République Tunisienne

Ministère de l'Enseignement Supérieur,

de la Recherche Scientifique

et de la Technologie

Université de Sfax

École Nationale d'Ingénieurs de Sfax

Cycle de Formation Doctorale

dans la Discipline Génie

Electrique

*Ingénierie des Systèmes

Informatiques*

**Thèse de DOCTORAT**

N° d'ordre: 2009– 96

# THESE

*Présentée à*

L'École Nationale d'Ingénieurs de Sfax

*En vue de l'obtention du*

## DOCTORAT

**Dans la discipline Génie Electrique

*Ingénierie des Systèmes Informatiques***

*Par*

**Jalel KTARI**

**(Ingénieur Génie Electrique)**

---

---

APPROCHE ET ENVIRONNEMENT D'EXPLORATION

ARCHITECTURALE BASSE CONSOMMATION

---

---

*Soutenu le 5 Mars 2009, devant le jury composé de :*

|    |                           |                           |

|----|---------------------------|---------------------------|

| M. | <b>Mohamed Adel ALIMI</b> | <i>Président</i>          |

| M. | <b>Slim BEN SAoud</b>     | <i>Rapporteur</i>         |

| M. | <b>Jean-Luc DEKEYSER</b>  | <i>Rapporteur</i>         |

| M. | <b>Nouri MASMOUDI</b>     | <i>Examinateur</i>        |

| M. | <b>Mohamed ABID</b>       | <i>Directeur de thèse</i> |

## **DEDICACE**

*À mon père & à ma mère*

*Auxquels*

*Je dois ce que je suis

Que dieu vous protége

Et vous prête une bonne santé*

*Et une vie heureuse*

*À toute ma famille*

*Pour les encouragements continus*

*À tous mes amis*

*À tous ceux que j'aime

Et qui m'aiment*

*À toi*

# REMERCIEMENTS

C'est avec un grand plaisir que je réserve ces lignes en signe de gratitude et de reconnaissance à tous ceux qui ont contribué de près ou de loin à l'élaboration de ce travail.

Je tiens à exprimer ma vive gratitude à mon directeur de thèse, Monsieur Mohamed ABID, Professeur à l'Ecole Nationale d'Ingénieurs de Sfax. Ses conseils et encouragements m'ont permis de surmonter toutes les difficultés du parcours. Qu'il trouve ici l'expression de mes sentiments sincères.

Mes remerciements s'adressent aussi à Monsieur Mohamed Adel ALIMI, Professeur et Directeur de l'Ecole Nationale d'Ingénieurs de Sfax pour l'intérêt qu'il a porté à ce travail en acceptant de me faire l'honneur de présider le jury de ma soutenance.

J'exprime ma reconnaissance à Monsieur Slim BEN SAOUD, Maître de Conférences à l'Institut National des Sciences Appliquées et de Technologie, ainsi qu'à Monsieur Jean-Luc DEKEYSER, Professeur à l'Université des Sciences et Technologies de Lille d'avoir accepté d'être rapporteurs de ma thèse.

Je remercie également Monsieur Nouri MASMOUDI, Professeur à l'Ecole Nationale d'Ingénieurs de Sfax, pour sa participation à mon jury.

Je remercie également Monsieur Mourid MARRAKCHI, Maître Assistant à l'Ecole Nationale d'Ingénieurs de Sfax, pour ses précieux conseils.

Par ailleurs, je remercie mon ami Dr. Issam MAALEJ qui m'a largement soutenu. Je lui suis très reconnaissant pour son aide, ses conseils et ses encouragements.

Je tiens également à remercier tous mes collègues et tous les membres de l'unité de recherche CES, à qui je souhaite une bonne continuation.

---

# SOMMAIRE

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>INTRODUCTION GENERALE .....</b>                               | <b>3</b>  |

| <b>CHAPITRE I. LA CONCEPTION FAIBLE CONSOMMATION .....</b>       | <b>6</b>  |

| I.1 INTRODUCTION.....                                            | 6         |

| I.2 LES EXIGENCES DES SYSTEMES EMBARQUES .....                   | 6         |

| I.3 SYSTEME FAIBLE CONSOMMATION .....                            | 7         |

| I.4 LA MAITRISE DE LA CONSOMMATION .....                         | 8         |

| I.5 LA REDUCTION DE LA CONSOMMATION .....                        | 8         |

| I.6 METHODOLOGIES DE REDUCTION DE LA CONSOMMATION.....           | 9         |

| I.7 TECHNIQUES ET OUTILS D'ESTIMATION .....                      | 11        |

| I.7.1 <i>Techniques</i> .....                                    | 11        |

| I.7.2 <i>Plate-forme SEQUENCE</i> .....                          | 16        |

| I.7.3 <i>SES Scanner</i> .....                                   | 22        |

| I.7.4 <i>ORINOCO</i> .....                                       | 24        |

| I.7.5 <i>EPRO</i> .....                                          | 26        |

| I.7.6 <i>DSP-PP</i> .....                                        | 29        |

| I.8 INTERPRETATION.....                                          | 30        |

| I.9 CONCLUSION .....                                             | 30        |

| <b>CHAPITRE II. EXPLORATION DE L'ESPACE DES SOLUTIONS.....</b>   | <b>32</b> |

| II.1 INTRODUCTION.....                                           | 32        |

| II.2 CONCEPTION MIXTE .....                                      | 33        |

| II.3 ÉLÉMENTS CARACTERISTIQUES DES FLOTS DE CODESIGN .....       | 34        |

| II.4 METHODOLOGIES ET OUTILS .....                               | 35        |

| II.4.1 <i>Introduction</i> .....                                 | 35        |

| II.4.2 <i>Outils de codesign</i> .....                           | 36        |

| II.4.3 <i>L'environnement MOVE</i> .....                         | 37        |

| II.4.4 <i>L'outil Codef-LP</i> .....                             | 38        |

| II.4.5 <i>L'outil Mogac</i> .....                                | 39        |

| II.4.6 <i>L'outil Cosyn-LP</i> .....                             | 40        |

| II.4.7 <i>Méthodologie de Ghali</i> .....                        | 41        |

| II.5 DISCUSSION.....                                             | 42        |

| II.6 CONCLUSION .....                                            | 43        |

| <b>CHAPITRE III. APPROCHE ET METHODOLOGIE D'EXPLORATION.....</b> | <b>45</b> |

| III.1 INTRODUCTION.....                                          | 45        |

| III.2 MODELES DE PERFORMANCES ET TECHNIQUE D'EXPLORATION .....   | 45        |

| III.2.1 <i>Modèle de graphe</i> .....                            | 45        |

| III.2.2 <i>Modèle d'architecture</i> .....                       | 46        |

| III.2.3 <i>Approche</i> .....                                    | 47        |

| III.2.4 <i>Modèles de performance temporelle</i> .....           | 49        |

| III.2.5 <i>Modèles de performance énergétique</i> .....          | 49        |

| III.2.6 <i>Modèle coût</i> .....                                 | 53        |

| III.2.7 <i>L'exploration basse consommation</i> .....            | 54        |

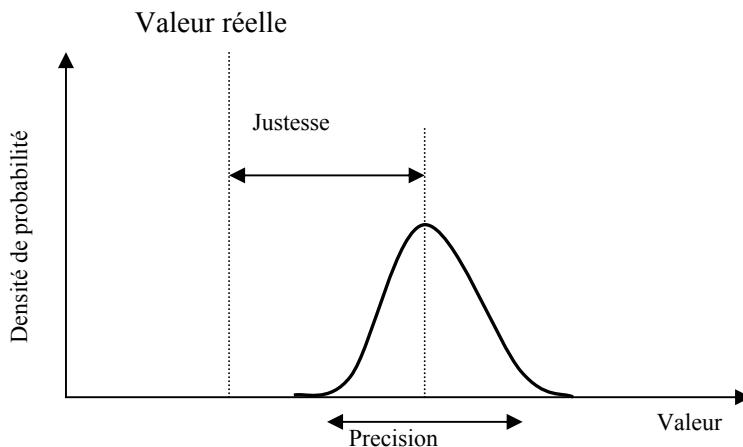

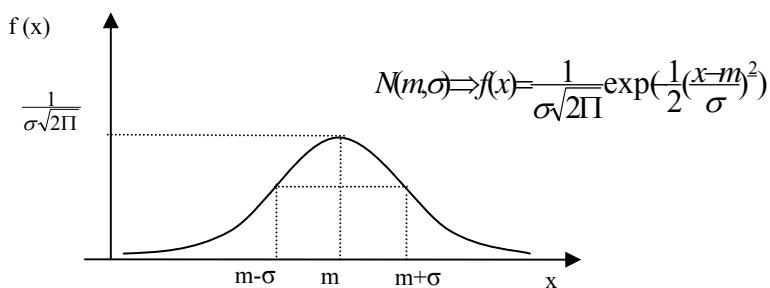

| III.2.8 <i>Méthodes d'estimation</i> .....                       | 54        |

| III.2.9 <i>Conclusion</i> .....                                  | 57        |

---

|                                                           |                                                             |           |

|-----------------------------------------------------------|-------------------------------------------------------------|-----------|

| III.3                                                     | OUTIL D'EXPLORATION .....                                   | 57        |

| III.3.1                                                   | <i>Stratégie d'exploration</i> .....                        | 59        |

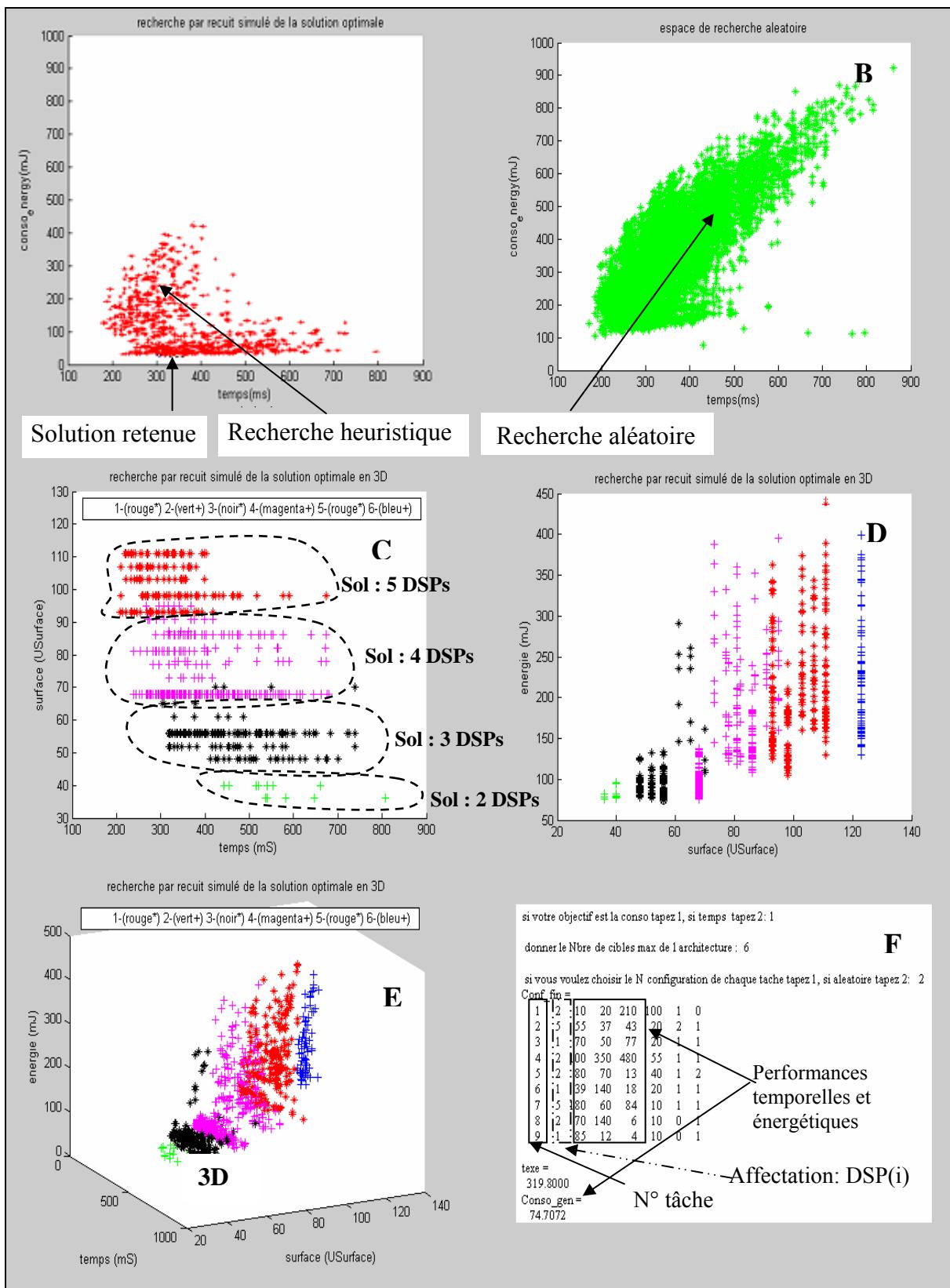

| III.3.2                                                   | <i>Résultats et analyse de l'espace d'exploration</i> ..... | 63        |

| III.4                                                     | CONCLUSION .....                                            | 67        |

| <b>CHAPITRE IV. EXPERIMENTATIONS ET ETUDE DE CAS.....</b> |                                                             | <b>69</b> |

| IV.1                                                      | INTRODUCTION.....                                           | 69        |

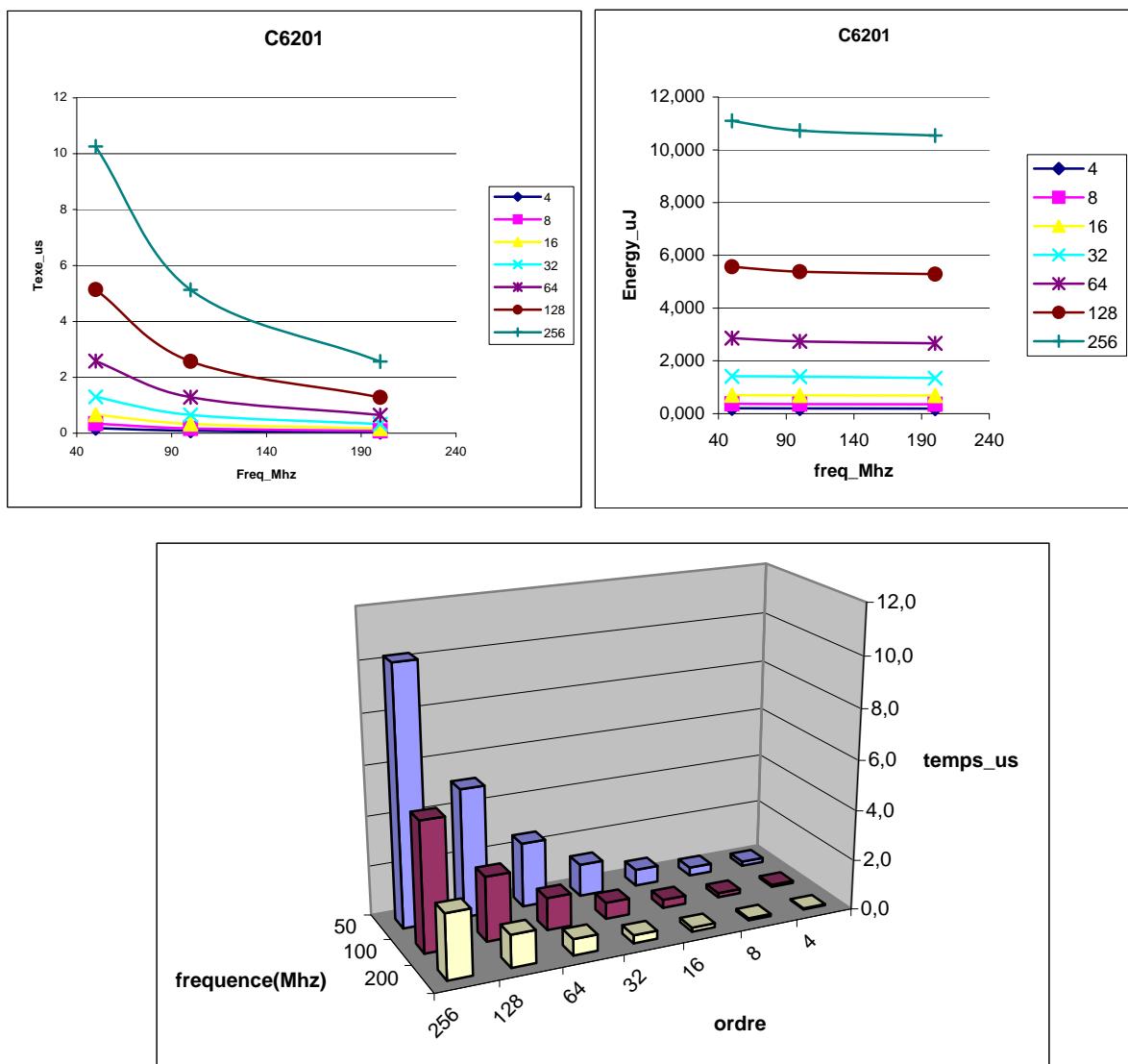

| IV.2                                                      | FILTRE A REPONSE IMPULSIONNELLE FINIE .....                 | 69        |

| IV.3                                                      | TRANSFORME DE FOURIER RAPIDE .....                          | 73        |

| IV.4                                                      | MPEG-2 .....                                                | 74        |

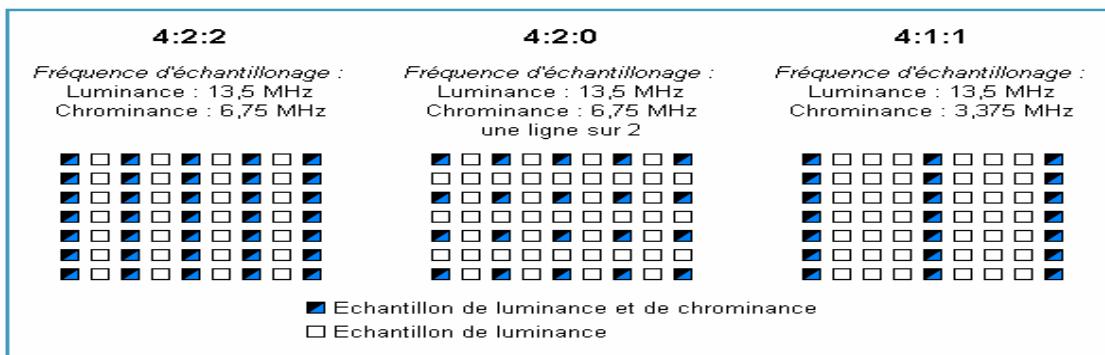

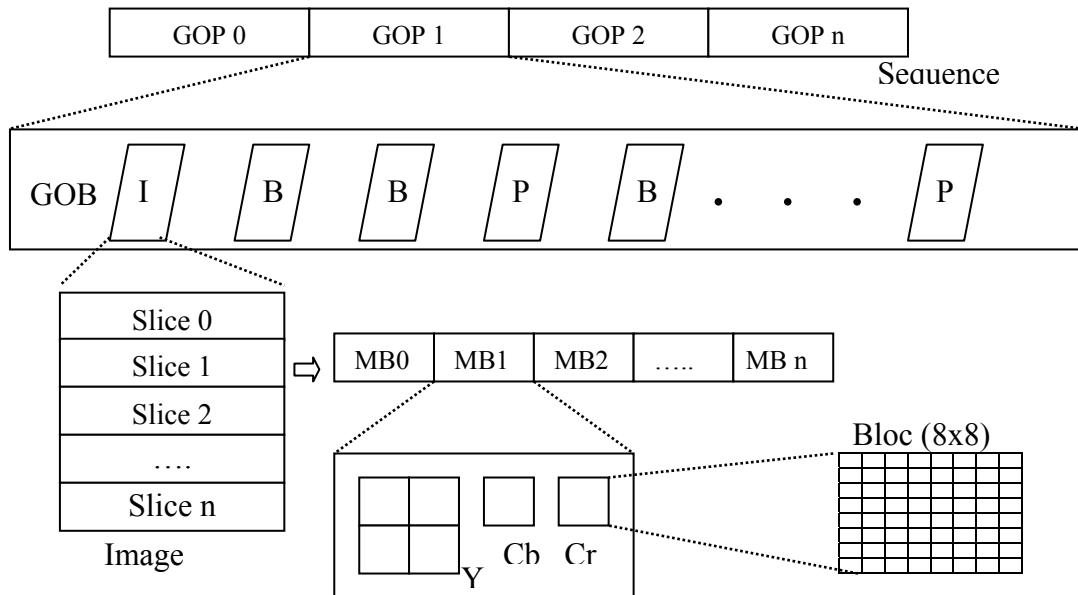

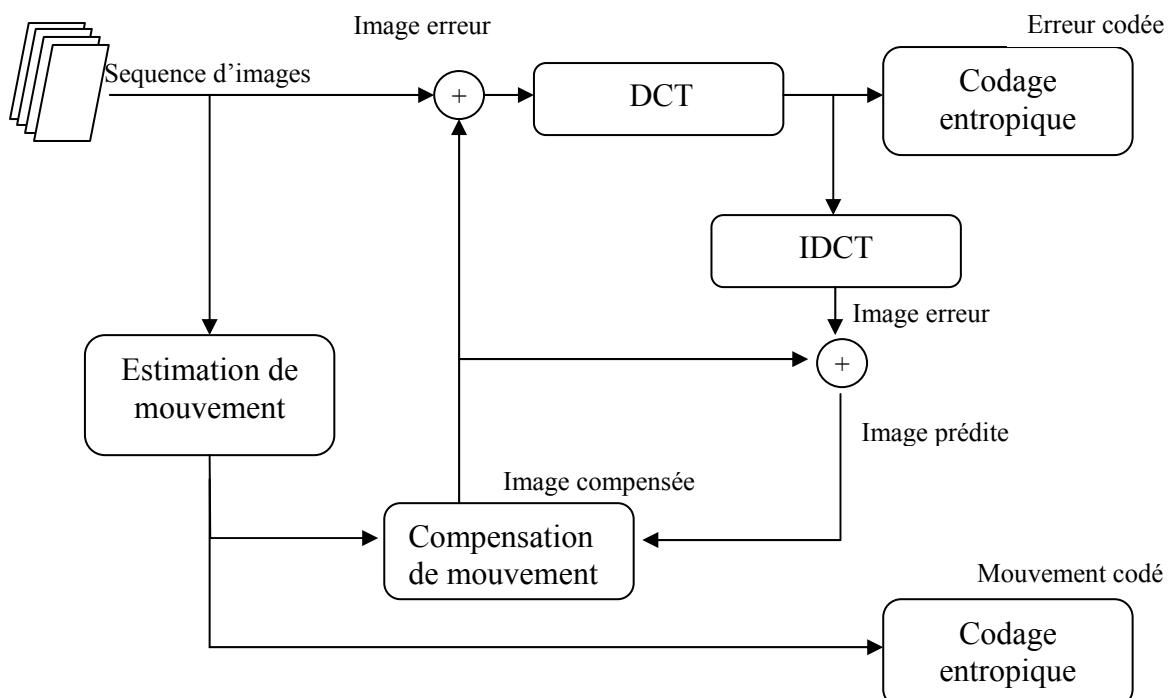

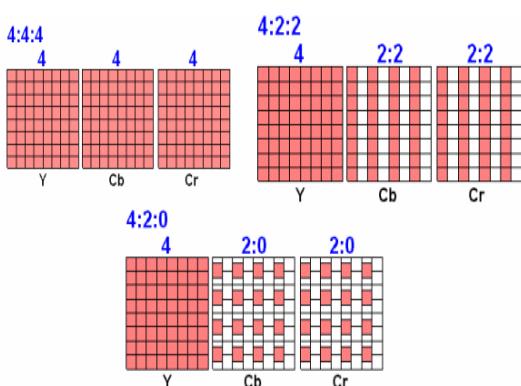

| IV.4.1                                                    | <i>Présentation et spécification</i> .....                  | 74        |

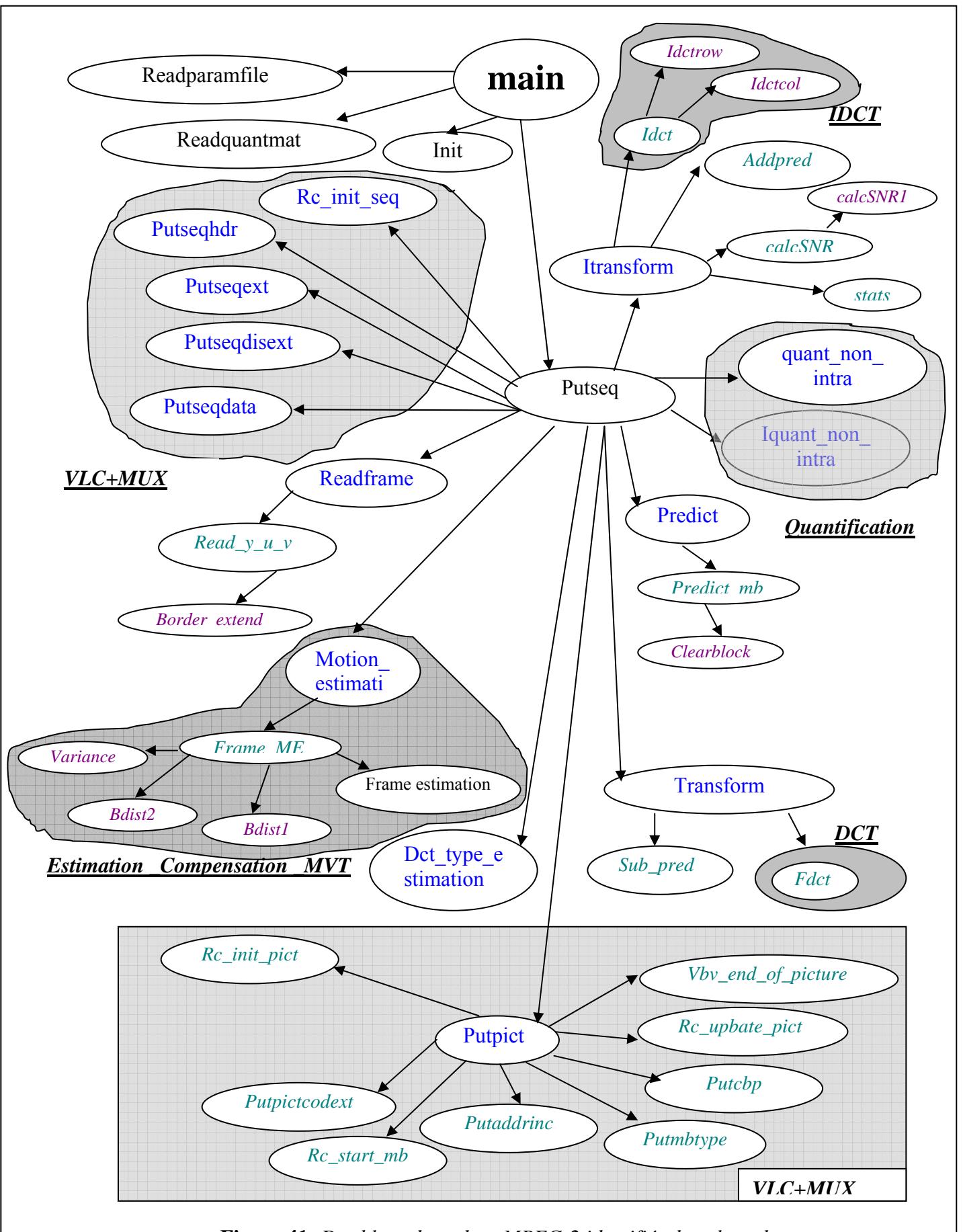

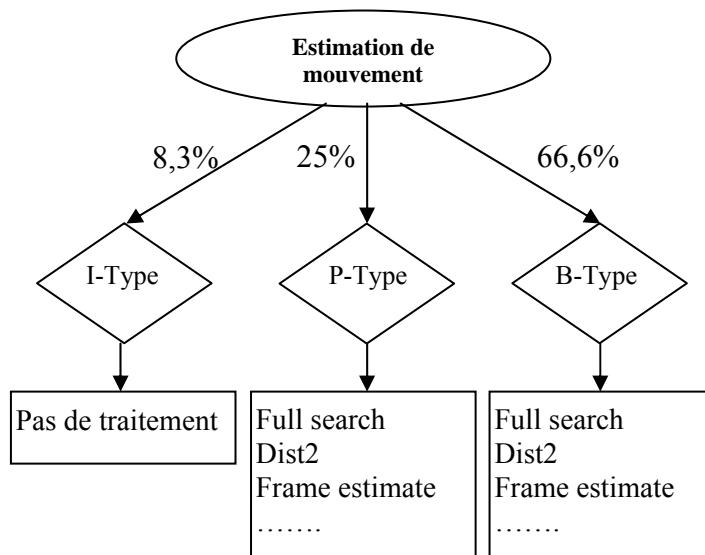

| IV.4.2                                                    | <i>Modélisation de l'application</i> .....                  | 77        |

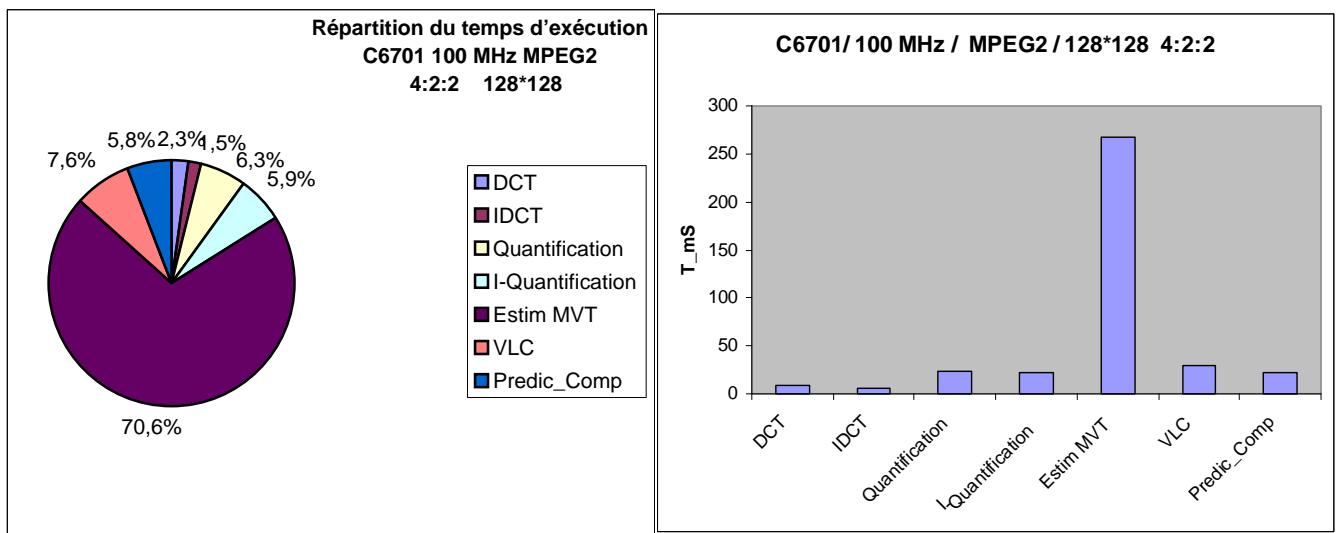

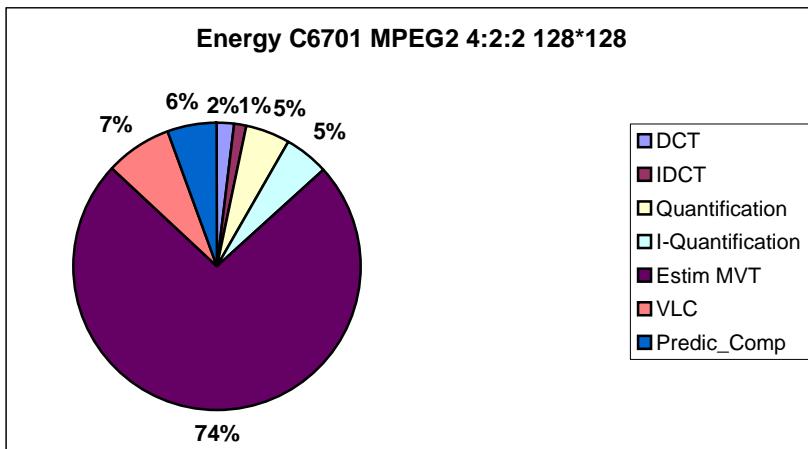

| IV.4.3                                                    | <i>Répartition du temps CPU et de la puissance</i> .....    | 84        |

| IV.4.4                                                    | <i>Modèle haut niveau MPEG2 (du pixel à l'image)</i> .....  | 85        |

| IV.4.5                                                    | <i>Du pixel au Standard</i> .....                           | 86        |

| IV.4.6                                                    | <i>Conclusion</i> .....                                     | 87        |

| IV.5                                                      | MPEG2-EXPLORATION DE L'ESPACE DES SOLUTIONS.....            | 87        |

| IV.6                                                      | FIABILITE DE L'APPROCHE.....                                | 88        |

| IV.7                                                      | CONCLUSION .....                                            | 91        |

| <b>CONCLUSIONS ET PERSPECTIVES .....</b>                  |                                                             | <b>93</b> |

| <b>REFERENCES .....</b>                                   |                                                             | <b>95</b> |

---

## **Introduction générale**

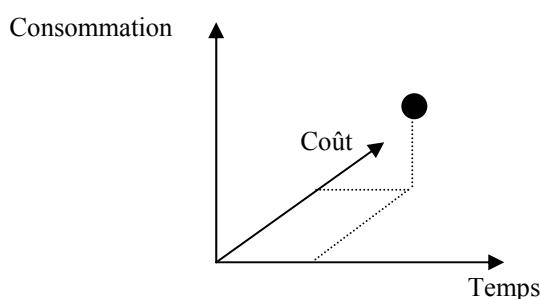

La complexité des systèmes embarqués est en pleine croissance afin de répondre aux exigences et aux critères de performances des nouvelles applications. Ceci rend la conception de plus en plus difficile en intégrant une multitude de fonctionnalités tout en respectant les contraintes de l'application. Par ailleurs, l'avènement des nouvelles technologies met en évidence la nécessité d'établir de nouvelles méthodologies de conception à un haut niveau d'abstraction. Ces méthodologies servent à mieux guider le concepteur lors du choix de la solution architecturale afin d'atteindre les objectifs souhaités entre autre la basse consommation.

En fait, la consommation de puissance et d'énergie est devenue une des contraintes principales lors de la conception des systèmes embarqués. En effet, les nouvelles applications nécessitent de plus en plus de puissance de calcul et de précision et par conséquent une augmentation de la consommation d'énergie et de puissance. Par ailleurs, vu le caractère de mobilité dans ces applications fonctionnant avec des batteries, la maîtrise de la consommation s'impose lors de la conception. Ceci permet d'une part d'augmenter la durée de vie des batteries qui se traduit par un gain en temps de communication d'un GSM par exemple, et de minimiser la dissipation thermique des composants qui influe sur la fiabilité du système d'autre part.

## **Objectif du sujet**

- Les nouvelles applications embarquées ont clairement montré l'évolution croissante de la consommation. Si la consommation n'est pas réduite et maîtrisée, la complexité ou bien la performance des applications devra être réduite afin d'envisager une solution embarquable. D'où une dégradation importante, voire inacceptable pour l'utilisateur, de la qualité de service (QoS) associée aux services fournis.

- On sait que les systèmes mobiles devront atteindre des performances élevées : 100 Mops/mW pour les nœuds mobiles et 10 à 50 Mops/mW pour les stations de base. Si de telles performances peuvent être atteintes par les ASIC, cela représente une efficacité 10 fois supérieure aux DSP actuels, 100 fois supérieure aux microprocesseurs généralistes. Pour garantir l'adaptabilité des systèmes à un environnement hétérogène, il faut donc prospecter de nouvelles solutions architecturales logicielles et matérielles garantissant une performance

---

élevée, une grande flexibilité et une faible énergie. Seule une approche globale de haut niveau permet de caractériser et d'optimiser efficacement la consommation (Benoit et al., 2004).

- L'étape d'exploration architecturale est une étape critique dans le flot de mise en œuvre du produit. En effet, pour une application donnée, il est possible d'avoir une multitude d'architectures. Cet espace contient des architectures qui sont non réalisables, d'autres qui ne satisfont pas les contraintes, d'autres qui les satisfont et des architectures qui ont des performances optimales. Il incombe à l'étape d'exploration de trouver pour l'application, une architecture adéquate qui satisfait les contraintes et qui optimise au mieux sa consommation.

## **Organisation et contribution de ce rapport**

Afin de maîtriser l'aspect faible consommation dans les systèmes embarqués, et afin de voir la possibilité de l'intégration de cet aspect dans l'exploration de l'espace des solutions à différents niveaux d'abstractions, une étude est faite sur les divers outils et méthodologies. De plus, une approche d'exploration basse consommation est proposée et validée.

Dans le premier chapitre du rapport, on présente les diverses techniques et méthodologies d'estimation de la consommation dans les systèmes embarqués à différents niveaux d'abstractions. Le deuxième chapitre est consacré à l'état de l'art de l'exploration de l'espace des solutions. On présente aussi les besoins, la nécessité et la complexité de l'exploration basse consommation lors de la conception.

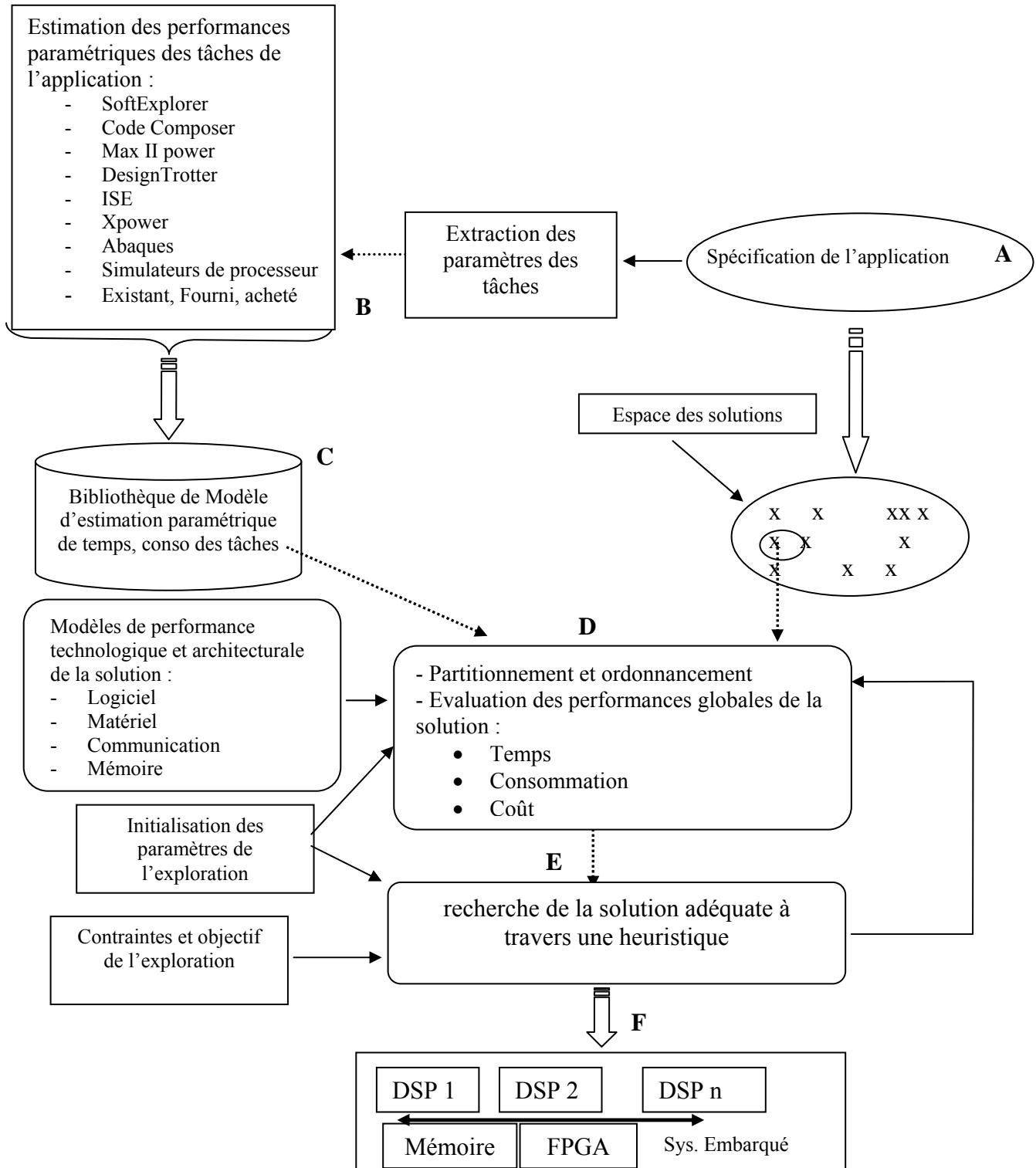

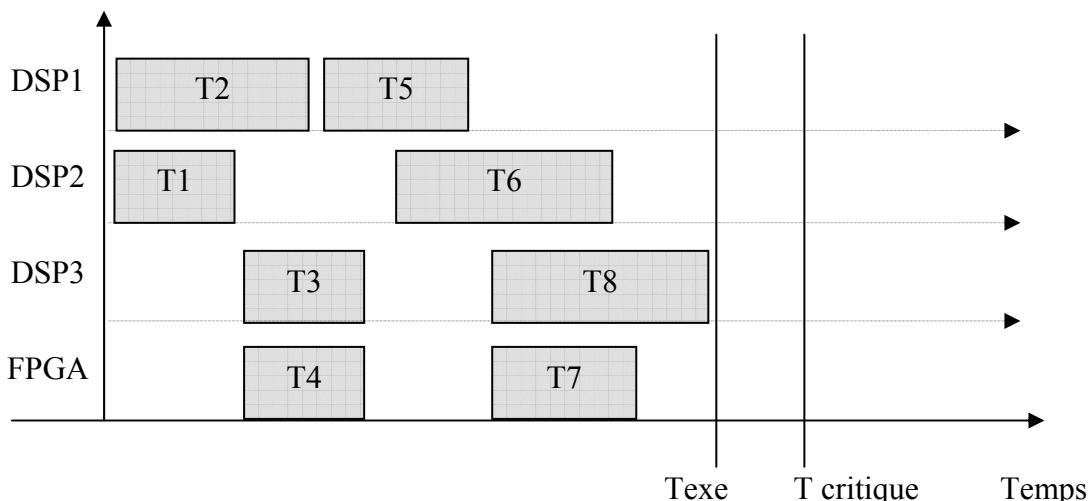

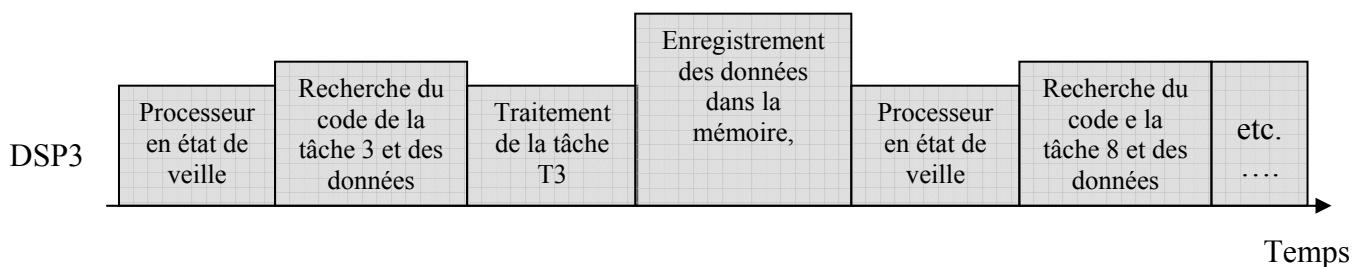

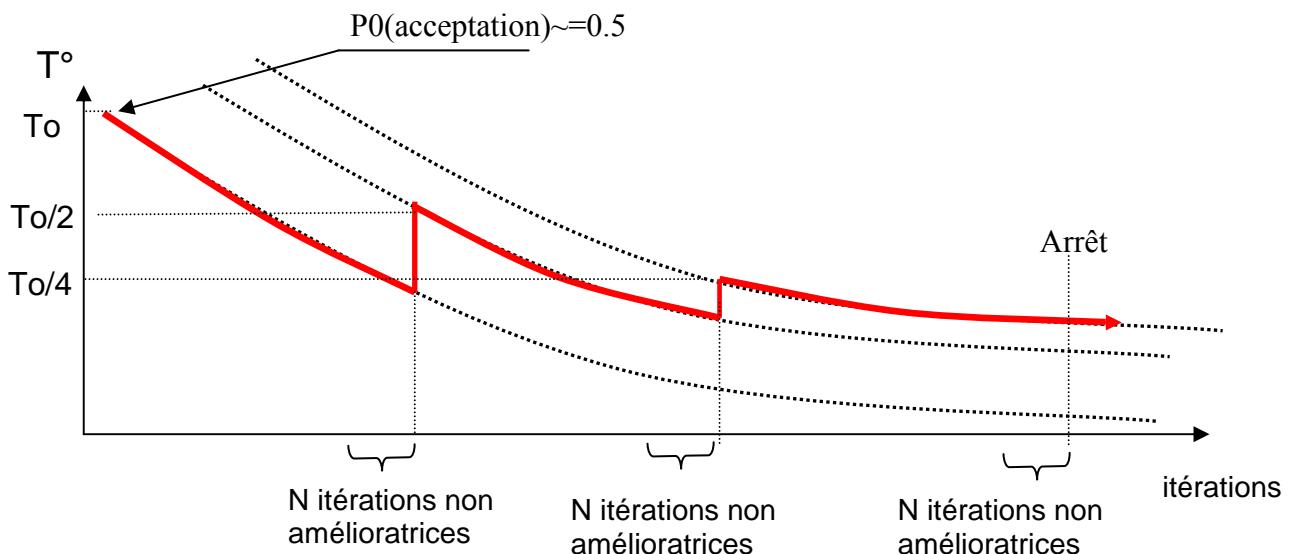

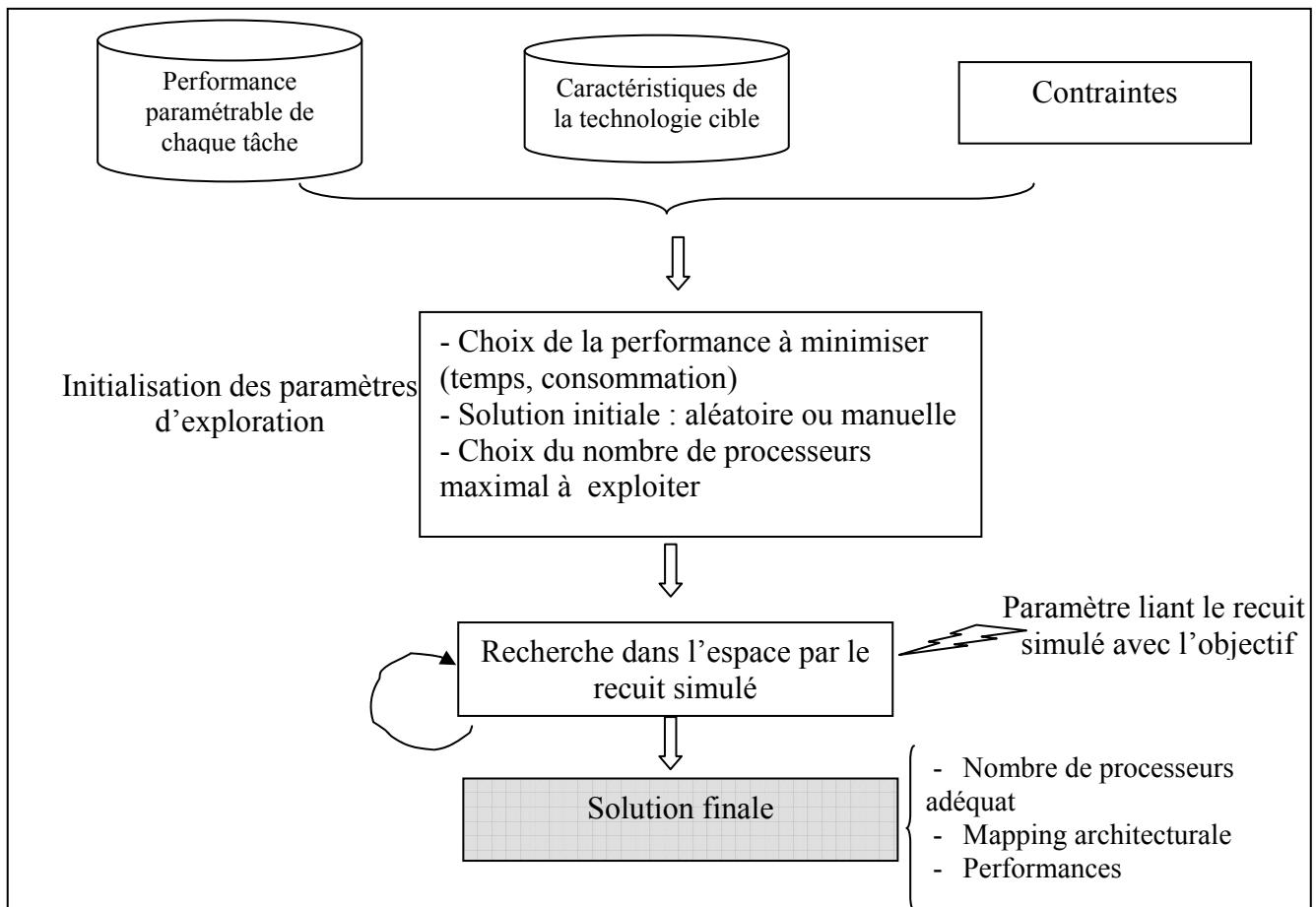

Dans le troisième chapitre du rapport, on présente notre approche pour faire face aux difficultés d'exploration et de conception basse consommation. Elle consiste à proposer des modèles de performances riches et une technique d'exploration dite basse consommation. Un modèle complet est proposé afin de déduire les performances globales du système qui seront utilisées lors de l'exploration à travers une technique basée sur le recuit simulé. Cette heuristique permet d'exploiter la technique d'exploration selon plusieurs niveaux de granularité et ce afin de pouvoir choisir le niveau qui permet d'assurer une exploration précise et rapide.

Le dernier chapitre est consacré à l'étude et la modélisation de haut niveau du filtre FIR, de la FFT et des différentes fonctions de l'application MPEG-2 sur diverses architectures cibles. Les modèles établis serviront comme bibliothèque de modèles utiles pour bien mener le choix stratégique de l'architecture cible adéquate lors de l'exploration basse consommation. Et afin de valider l'approche, une étude probabiliste est proposée.

---

*Chapitre*

**I**

# La conception faible consommation

(Techniques et Outils)

# Chapitre I. La conception faible consommation

## I.1 Introduction

Historiquement, les contraintes majeures lors de la conception des systèmes embarqués étaient essentiellement la performance et le coût. Avec la tendance vers les applications portatives et la forte densité d'intégration, l'énergie est devenue un facteur critique lors de la conception. En effet, la consommation est actuellement l'une des importantes métriques lors de la conception des systèmes embarqués. Il est à signaler que l'objectif essentiel de la conception faible consommation est non seulement minimiser la puissance, mais aussi augmenter la durée de vie des batteries et éviter les systèmes de refroidissement encombrants. Pour cela, plusieurs techniques et technologies sont développées et appliquées dans ce contexte. Ces différentes techniques seront présentées dans ce chapitre.

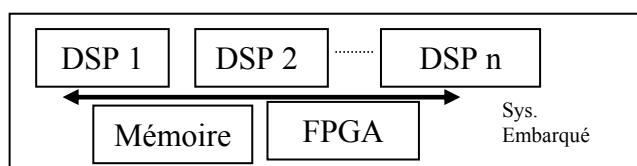

## I.2 Les exigences des systèmes embarqués

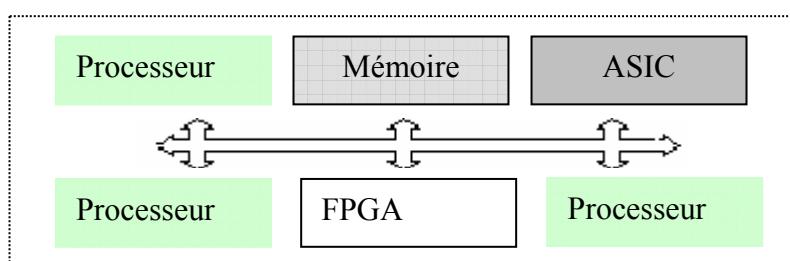

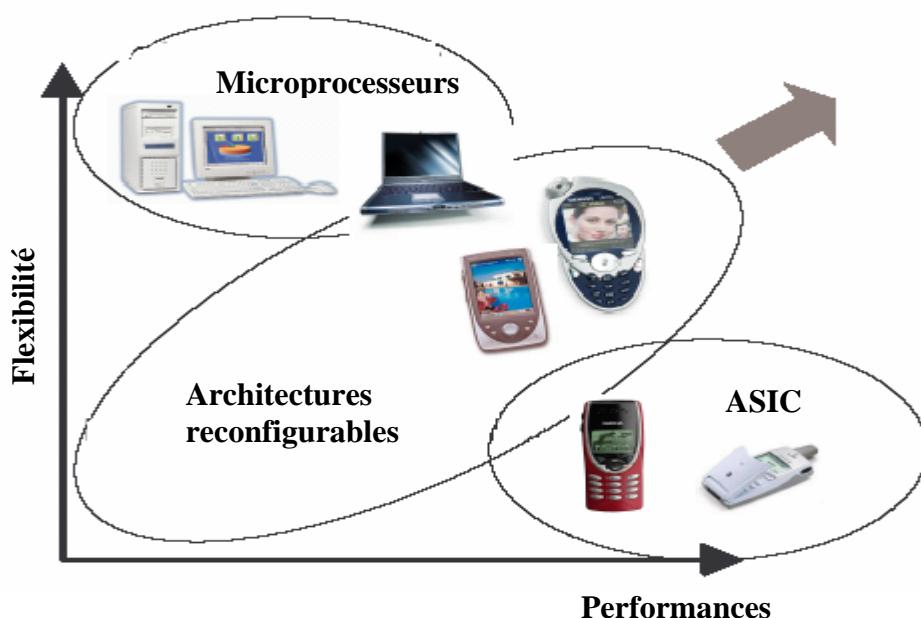

La conception logiciel/matériel de haut niveau permet de maîtriser la conception des systèmes complexes (Figure 1) et d'approuver leurs continuités. L'analyse des performances pendant une phase avancée de conception et avant la fabrication permet une exploration rapide de plusieurs alternatives d'architecture, ce qui offre au concepteur une meilleure visibilité et une grande réactivité vis-à-vis des changements technologiques (fiabilité, optimisation, flexibilité, migration etc.).

**Figure 1.** Architecture d'un système embarqué mixte (HW/SW)

Les prévisions pour l'évolution des applications de traitement de signal et d'image, pour les systèmes mobiles par exemple, montrent leur impact sur la conception des circuits et des systèmes embarqués. En particulier, à l'heure actuelle, il est indispensable de tenir compte de la consommation (en puissance et en énergie) comme critère de développement d'un système (Tableau 1) au même titre que la surface et la vitesse. En effet, la fréquence de

---

fonctionnement élevée, le nombre de ressources mises en œuvre et le degré d'intégration, contribuent à atteindre les limites physiques supportables par les circuits. La maîtrise de la consommation est donc un problème majeur dans la conception des systèmes embarqués.

On sait que si l'optimisation de la consommation doit intervenir à chaque niveau de la conception, c'est cependant aux plus hauts niveaux que les gains attendus sont les plus importants : 20 à 50% au niveau technologique contre 10 à 20x au niveau système (Rabaey et al., 1996) (Fei et al., 2003). Comme la partie logicielle représente au moins 70% du coût du développement des systèmes complexes et que la taille du code des applications TDSI double tous les deux ans, on conçoit qu'il est indispensable de disposer, au plus tôt dans la conception, de métriques de consommation fiables caractérisant aussi bien les parties logicielles et les parties matérielles (ITRS, 2004).

**Tableau 1.** *Les exigences fonctionnelles des systèmes PDA (ITRS, 2004)*

| Année                     | 2004                              | 2007                                                                                     | 2012                                                                    | 2015 |

|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|

| Technologie (nm)          | 90                                | 65                                                                                       | 45                                                                      | 32   |

| Voltage (V)               | 1.2                               | 0.8                                                                                      | 0.6                                                                     | 0.5  |

| Fréquence (MHz)           | 300                               | 600                                                                                      | 900                                                                     | 1200 |

| Application               | Traitement Image<br>Web<br>E-Mail | Vidéo temps réel Codec (MPEG4)<br><br>TV Téléphone<br>reconnaissance de voix<br>Cryptage | Interprétation temps réel<br><br>TV Téléphone<br>reconnaissance de voix |      |

| Performance (GOPS)        | 0.3                               | 2                                                                                        | 14                                                                      | 77   |

| Puissance (W)             | 0.1                               | 0.1                                                                                      | 0.1                                                                     | 0.1  |

| Puissance Standby (mW)    | 2                                 | 2                                                                                        | 2                                                                       | 2    |

| Capacité batterie (Wh/Kg) | 120                               | 200                                                                                      |                                                                         | 400  |

### I.3 Système faible consommation

Diverses méthodes existent afin d'obtenir un système à faible consommation :

- Modéliser le logiciel pour diminuer le coût énergétique de son exécution : optimisation du code des applications, étude du comportement des applications et des processeurs en fonction des paramètres du code.

- La seconde méthode consiste à concevoir de composants spécifiques pour consommer le minimum d'énergie. En fait, c'est avec l'explosion du marché des systèmes embarqués et l'apparition des problèmes de surchauffe des composants, que cet aspect a été

---

pris en compte au niveau de la conception. Comme techniques de limitation de consommation des composants, on cite la diminution de la tension d'alimentation, l'activation séparée des blocs logiques et le contrôle du taux d'activité des données.

- La troisième méthode consiste à réaliser une collaboration entre le logiciel et le matériel afin d'optimiser la consommation totale du système. Elle s'appuie sur des mécanismes matériels pour diminuer la consommation et utilise le logiciel pour une meilleure décision en activant ou non ces mécanismes. Cette méthode est décrite dans le cadre de la mise en veille des périphériques ainsi que sur l'adaptation dynamique de la vitesse du processeur, etc.

#### **I.4 La maîtrise de la consommation**

Les principales sources de dissipation de puissance dans un circuit numérique sont données dans l'équation suivante (équation 1).

La puissance statique  $P_s$  peut être, dans certains cas, négligée pour des circuits de type CMOS. Mais avec les taux d'intégration actuels et les nouvelles technologies, elle est loin d'être négligeable.

$$P_{moy} = P_d + P_{cc} + P_f = \alpha \cdot C \cdot V_{dd}^2 \cdot f + V_{dd} \cdot I_{cc} + V_{dd} \cdot I_f \quad (1)$$

où  $P_{moy}$  est la puissance moyenne dissipée par le circuit,  $P_d$  la puissance dynamique causée par la charge et la décharge de la capacité  $C$ .  $P_{cc}$  et  $P_f$  reflètent la puissance dissipée due aux courants de court-circuit et de fuite respectivement.

Avec  $V_{dd}$  la tension d'alimentation,  $f$  la fréquence d'horloge,  $C$  la capacité physique du circuit et  $\alpha$  le taux de commutation du circuit. Ces deux derniers paramètres sont souvent regroupés en un terme  $C_{eff}$ .

#### **I.5 La réduction de la consommation**

La consommation moyenne dans un circuit dépend de :

- La tension d'alimentation, son impact quadratique en ce qui concerne la consommation permet d'envisager un gain important. Il faudra cependant rester avec  $V_{dd} > 2 \cdot V_T$  (Rabaey et al., 1996) ou même plus actuellement. Et ceci pour éviter une augmentation importante du temps de propagation, qui est proportionnel à  $C_l \cdot V_{dd} / (V_{dd} - V_T)^2$ , ce qui cause un ralentissement du fonctionnement.

- La fréquence d'horloge peut être réduite en se basant sur des techniques d'optimisation du chemin critique logique (arbre de l'horloge) ou bien des méthodes

---

(parallélisme, pipeline) aux niveaux algorithmiques et architecturaux. De cette manière, on évite le fonctionnement à des fréquences plus élevées.

➤ L'activité du circuit qui se manifeste par le nombre de commutations au niveau des portes. Afin de réduire cette activité, il est utile de bien codifier les données de telle façon qu'on minimise les changements de niveau logique et éventuellement minimiser les commutations parasites.

➤ La capacité effective qui est un paramètre technologique : les connexions aux composants externes ont typiquement une capacité beaucoup plus élevée que les connexions aux ressources sur la puce. Donc pour économiser l'énergie, la minimisation de l'utilisation des accès externes et de la commutation est sollicitée. En fait, l'accès à la mémoire externe consomme beaucoup d'énergie. Ainsi, une façon de réduire la capacité est de réduire ces accès et d'optimiser le système en employant des ressources internes comme la mémoire cache et les registres.

## **I.6 Méthodologies de réduction de la consommation**

Il est possible d'utiliser des techniques de conception basse consommation à différentes étapes de la conception d'un système. La conception descendante consiste à partir du niveau le plus abstrait d'atteindre le niveau le plus bas. Pour ces systèmes, on distingue cinq niveaux différents: (Havinga et al., 2000) (Nikolaidis et al., 2005)

- Le niveau système

- Le niveau algorithmique

- Le niveau architectural (RTL: Register Transfert Level)

- Le niveau logique

- Le niveau électrique et physique

Par exemple, au niveau système : les modules inactifs peuvent être désactivés afin de minimiser les pertes énergétiques. Au niveau architectural, le parallélisme matériel peut être employé pour réduire les interconnections sans dégrader la sortie du système. Au niveau technologique, plusieurs optimisations peuvent être appliquées au niveau porte.

Les gains en consommation à chaque niveau de conception sont détaillés avec les outils dans le tableau 2: (Rabaey et al., 1996) (Laurent, 2002) (Beak et al., 2004) (Sequence, 2005) (Stanley et al., 2004) (Xilinx, 2006) (Minh et al., 2003) (Shin et al., 2002).

**Tableau 2 : Techniques et outils de réduction de la consommation**

| Niveau        | Domaine                                                                         | Outils                                                                                                                                                                | Intervention                                                                                                                  |

|---------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Système       | Processeur travaillant avec plusieurs fréquences                                | - <i>ORINOCO</i>                                                                                                                                                      | -Mises en veille<br>-Voltage scaling<br>-Partitionnement (hw/sw)<br>-Contrôle d'activité                                      |

| Algorithmique | -Sources de consommation mal maîtrisées<br>-Architecture peu connue             | - <i>GAUT_LP</i><br>- <i>Orinoco (Offis)</i><br>- <i>SoftExplorer</i><br>- <i>ePRO</i><br>- <i>SES</i>                                                                | -Réduire les accès mémoire<br>-Réduire les ruptures de pipeline<br>-Diminuer le taux de défaut de cache                       |

| RTL           | -Sources de consommation à peu près maîtrisées<br>-Implantation réelle inconnue | - <i>Design Powe (Synopsys)</i><br>- <i>Power Theater Sequence</i><br>- <i>GAUT_LP</i><br>- <i>Wattch, Simplepower</i><br>- <i>DSP-PP</i>                             | -Parallélisme/Pipeline<br>-Encodage de bus<br>-Eteindre les modules inutilisés                                                |

| Logique       | -Nature des signaux entrés influence fortement la consommation du circuit       | - <i>Cooltime</i><br>- <i>QuickPower (Mentor)</i><br>- <i>DesignPower(Synopsys)</i><br><i>PowerTheater(Sequence)</i><br>- <i>Accupower</i><br>- <i>Xpower(Xilinx)</i> | -Format de codage<br>-Extraction des sous-fonctions communes<br>-Partage de ressources<br>-Eliminer les transitions parasites |

| Physique      | Source de consommation clairement identifiée                                    | - <i>Coolpower</i><br>- <i>Spice</i><br>- <i>Accupower</i>                                                                                                            | -Transistor sizing<br>-Actions sur les seuils<br>-Actions sur Vdd                                                             |

Etant donné une spécification de conception, le concepteur a plusieurs choix sur les différents niveaux d'abstraction. Le designer doit choisir par exemple un algorithme particulier, concevoir ou exploiter une architecture qui peut être employée, et déterminer les divers paramètres influants comme la tension et fréquence d'horloge. Cet espace de conception multidimensionnel offre une grande gamme de compromis possibles. Et l'influence la plus remarquable sur la propriété de conception est obtenue aux plus hauts niveaux.

Donc les décisions de conception les plus efficaces dérivent du choix et de l'optimisation des architectures et des algorithmes aux niveaux les plus hauts. Plusieurs chercheurs (Havinga et al., 2000)(Garcia et al., 2005) ont montré que la conception au niveau architectural et système peut avoir un fort impact sur la consommation. Cependant en concevant au niveau système, le problème est de prévoir l'efficacité des décisions de conception. En fait, les détails d'implémentation peuvent être exactement estimés seulement au niveau technologique et pas aux niveaux d'abstraction plus hauts.

---

## I.7 Techniques et outils d'estimation

### I.7.1 Techniques

Diverses techniques d'estimation sont basées sur une méthode appelée Analyse de la Puissance au niveau Instructions (ILPA). L'ILPA a été développé à l'université de Princeton par Vivek Tiwari et al (Tiwari et al., 1996). Cette méthode était souvent considérée comme référence dans l'estimation de la consommation. Elle est applicable théoriquement à tous les processeurs que ce soit les processeurs généraux (Pentium, Athlon,...) ou les processeurs spécifiques (DSP).

Dans les systèmes basés sur microprocesseur, on peut modéliser la dissipation comme une fonction du logiciel (des instructions) étant exécutée sur une plate-forme matérielle. Les techniques d'évaluation de consommation du logiciel dans la littérature peuvent être triées dans ces catégories :

#### I.7.1.1 Analyse de la puissance au niveau instructions (ILPA)

Cette méthode est proposée afin d'évaluer la dissipation d'une partie du logiciel. L'idée de base est d'associer la puissance consommée avec l'exécution d'une instruction individuelle. La modélisation de cette méthode est décrite généralement par :

$$E = \sum_i (B_i * N_i) + \sum_{i,j} (O_{ij} * N_{ij}) + \sum_K S_k \quad (2)$$

Avec  $B_i$  l'énergie dissipée par l'instruction individuelle  $i$ ,  $O_{ij}$  reflète la puissance due au changement entre deux instructions consécutives ( $i,j$ ). En effet, il apparaît un surcoût dû au passage d'une instruction à l'autre c à d qu'un certain nombre de bits commutent du fait du changement du code de l'instruction (Brandolese et al., 2000). Le modèle doit donc tenir compte de cette consommation inter-instruction ce qui oblige à mesurer les consommations de toutes les combinaisons possibles deux à deux.  $S_k$  représente l'énergie due aux ruptures de pipeline et aux défauts de cache.

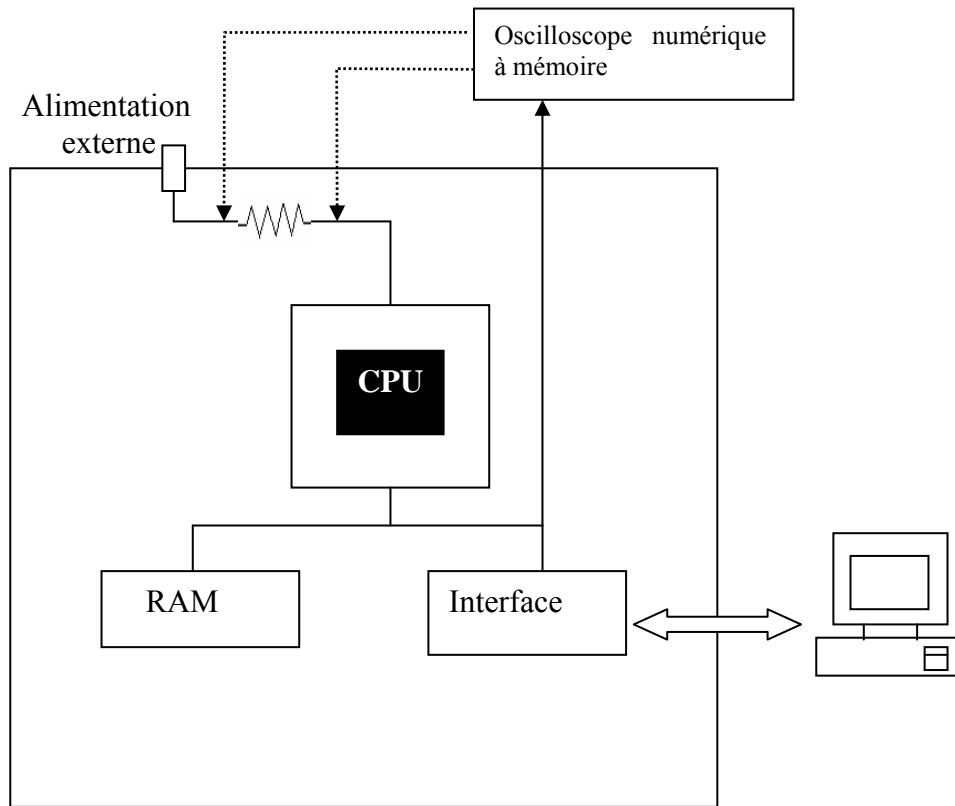

La figure 2 représente une plate forme utilisée afin de matérialiser cette méthode (Russell et al., 1998). Pour mesurer la puissance, une résistance de précision a été placée en série avec l'alimentation du processeur.

La consommation du processeur est calculée par cette formule (3) :

$$P(t) = I(t)V(t) = \frac{V_1(t) - V_2(t)}{R} * V_2(t) \quad (3)$$

Pour déterminer  $B_i$  et  $O_{ij}$  de l'équation 2 il faut faire un ensemble de tests des cas possibles. Mais ça engendre un nombre important de mesures  $\approx 110\ 000$  mesures pour un processeur Intel de 331 instructions (Li et al., 2003).

**Figure 2 : Plate forme expérimentale pour la mesure**

V. Tiwari dans (Tiwari et al., 1996) a fait l'expérience sur les processeurs commerciaux :

- Intel 486 DX2-S, 40 MHz, c'est un processeur CISC (Complex Instruction Set Computer) basé sur l'architecture du X86.

- FujiTsu SPARCLite MB86934, 20 MHz, c'est un processeur 32 bits, RISC (Reduced Instruction Set Computer)

L'expérience est faite par le procédé décrit au-dessus, le tableau 3 montre quelques résultats obtenus :

---

**Tableau 3 : Le coût des instructions de bases du 486 et '934**

| N° | Intel 486DX2 |              |        |             | FujiTsu SPARClite MB86934 |              |        |             |

|----|--------------|--------------|--------|-------------|---------------------------|--------------|--------|-------------|

|    | Instruction  | Courant (mA) | Cycles | Energie(nJ) | Instruction               | Courant (mA) | Cycles | Energie(nJ) |

| 1  | NOP          | 276          | 1      | 22.7        | NOP                       | 198          | 1      | 32.6        |

| 2  | Mov dx,bx    | 302          | 1      | 24.9        | St %io,[%IO]              | 346          | 2      | 114         |

| 3  | Jmp          | 373          | 3      | 92.3        | Ld [%IO],%io              | 213          | 1      | 35.1        |

| 4  | Add dx,bx    | 314          | 1      | 25.9        |                           |              |        |             |

Cette méthode est assez efficace et fiable pour les architectures ayant un jeu d'instructions limité. Par contre, pour les architectures VLIW (Very Long Instruction Word), le nombre de mesures à réaliser devient important [ $O(N^{2k})$ ] avec  $N$  le nombre d'instructions et  $k$  l'ordre du VLIW ]. Pour cela d'autres méthodes ont été développées afin de surmonter ce problème.

### I.7.1.2 Caractérisation par macro-modélisation

Au lieu d'évaluer la puissance au niveau instruction, le niveau fonctionnel logiciel, qui est une technique de macro-modélisation, traite les fonctions ou les sous-routines comme "des boîtes noires" et construit les macro-modèles qui corrèlent la puissance avec un jeu de caractéristiques. Telles caractéristiques de puissance peuvent être obtenues et rassemblées en employant une structure de simulation d'énergie à bas niveau (Li et al., 2003). La puissance dans ce cas est :

$$P = \sum_i W_i * C_i \quad (4)$$

Avec  $W_i$  sont les coefficients du macro-modèle à déterminer. Des méthodes mathématiques de régression sont mises en jeu afin d'identifier les  $W_i$  optimales, basées par l'application de paires d'entrée/sortie bien connues. Le problème-clé de cette macro-modélisation est comment choisir les  $C_i$  qui représentent une corrélation de la puissance avec ces boîtes noires, qui peuvent efficacement capturer les caractéristiques de puissance d'une sous-routine logicielle donnée dans des circonstances diverses.

---

### I.7.1.3 FLPA

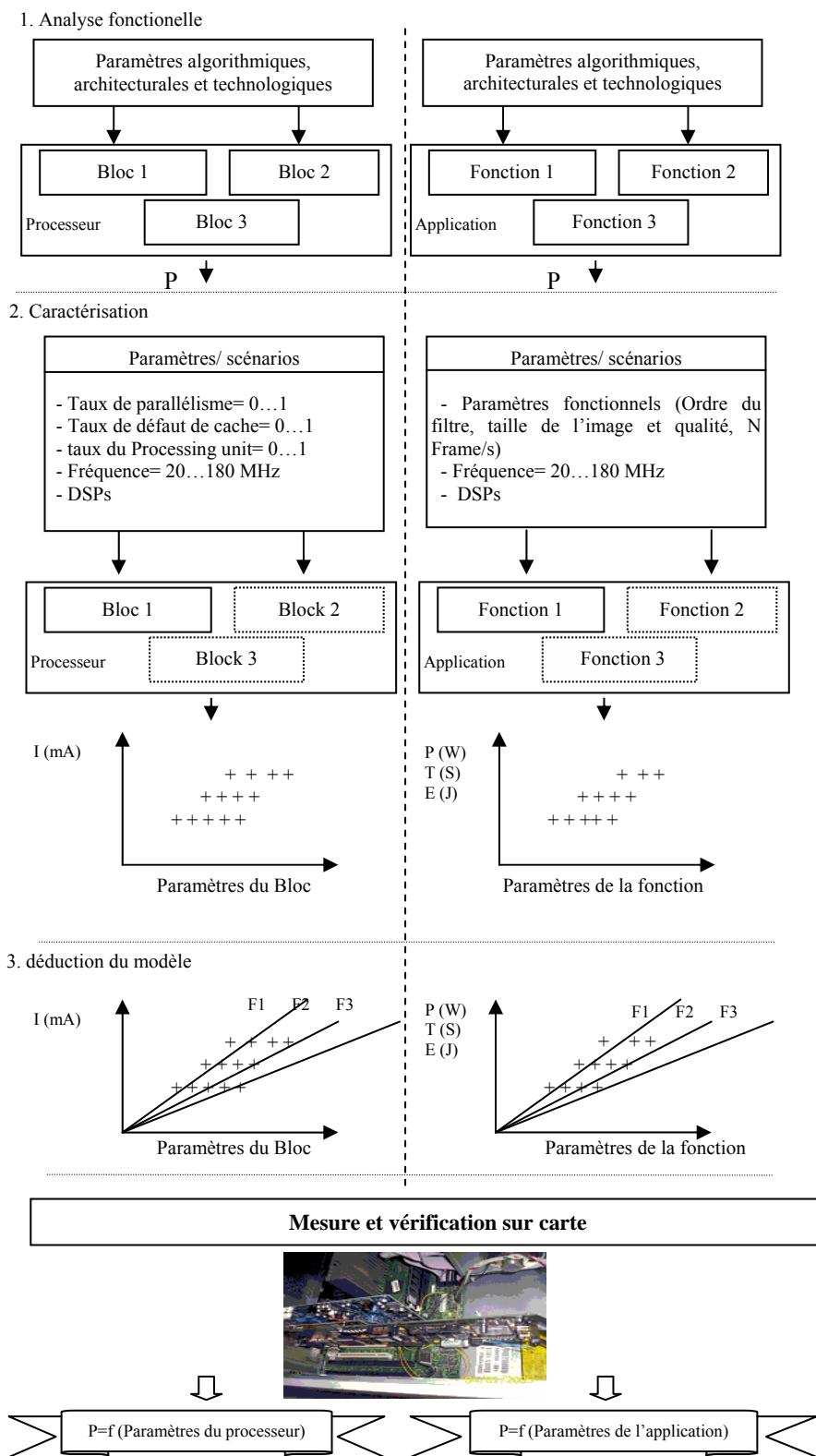

Les techniques d'estimation classiques ont souvent leurs limites. En effet, avec ces méthodes, la consommation due à la communication avec l'extérieur (accès à la mémoire externe, défaut de cache) n'est pas considérée. Par ailleurs, ces techniques sont assez complexes à exploiter pour les nouvelles architectures ayant un pipeline profond. Afin de surmonter ces problèmes, (Laurent et al., 2007) (Julien et al., 2004) a proposé une méthode permettant de réduire la complexité de l'estimation. Cette méthode est basée sur une analyse fonctionnelle de la cible du point de vue consommation (Functional Level Power Analysis : FLPA) ; elle est indépendante du niveau d'abstraction (assembleur ou C). Grâce à cette analyse, un nombre limité de mesures suffit pour déterminer le modèle de consommation de la cible. De plus, elle prend en compte toutes les fonctions du processeur que ce soit le contrôle du pipeline, les unités de traitement, les mémoires internes ainsi que les défauts de cache, ce qui n'est pas le cas avec les méthodes au niveau instruction.

#### I.7.1.3.1 Méthodologie

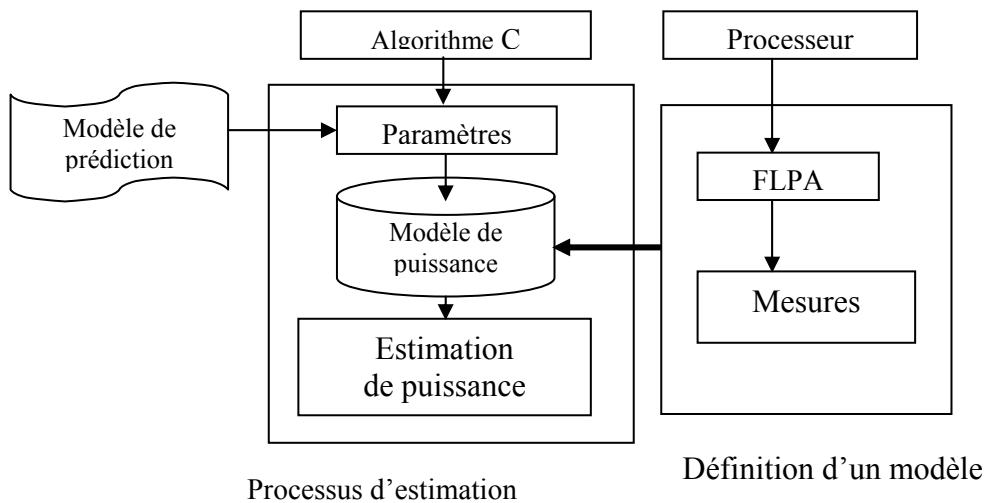

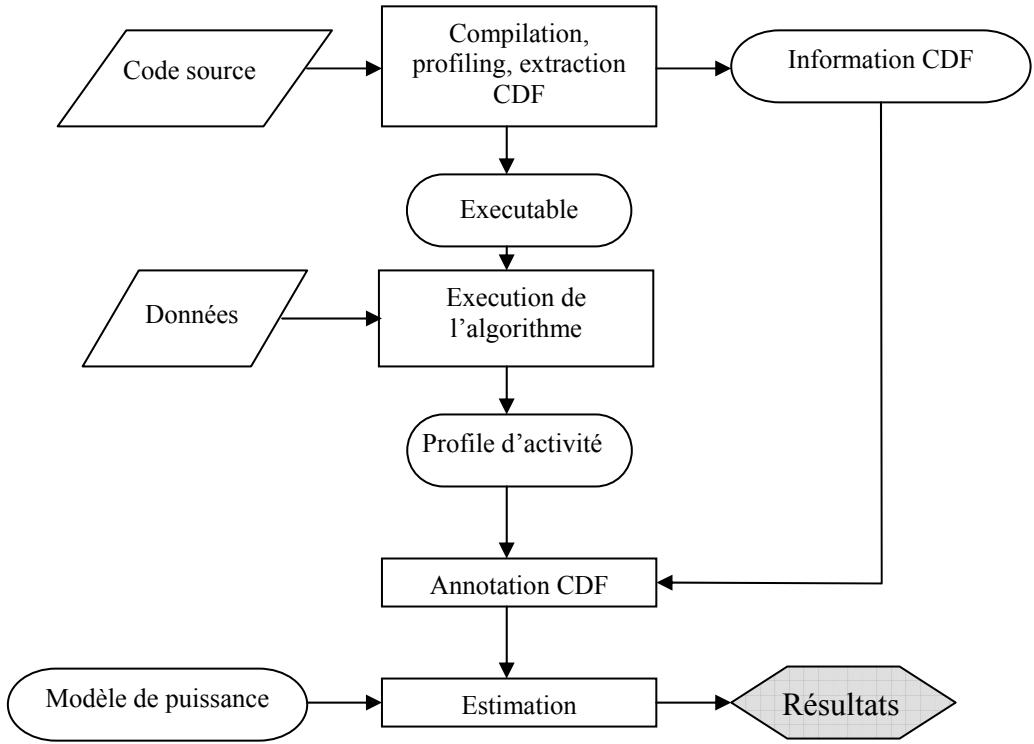

La méthodologie d'estimation de la consommation FLPA, illustrée par la figure 3, est constituée de deux parties : la définition du modèle et le processus d'estimation.

- La définition du modèle de puissance du processeur est réalisée une seule fois par cible. Elle est basée sur l'analyse fonctionnelle de l'architecture cible de point de vue consommation. Cette analyse permettra de déterminer un modèle de puissance basé sur des lois de consommation qui représentent le comportement en courant du cœur du DSP. Ces lois sont des fonctions mathématiques déterminées à partir d'un nombre réduit de mesures physiques réalisées sur la cible et dépendant de paramètres algorithmiques et de configuration. La FLPA permet de déterminer quels sont les paramètres pertinents de point de vue consommation pour un processeur donné. Par ailleurs, les paramètres algorithmiques sont des ratios (variant de 0 à 1) qui représentent le taux d'activité entre chaque bloc fonctionnel du DSP; par exemple, le taux de parallélisme, le taux de défaut de cache... Les paramètres de configuration sont définis par le concepteur.

- Le processus d'estimation est réalisé à chaque fois que la consommation d'un algorithme doit être déterminée. Au niveau C, les paramètres algorithmiques sont estimés en utilisant un modèle de prédiction. Il suffit ensuite d'utiliser les lois de consommation établies pour l'architecture cible pour connaître la consommation de l'application. (Laurent et al., 2002), (Ktari et al., 2005)

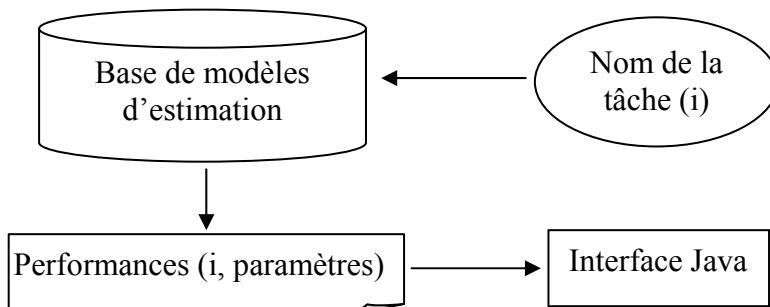

**Figure 3 : Méthodologie de l'estimation FLPA**

#### I.7.1.3.2 Outil : SoftExplorer

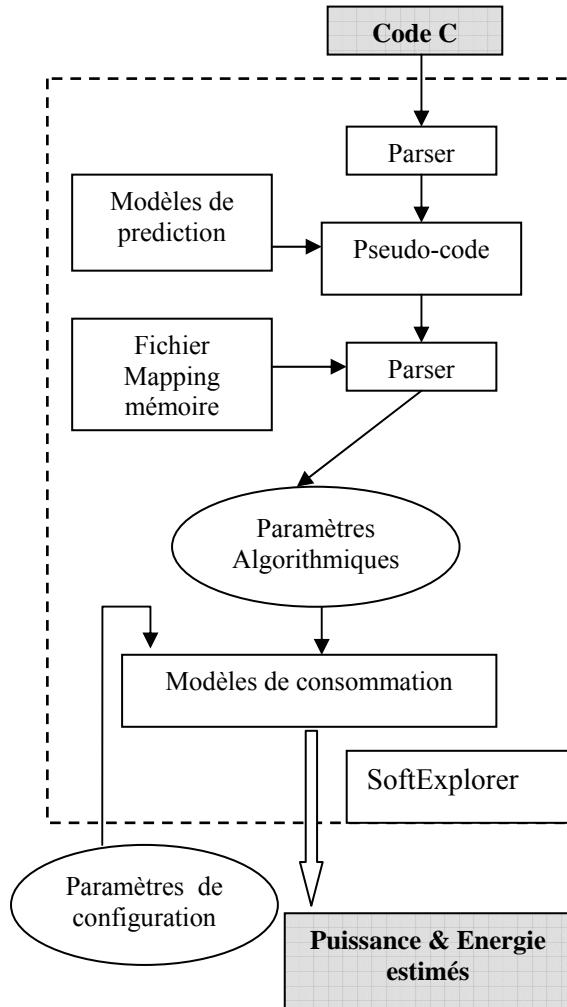

Cet outil (Laurent et al., 2007) automatique a comme entrée le code C ou ASM d'une application pour estimer sa consommation en terme de puissance et énergie. La structure de SoftExplorer est illustrée dans la figure 4. Il est basé sur trois modèles complémentaires :

- Le modèle du processeur : également appelé le modèle de puissance représente la manière dont la consommation du processeur change avec son activité.

- Le modèle de l'algorithme : représentant le lien entre l'algorithme et l'activité qu'il induit dans le processeur.

- Le modèle du compilateur : également appelé le modèle de prédiction qui représente le comportement du compilateur qui dépend des options choisies par le programmeur pendant la compilation, avec un fort impact sur le code généré, et ainsi sur l'activité du processeur.

**Figure 4 : Flot d'estimation avec SoftExplorer**

Cet outil disponible sera exploité dans ce travail (Ktari et al., 2007) lors de la modélisation des applications écrites en ANSI-C. Et ceci en parallèle avec les mesures réalisées sur cartes DSP.

### I.7.2 Plate-forme SEQUENCE

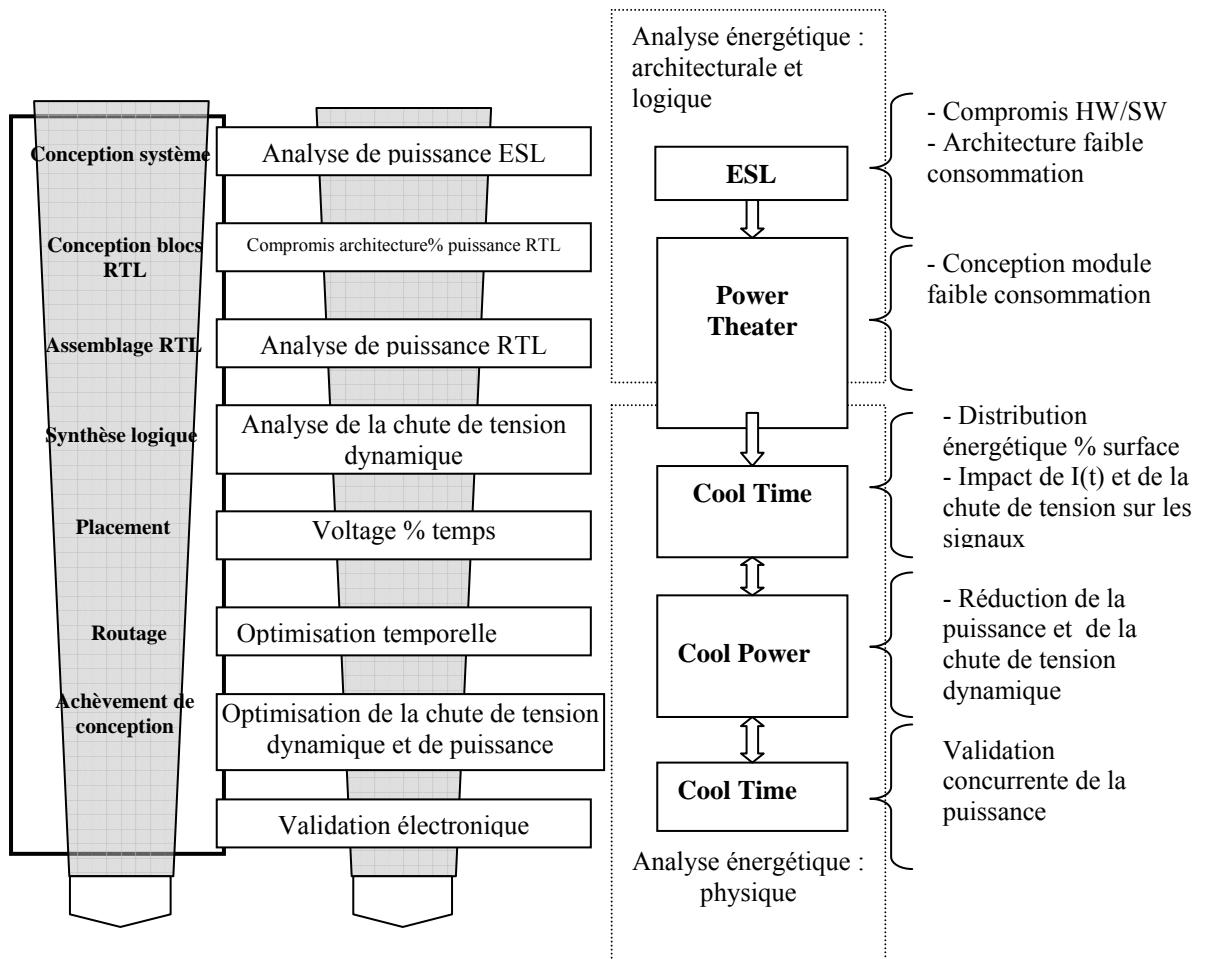

Sequence Design, Inc fournit un ensemble d'outils commerciaux complémentaires avec le flot de conception existant (Synopsys, Cadence). (Figure 5)

Cette plate-forme permet aux concepteurs des systèmes sur puce de réduire le coût du temps de mise sur le marché (*time to market*) en améliorant la performance et en limitant la consommation. En effet, elle permet de tenir compte de l'aspect faible consommation (analyse et optimisation de puissance) dans tous les niveaux d'abstractions du flot de conception. (Sequence, 2005)

**Figure 5 : Flot de conception Sequence design**

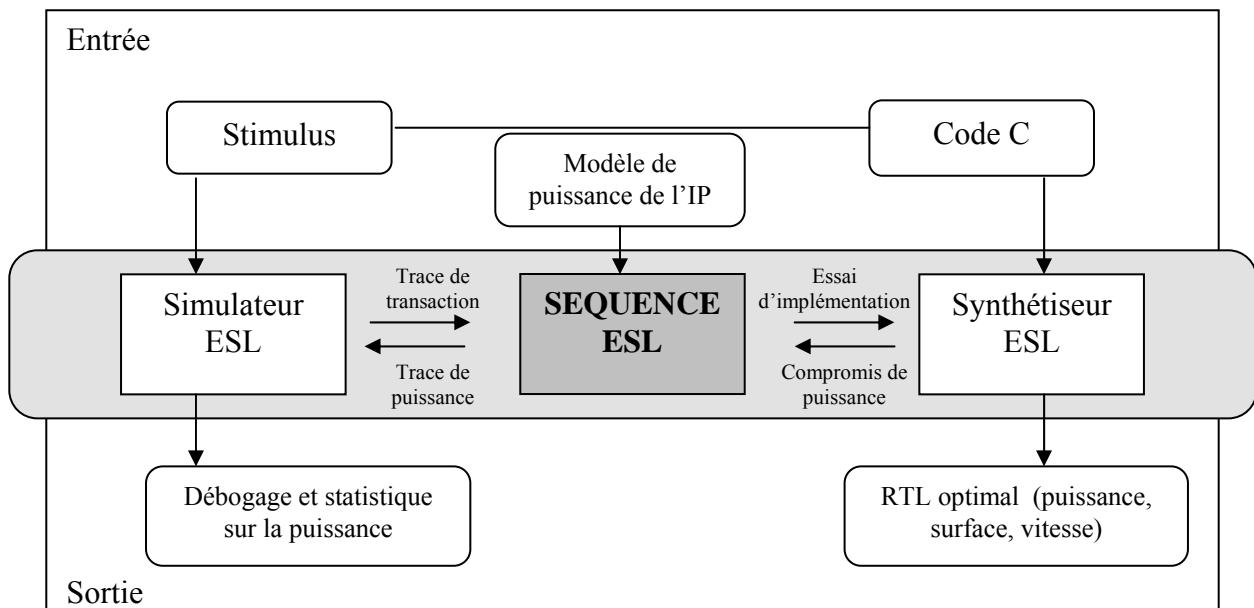

### I.7.2.1 ESL : (Electronic System Level)

#### I.7.2.1.1 Introduction

Le défi majeur lors de la conception des SoCs est de concevoir et d'implémenter une architecture sur puce optimale qui soit performante, faible consommation et de surface réduite dans une plate-forme matérielle/logicielle. Cet acte d'équilibrage entre ces diverses contraintes nécessite l'exploration des architectures aux niveaux d'abstraction plus haut que le niveau RTL. C'est pour cette raison, un intérêt est accordé pour adopter SystemC comme langage de conception au niveau système électronique (Electronic System Level : ESL).

La technique d'estimation de puissance ESL doit répondre à des exigences critiques. En effet, les architectures des SoCs sont soumises à diverses contraintes. Pour cela, les concepteurs ont besoin des résultats rapidement ainsi que le *feedback* sur la puissance et l'énergie consommées de tous les modules de la puce.

### I.7.2.1.2 Caractéristiques

La technologie d'estimation ESL fournit les informations énergétiques critiques requises par le concepteur de SoC lors de l'évaluation de la consommation au niveau Système-C. En effet, elle intègre avec le synthétiseur de Système-C des outils d'estimation exploités par les programmeurs pour optimiser les algorithmes. (Figure 6)

**Figure 6: ESL: Flot de conception**

### I.7.2.2 Power Theater

Réduire la consommation si tôt, avant la synthèse, économise considérablement la dissipation de puissance. Power theater est un ensemble d'outils garantissant une efficacité maximale de la puissance lors de la conception. (Sequence, 2005)

À travers Power Theater, Sequence offre des solutions rapides et précises aux niveaux RTL et logique qui analysent et réduisent la dissipation de puissance lors de la conception d'un SoC. Cet outil analyse, affiche et aide l'utilisateur à réduire la puissance dissipée dans la puce entière et au niveau de chaque module. Il a comme entrée du code Verilog, VHDL et Synopsys Liberty (.LIB)

### I.7.2.2.1 Avantages

Power Theater offre aux concepteurs divers avantages :

- Analyse de la puissance et de l'énergie assez tôt dans le flot de conception facilitant ainsi la réduction de la dissipation et le contrôle du coût énergétique.

- Assurer l'analyse « Zero-sim » de la puissance des modules RTL, sans recours aux vecteurs de tests : *testbenches*.

- Voir l'impact simultané de tous les modules communiquant (mémoire, I/O, contrôle du chemin des données) dans la puce.

- Déterminer les cycles critiques de dissipation.

### I.7.2.2.2 Méthodologie de réduction

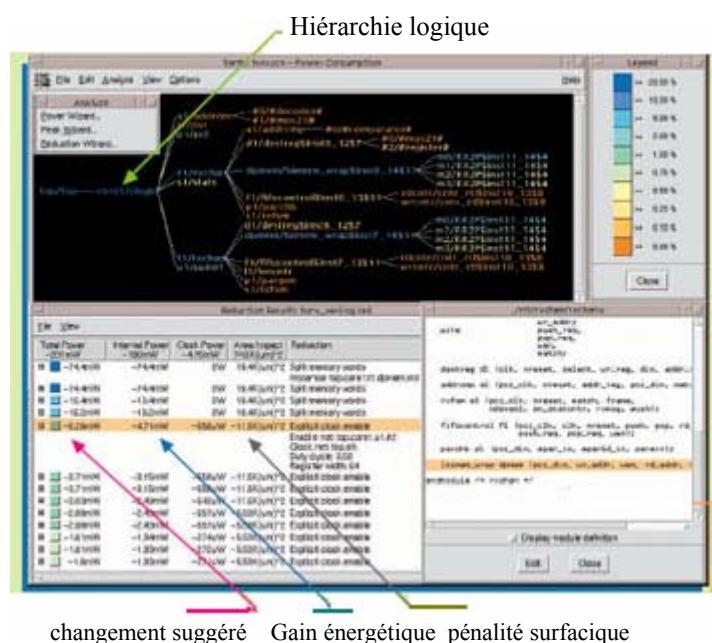

Cet outil intègre des agents de réduction de la consommation au niveau RTL appelés WattBots qui mesurent de façon automatique l'impact de tout changement potentiel de l'architecture sur la dissipation. (Figure 7)

**Figure 7 : Analyse de puissance avec le débogueur RTL Cool PowerTheater**

Chaque WattBots est conçu pour identifier un type spécifique de possibilité de réduction énergétique. En effet, WattBots intègre tous les principaux types de circuits pouvant être exploité lors de la conception, y compris le contrôle, le chemin de données, l'E/S, la mémoire et l'horloge. Et pour chaque possibilité identifiée, Power Theater propose :

- Des modifications RTL spécifiques,

-Une quantification du gain énergétique résultant, en tenant compte des diverses contraintes mises en jeu comme la surface.

De cette façon, le concepteur a la possibilité de choisir l'architecture la mieux adaptée aux contraintes de conception.

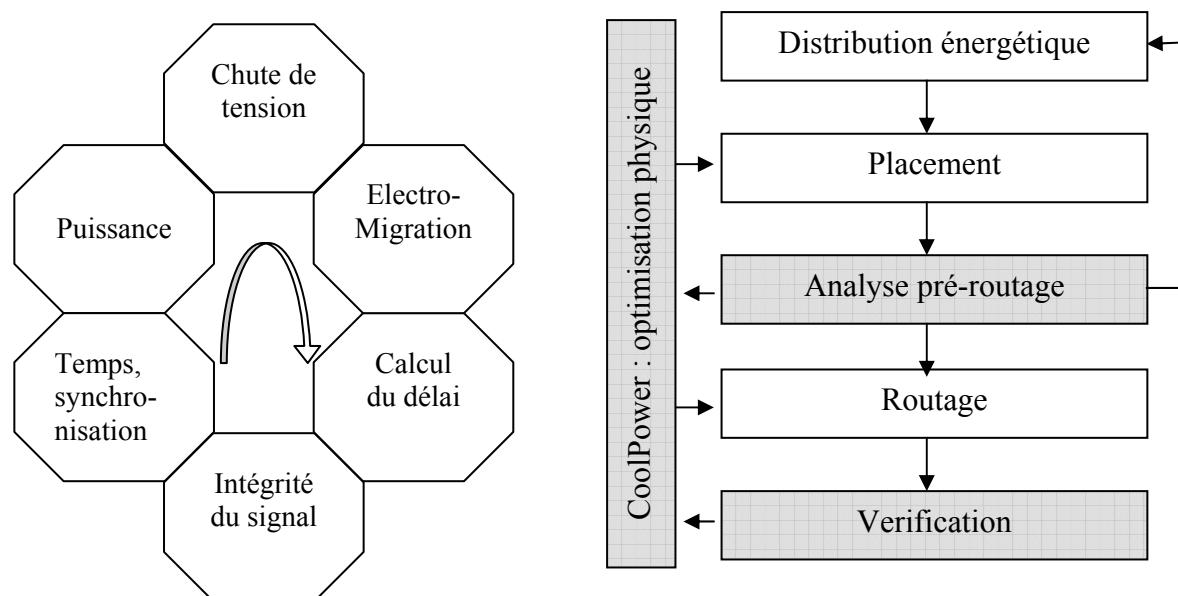

### I.7.2.3 Cool Time

#### I.7.2.3.1 Avantages

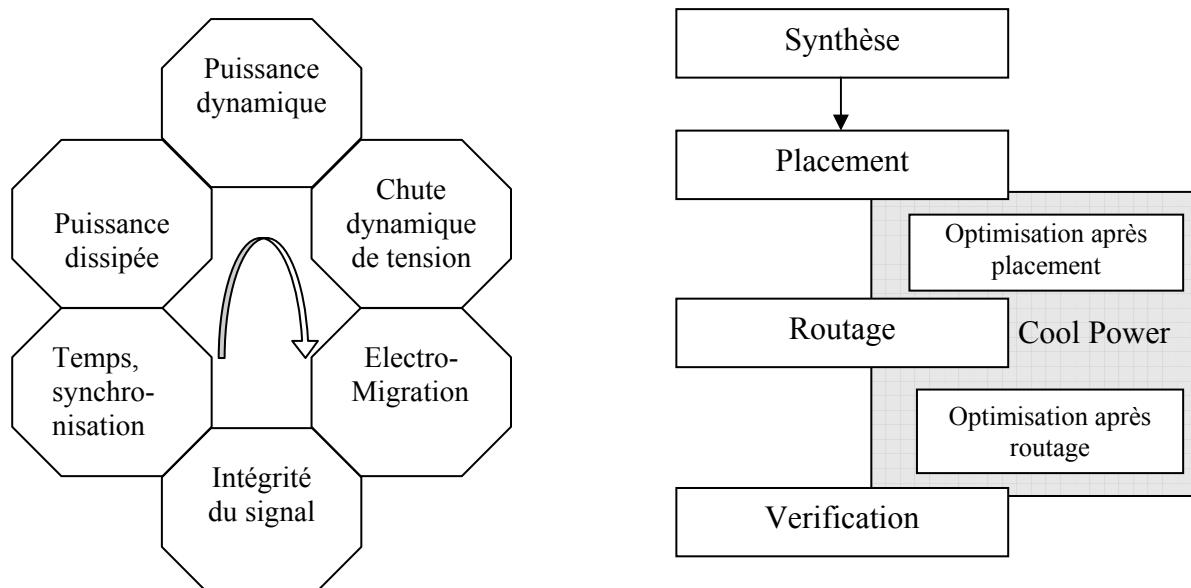

CoolTime (Sequence, 2005) est un moyen facilitant l'analyse simultanée de l'intégrité de la puce: la tension d'alimentation électrique et la synchronisation. En regroupant divers outils, CoolTime rend l'analyse des effets électriques interdépendants précise et convergente. Il partage une plate-forme commune avec CoolPower pour assurer une conception rapide qui tient compte des chutes de tension, courants de fuite et la synchronisation. (Figure 8)

**Figure 8 : Analyse électrique concorrente avec CoolTime**

#### I.7.2.3.2 Caractéristiques

- CoolTime peut être utilisé si tôt dans le flot de conception réduisant ainsi les changements exigés dans les étapes postérieures. En partant du placement initial, l'analyse du courant statique peut être faite afin de valoriser la consommation lors du routage. Ainsi on assure une chute de tension dynamique dans des marges acceptables lors de la conception.

- CoolTime permet l'analyse de la chute de tension dynamique. En effet, un modèle de caractérisation intégré dans l'outil génère des modèles de courant sous forme d'onde. Et avec une étude concurrente, CoolTime analyse les effets interdépendants des événements, des courants et des tensions lors du régime transitoire.

- Il supporte les techniques de simulation (testbenches) avec ou sans vecteurs de simulation. Contrairement aux techniques probabilistes, l'algorithme de création des stimulus prévoit la chute de tension au pire des cas.

- L'outil crée un modèle RLC complet de la puce ainsi que des parasites. Il supporte l'inductance mutuelle et les sources contrôlées de courant et de tension.

#### I.7.2.4 Cool Power

CoolPower (Sequence, 2005) prévoit et améliore la conception avant et après le routage. En effet, il offre à l'utilisateur la capacité d'optimiser de façon interactive la conception hiérarchique des millions de portes au niveau blocs.(Figure 9)

**Figure 9 : Analyse et optimisation électrique concurrente avec CoolPower**

En plus, l'outil réduit la dissipation statique et dynamique au niveau physique à l'aide de l'analyse concurrente de CoolTime tout en respectant la synchronisation et l'intégrité du signal. En effet, il réduit la puissance dynamique en appliquant et en testant divers changements sur le *netlist* qui optimisent les pertes énergétiques. Par ailleurs, CoolPower fixe automatiquement les problèmes provoqués par la chute de tension dynamique en insérant des capacités de découplage et en modifiant les placements pour éviter les points chauds.

En résumé, la plateforme Sequence offre une gamme d'outils payants orientée vers la conception et l'estimation des performances des SoC et des ASIC, mais non pas vers les DSPs commerciaux. Par ailleurs, cette plateforme reste encore un produit en cours de développement.

### I.7.3 SES Scanner

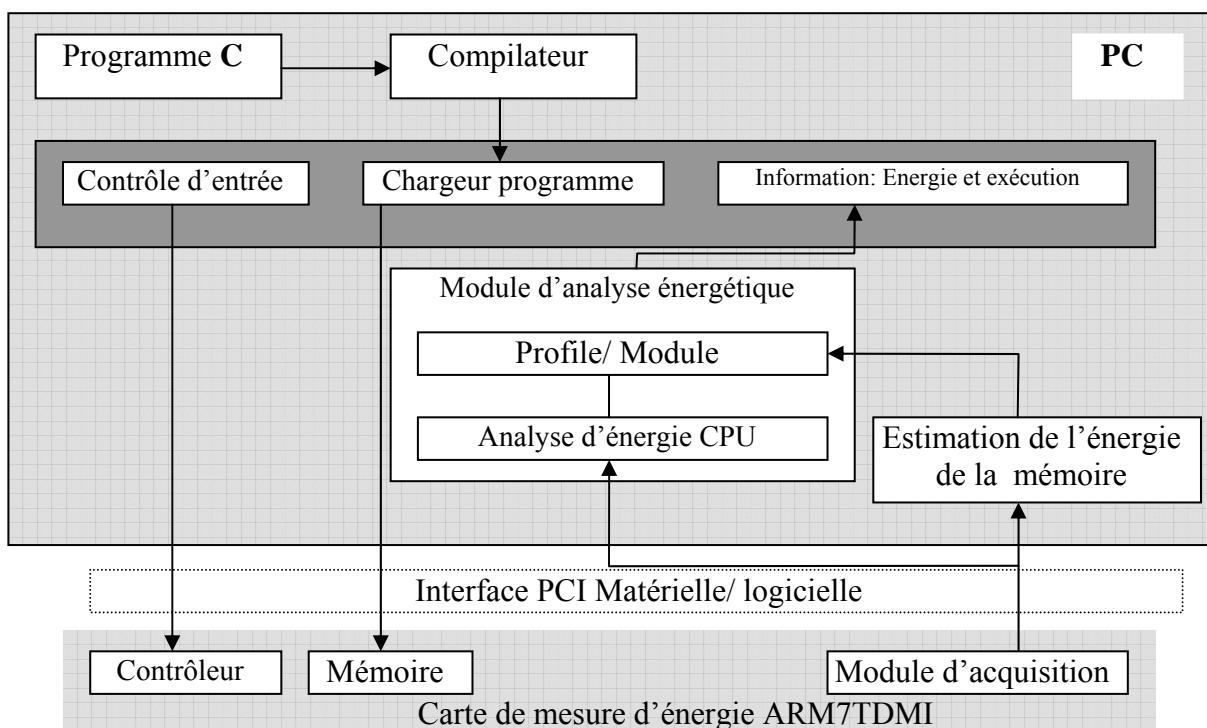

SES (Seoul national university Energy Scanner) (Shin et al., 2002) est un outil qui fournit des informations sur la puissance et l'énergie consommées par le programme embarqué au niveau cycle, en visant son optimisation. Il associe ces informations récupérées par mesure sur carte avec le code C. Avec le débogueur GNU, jouant le rôle d'interface, diverses informations sur la consommation sont extraites au niveau C facilitant à l'utilisateur d'identifier les points chauds de l'application embarquée. SES comporte 3 modules logiques : l'estimateur d'énergie, l'analyseur et l'interface utilisateur. (Figure 10)

**Figure 10 : Architecture du SES**

#### I.7.3.1 Module d'estimation d'énergie

Ce module comporte une carte de mesure et un estimateur de consommation de la mémoire. La carte est connectée au port PCI exploitant un module d'acquisition du profil en

---

temps réel facilitant la collection de la trace précise du système au niveau cycle. Cette carte comporte un cœur de processeur ARM7TDMI avec son contrôleur, le module d'acquisition et la mémoire programme.

Le module d'acquisition comporte un circuit de mesure de l'énergie au niveau cycle, une mémoire d'acquisition et le contrôleur du profil. La carte de mesure d'énergie fonctionne comme un émulateur du processeur équipé d'un circuit de mesure de la consommation au niveau cycle. Les informations collectées comportent une trace énergétique du cœur du processeur ainsi que la trace de la mémoire au niveau cycle. Une fois la trace est collectée, elle est transférée via le bus PCI vers l'estimateur de consommation de la mémoire.

Ce dernier, fonctionnant sur la machine hôte, est un simulateur logiciel qui intègre des modèles de consommation au niveau cycle de divers types de caches, de bus et de mémoires. Il génère un profil général de la consommation.

### I.7.3.2 Module d'analyse et interface utilisateur

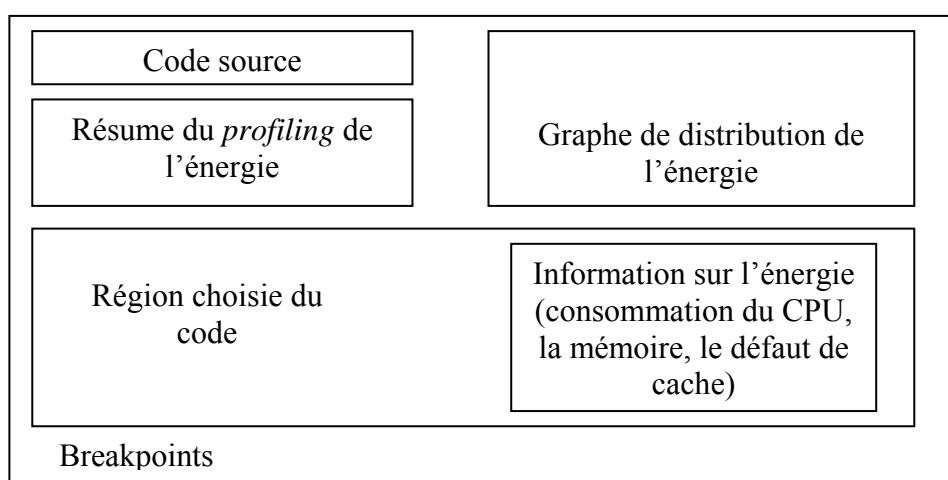

Ce module lie le profil énergétique du processeur cible et la mémoire avec le code source à différents niveaux C/ASM. Grâce à l'interface graphique, l'utilisateur peut avoir recours à diverses options : compilation, spécification de la partie du code à profiler, ajout des *breakpoints*, et chargement du programme. (Figure 11)

**Figure 11 : L'interface graphique de SES**

La limitation de cet outil est la dépendance envers la plateforme de mesures. En fait, pour tout type d'application, l'outil a recours à la carte d'acquisition d'infos sur la consommation. Ceci paraît un facteur limitatif pour son utilisation lors de la conception des applications.

---

## I.7.4 ORINOCO

La méthodologie de conception au niveau système de ChipVision permet d'identifier les points chauds de l'application aussi tôt dans le processus de conception, spécifiquement au niveau ESL (Electronic System Level). Pour cela, l'outil ORINOCO (Stanley et al., 2004) est employé dans le flot de conception HW. Il est conçu spécifiquement pour les applications de traitement de données et de signal.

### I.7.4.1 ORINOCO : Analyse de la puissance au niveau ESL

L'approche traditionnelle de la conception faible consommation est d'estimer et d'analyser la puissance au niveau RTL ou porte, et de modifier la conception en conséquence. Dans le meilleur cas, les blocs fonctionnels RTL sont modifiés, et re-synthétisés. Ce processus est répété jusqu'à ce que les résultats désirés soient réalisés. Toutefois, les réductions désirées en puissance peuvent souvent être réalisées en modifiant seulement l'architecture ou bien l'algorithme. Cependant, les modifications à ce niveau affectent non seulement la puissance, mais également d'autres métriques de performance ou bien le coût de la puce.

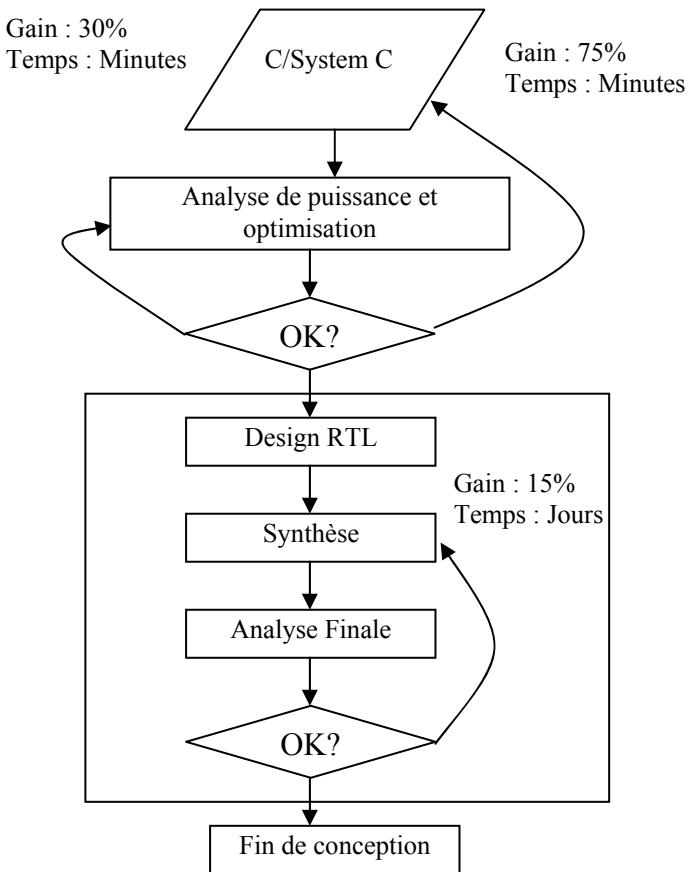

Avec ORINOCO, c'est possible d'optimiser la consommation au niveau système. La figure 12 montre le flot de conception et d'optimisation. La spécification du système est écrite à un niveau d'abstraction assez élevé (C/C++ ou SystemC). En partant de ces spécifications, des algorithmes réalisant la fonctionnalité du système sont développés et optimisés, généralement avec le même langage. La description algorithmique se compose d'une spécification exécutable ou d'une description fonctionnelle. L'architecture (mémoire, contrôleur et la structure de chemin de données) est générée pour implémenter les algorithmes. Lors de ce développement, diverses contraintes se présentent comme la puissance, la performance et la surface. Le problème qui se pose s'est qu'il y a peu d'outils structurés disponibles pour effectuer une telle analyse.

Au niveau ESL, ORINOCO choisit la plate-forme optimale selon cette méthodologie : Les divers algorithmes candidats sont analysés en terme de consommation et points chauds. Les algorithmes les plus prometteurs sont alors choisis et optimisés. Ceci est alors suivi par la création d'une architecture optimale. Les fonctions dont la consommation est optimale sont alors transformées en matériel. Ce processus d'estimation et optimisation de la consommation est itératif, et chaque itération nécessite des minutes ou des heures.

**Figure 12:** *flot de conception ESL*

#### I.7.4.2 Analyse d'algorithme et Optimisation

Avec ORINOCO, le « meilleur » algorithme est choisi parmi divers « candidats ». La puissance de chacun est identifiée selon la méthodologie représentée sur la figure 13. La spécification en C/SystemC est d'abord compilée puis profilée. Les informations ainsi générées sont réintégrées dans le code source. Les algorithmes sont alors exécutés, et les données résultantes du profil d'activité sont employées pour annoter une représentation appropriée de contrôle du flot de données (CDF).

Une architecture optimisée en consommation peut être tirée avec ORINOCO sans nécessité de synthèse complète grâce aux modèles de puissance créés pour chaque composant au niveau RTL. Ces modèles dépendent des données en entrée, des caractéristiques des composantes telles que le nombre de bits et l'architecture, et de la technologie des cellules. Ainsi, les modèles de puissance peuvent être générés automatiquement pour une technologie donnée. Et en utilisant l'activité des composants et les modèles de puissance, la puissance d'un composant peut être estimée.

**Figure 13:** Algorithme d'estimation de la puissance avec le *flux de contrôle de donnée*

Par ailleurs, les mémoires sont utilisées dans ce cas pour le stockage intermédiaire de l'information et la communication inter-blocs. Ainsi, elles ont un effet significatif sur la consommation. Diverses techniques d'optimisation des accès aux mémoires incluant les transformations de boucles et le co-emplacement de code peuvent être affectées simplement en réécrivant le code. Toutefois, l'outil n'est pas conçu pour estimer la consommation des processeurs et des bus commerciaux, de plus il ne tient pas compte de l'interaction avec l'environnement externe.

### I.7.5 EPRO

EPRO (Beak et al., 2004) est un outil fournissant des informations sur la performance et la consommation pour diverses applications réelles embarquées. Avec cet outil, des études de cas ont montré une réduction de 5,4 % sur la consommation de l'énergie et une amélioration de 4,4% au niveau performance. L'avantage majeur de ePRO est l'aptitude de faire le *co-profiling* (consommation et performance) en même temps.

### I.7.5.1 Architecture générale

ePRO nécessite trois modules physiques : la cible embarquée, un multimètre numérique et la machine hôte. Cet outil est conçu pour le processeur PXA255 de la famille TynuxBox basée sur l'architecture Xscale. L'avantage de cette architecture est la présence d'une unité monitrice de performance (PMU) présente au niveau architectural. Ceci mène à bien contrôler divers comportements du système : efficacité de la mémoire cache (instruction, donnée), la latence de l'étage *fetch*.

Afin d'effectuer des profils matériels sur l'énergie, on doit avoir recours à un multimètre digital fonctionnant à des fréquences élevées. Ce dernier est contrôlé à la fois par la machine hôte et la carte cible afin de collecter le profile énergétique via des *triggers* E/S.

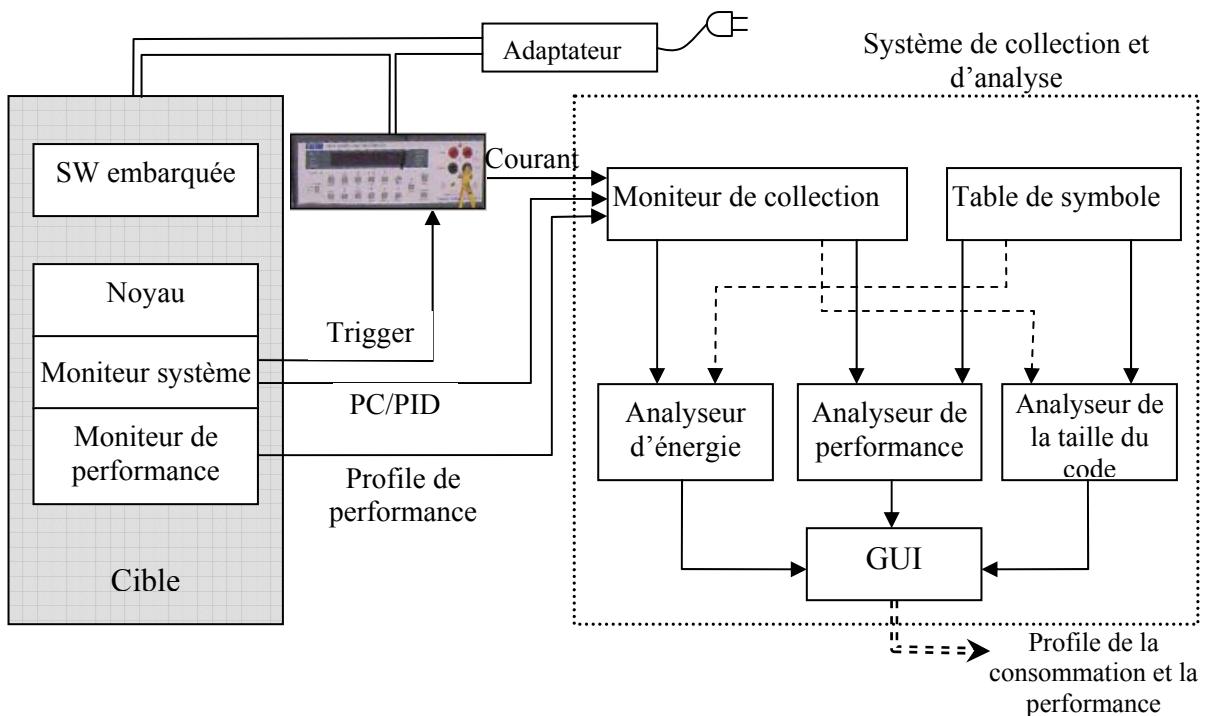

ePRO inclus 3 modules : le *profiler* d'énergie, le *profiler* de performance et l'interface graphique utilisateur (GUI). (Figure 14)

**Figure 14: Architecture de ePRO**

### I.7.5.2 Le *profiler* d'énergie

Ce *profiler* d'énergie comporte un moniteur système, un multimètre et un analyseur d'énergie. La trace énergétique est faite en deux étapes :

- La collection de données : Durant cette phase, le moniteur système collecte périodiquement les valeurs échantillonées du courant pour les envoyer à la machine hôte via

---

une interface Ethernet. En plus, il collecte les informations sur le système comme le compteur programme (PC), l'identificateur de processus (PID) à la même période.

- L'analyseur des données : Durant cette phase, l'analyseur énergétique analyse les valeurs échantillonnées du courant et les informations du système pour générer la trace énergétique. Et à l'aide d'une table de symbole générée par le compilateur croisé, la trace est *mappée* avec les diverses fonctions de l'application embarquée.

### I.7.5.3 Le *profiler* de performance

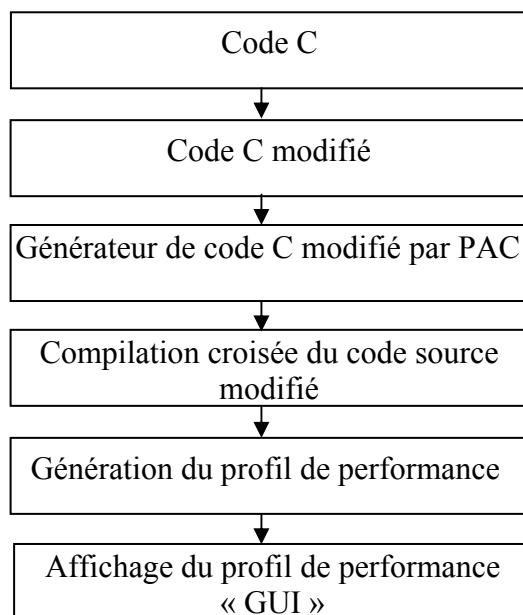

L'analyseur de performance comporte un modificateur de code qui a comme entrée un code à un haut niveau d'abstraction comme le langage C, et a comme sortie un code modifié. Le PAC (Analyse de Performance de Code) est inséré à ce nouveau code.

Le code généré par le PAC est compilé et exécuté sur le processeur cible. Ceci permet de générer le profil de performance (efficacité de la cache d'instruction et de donnée, les requêtes sur le bus). (Figure 15)

**Figure 15:** Organigramme global de profil de performance

### I.7.5.4 L'interface utilisateur

Les traces de l'énergie et de performance sont présentées à travers une interface graphique facilitant l'identification des points chauds de l'application embarquée. En effet, les caractéristiques énergétiques de chaque fonction sont présentées à travers cette interface.

L'inconvénient majeur de cet outil est son recours à la plateforme pour le *profiling*. Ce qui impose sa présence dans tous les tests.

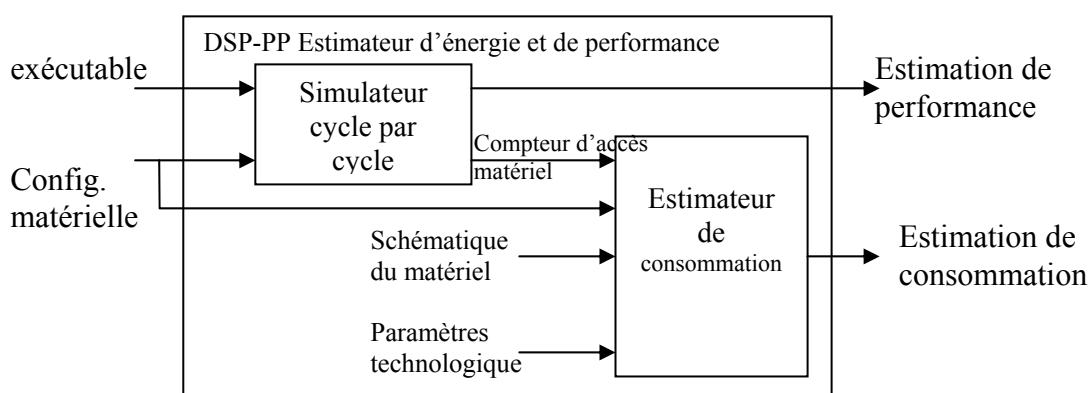

## I.7.6 DSP-PP

Il a été largement accepté que la simulation, au niveau porte et circuit, est infaisable pour évaluer la consommation d'une exécution logicielle pour des systèmes de calcul complexes. Pour cela, un jeu complémentaire d'approches basé sur l'utilisation de simulateurs architecturaux de consommation au niveau cycle précis est apparu. Ces simulations peuvent être applicables aux processeurs modernes super scalaire (avec les pipelines assez profonds). (Li et al., 2003).

On peut citer le DSP-PP (Minh et al., 2003) qui est un outil de simulation RTL permettant l'estimation de la puissance dissipée pour les DSPs. Il est écrit en C++ afin de profiter de ce haut niveau d'abstraction. (Figure 16)

**Figure 16:** Diagramme de l'estimateur DSP-PP

DSP-PP emploie la simulation détaillée au niveau cycle de tous les composants du DSP: les chemins de données et l'interconnexion et estime exactement la valeur de puissance dynamique, de court circuit et de fuite de chaque composant du DSP. Les composants du DSP sont modélisés comme des objets intégrants le modèle de consommation.

Le DSP-PP est composé de deux composants: le simulateur de performance au niveau cycle (CPS) et l'estimateur de dissipation de puissance (PDE).

- Le CPS est un simulateur "piloté par l'exécution" il accepte comme entrée l'exécutable obtenu par compilation et la configuration architecturale du DSP. Il simule cycle par cycle l'exécution de l'instruction ainsi que les données. Il génère comme sortie des statistiques sur la performance, et le nombre d'accès matériels cycle par cycle.

- Le PDE est constitué de modèles de consommation des différents composants. Il accepte comme entrée le nombre d'accès matériels du CPS et la configuration de l'architecture du DSP afin de générer une estimation de la puissance

---

Cependant, la simulation au niveau cycle-précis entraîne une vitesse de simulation extrêmement lente, empêchant l'efficacité de la recherche d'espace de conception. C'est particulièrement vrai en simulant des applications complexes employant des modèles de processeur détaillés. À cause de cela, la simulation basée sur le modèle de puissance ne peut pas être employée pour l'évaluation de puissance de logiciel pendant l'exécution.

## ***I.8 Interprétation***

De nombreux travaux se sont focalisés sur la modélisation de la consommation au niveau instruction, où la consommation du code est obtenue en estimant celle de chaque instruction du code. Ces méthodes sont généralement inefficaces pour les architectures complexes ayant diverses unités de traitement communicantes. De plus, certains outils ne ciblent pas les DSP commerciaux traités dans ce travail (C62, C55 et le C67). Par ailleurs, les gains importants en terme de consommation sont réalisés aux hauts niveaux d'abstraction où les décisions d'implantations logicielles et/ou matérielles sont faites. Ceci permet de compenser la complexité croissante des applications et d'intégrer la consommation au début du flot de conception mixte. Par ailleurs, afin de pouvoir dimensionner le système dès le début du flot de conception, des modèles de performances temporelles et énergétiques sont nécessaires afin de caractériser l'influence des paramètres de l'application et de l'architecture sur la consommation.

## ***I.9 Conclusion***

Dans ce chapitre, on a présenté les diverses techniques et outils d'estimation et d'optimisation de la consommation. Grâce à ces outils, le concepteur a la possibilité d'exploiter plus de ressources ‘faible consommation’ et d'offrir les performances maximales aux utilisateurs. Par ailleurs, les décisions de conception les plus efficaces dérivent du choix et de l'optimisation des architectures et des algorithmes aux niveaux les plus hauts. Et afin de mieux guider le concepteur lors de la conception des architectures complexes, il est nécessaire d'adopter une méthodologie d'exploration de l'espace des solutions possibles qui soit plus globale (toute l'architecture). Cette méthodologie permettra d'avoir une solution optimale qui respecte les diverses contraintes de l'application.

---

*Chapitre*

***II***

# Exploration de l'espace des solutions

## Chapitre II. Exploration de l'espace des solutions

### II.1 Introduction

Les futurs systèmes mobiles ne cessent d'évoluer en intégrant de plus en plus de nouvelles fonctionnalités. A titre d'exemple, les téléphones portables actuels intègrent de la musique, la vidéo, les jeux, le GPS, la capture d'image, l'accès à Internet, le stockage de données, etc. Et ceci, tout en gardant une bonne autonomie et une masse ne dépassant pas les 150 grammes. Cette multitude de fonctionnalités favorise généralement des architectures multiprocesseurs ayant des performances élevées. Pour garantir la faisabilité de ces systèmes, il faut donc prospecter de nouvelles solutions architecturales logicielles et matérielles garantissant une performance élevée, une grande flexibilité et une faible consommation (Figure 17). Seule une approche globale permettra de caractériser et d'optimiser efficacement ces systèmes. (Maalej, 2007)

De plus, l'optimisation d'un système ne s'effectue pas seulement au niveau de la conception de ces composants, mais également au niveau du choix d'une architecture générale. Le choix d'une technologie par rapport à une autre et le choix des unités de traitement, peuvent devenir des problèmes critiques lorsque la gestion de la consommation représente un critère essentiel. Ainsi au lieu de rechercher un périphérique, entre autre une architecture, plus performante, il peut parfois être préférable de changer complètement de technologie.

**Figure 17 : Flexibilité des architectures vis à vis de leurs performances (Benoit et al., 2004)**

---

Dans ce chapitre, on présente les méthodes d'exploration de l'espace des solutions, le flot de conception général des systèmes embarqués en terme d'outils, de métriques et de modèles d'exploration architecturale (Hw/Sw). Ce chapitre s'intéresse aussi aux algorithmes d'exploration de l'espace des solutions.

## II.2 Conception mixte

L'exploration de l'espace de conception est entreprise à partir des descriptions de haut niveau tel que le C/VHDL en tenant compte éventuellement d'une architecture cible. Cela permet de considérer un compromis des réalisations logicielles/matérielles pour satisfaire les performances et les contraintes à travers les bons choix de l'architecture logicielle/matérielle.

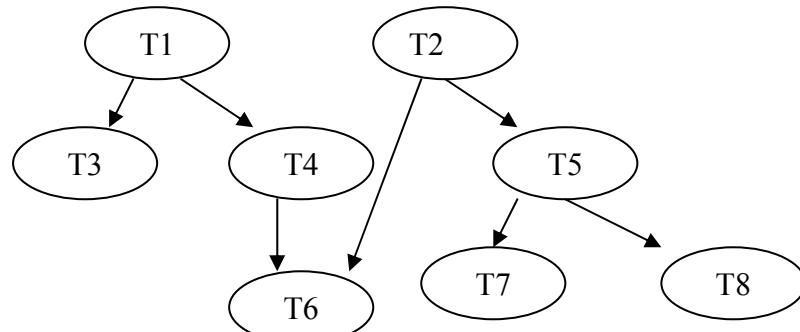

Par ailleurs, l'exploration de l'espace des solutions est parmi l'une des étapes nécessaires lors de la conception des systèmes embarqués. Elle permet de surmonter le problème de la complexité de l'espace afin d'atteindre la solution adéquate rapidement. Il est à signaler que le choix de la meilleure solution à un haut niveau d'abstraction n'est pas assez simple vu le nombre de combinaisons architecturales possibles. Par ailleurs, la complexité de l'exploration est liée à la complexité de l'application. En effet, pour une application contenant  $n$  tâches fonctionnant sur une architecture monoprocesseur, le nombre de solutions possibles  $U$  est établi par la loi suivante (Bagdadi et al.,2002):

$$U_n = \sum_{q=1}^n \sum_{i=0}^q \frac{(-1)^{q-i} i^n}{(q-i)! i!} \quad (5)$$

Pour le cas d'une architecture multiprocesseur ( $p$  processeurs), le problème se complique plus. Le nombre de solutions possibles sera :

$$U_n^p = \sum_{q=1}^n p^q \sum_{i=0}^q \frac{(-1)^{q-i} i^n}{(q-i)! i!} \quad (6)$$

Prenons le cas d'un problème composé de 10 tâches fonctionnant sur 3 processeurs, l'espace des solutions possibles dépasse dans ce cas  $10^7$  combinaisons possibles. Le concepteur d'un tel système est incapable généralement de gérer et d'évaluer cet ensemble de solutions ni manuellement ni d'une manière exacte.

Il est à signaler que la problématique d'exploration de l'espace des solutions ne se limite pas à l'étude des combinaisons possibles (ordonnancement et partitionnement). En fait, les systèmes embarqués sont souvent soumis à diverses contraintes. Le temps réel et la

---

consommation sont parmi les exigences de ces systèmes vu qu'ils sont toujours en interaction avec leur environnement extérieur et qu'ils nécessitent beaucoup de calcul.

### ***II.3 Éléments caractéristiques des flots de codesign***

L'exploration de l'espace des solutions basse consommation nécessite un certain nombre d'informations relatives à l'application d'une part et aux modèles de performances d'autre part. Par ailleurs, un besoin de modèles d'estimation et de performance suffisamment riches et paramétrables s'impose lors de l'exploration. Dans ce qui suit, on présente les points clés de cette dernière:

- La spécification : elle est un point important du flot de conception dont le choix peut avoir un impact sur les résultats. Il existe une variété de modèles et de langages utilisés (Lustre, SDL, CDFG, System-C, etc). Ils permettent d'exprimer des notions telles que : la concurrence, la hiérarchie, les communications, la synchronisation, le temps, etc.

- La simulation : elle se retrouve à plusieurs niveaux d'abstraction dans le flot de conception. Le niveau de détails est plus important au niveau d'abstraction le plus bas et il diminue au fur et à mesure que l'on remonte vers le niveau système. Plus le niveau de détails est élevé plus les temps de simulation sont longs. Au niveau système, la simulation est de type fonctionnel, elle permet de vérifier que le système est fonctionnellement correct sans se préoccuper des détails d'implantations.

- L'architecture : Un flot de codesign est souvent orienté vers un type d'architecture. La modélisation des architectures permet d'évaluer les performances et les coûts d'implémentation de la spécification et ainsi de guider les choix de partitionnement. Les premières méthodes de codesign considéraient des modèles d'architecture simples composés d'un processeur et d'un accélérateur matériel dédié (ASIC). D'autres méthodes permettent de cibler des architectures hétérogènes composées de plusieurs types de processeurs et d'accélérateurs ainsi que des hiérarchies de mémoires (Bianco *et al.*, 1998), (Auguin *et al.*, 2001), (Marteil *et al.*, 2006). Enfin, il existe des méthodes permettant de gérer les architectures reconfigurables (souvent à base de FPGA), (Li *et al.*, 2000), (Bossuet *et al.*, 2003) (Elleouet *et al.*, 2006).

- Les métriques : Les étapes du processus d'exploration et plus particulièrement le partitionnement, peuvent être guidées par des métriques caractérisant l'application. Ces métriques permettent de guider le concepteur et les outils quant aux choix de l'architecture et du partitionnement. Dans (Sciuto *et al.*, 2002), des métriques relativement fines sont définies

---

pour caractériser l'affinité entre les fonctions d'une application et trois types de cibles architecturales : processeur à usage général (GPP), processeur de signal numérique (DSP) et ASIC. Les métriques, qui résultent de l'analyse du code 'C' de l'application, permettent de repérer les séquences d'instructions qui peuvent être soit orientées DSP, orientées ASIC (instructions de niveau bit,...) ou orientées GPP (structure de test, ratio d'instructions d'entrées/sorties,...). Ces métriques servent ensuite pour guider l'outil de partitionnement logiciel/matériel.

- Partitionnement : que celle-ci soit manuelle ou automatique, son but est de répartir les "fonctions" de l'application sur les parties logicielles et matérielles de l'architecture cible. Ce processus est réitéré jusqu'à ce qu'une solution ou un ensemble de solutions satisfaisantes ait été trouvé.

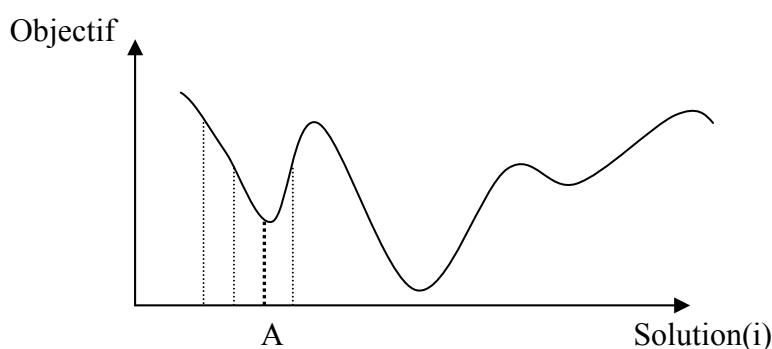

- Exploration de l'espace de solutions : Le résultat de l'exploration de l'espace de conception peut prendre la forme, soit d'une solution unique, soit d'un ensemble de solutions. Les méthodes qui fournissent à l'utilisateur une solution unique à partir d'un sous-ensemble restreint de possibilités, visent le plus souvent à trouver la solution optimale au problème alors que les méthodes qui fournissent un ensemble de solutions visent en général à trouver des solutions qui respectent l'ensemble des contraintes sans forcément être optimales. En effet, à un niveau d'abstraction élevé, la précision n'est pas assez suffisante pour garantir avec certitude que la solution soit optimale (car trop de détails d'implantation sont inconnus). Il est ainsi plus judicieux de conserver un ensemble de solutions "prometteuses" qui seront ensuite estimées à un niveau inférieur, conduisant à un ensemble de solutions plus réduit. La réitération de ce principe permet ainsi de converger vers une solution unique.

Dans cette partie, les étapes essentielles du flot de conception mixte typique sont présentées. Dans la section suivante, quelques outils de codesign seront présentés.

## **II.4 Méthodologies et outils**

### **II.4.1 Introduction**

Bien que les méthodes de réduction de puissance et d'énergie soient plus efficaces une fois adressées le plutôt possible dans le processus de conception (globalement au niveau système); la majorité des travaux existants sur l'optimisation de puissance adressent séparément les parties logicielles, matérielles et de communications après avoir décidé de l'architecture cible du système. Quelques approches de co-design tiennent compte d'un tel but à un niveau d'abstraction plus élevé. Ces approches commencent en général par une étape

d'estimation de la consommation des parties du système (tâches, fonctions, communications etc.) pour déterminer ensuite, et le plutôt possible, la consommation totale du système.

## II.4.2 Outils de codesign

Le tableau 4 présente quelques environnements de codesign développés soit par les groupes de recherche universitaires, soit dans l'industrie

**Tableau 4 : Comparatif des environnements de codesign (Abdennour, 2004)**

|                | Type d'application                               | Langage de spécification           | Approche de conception                                                                           | Architecture cible                                                                                                  |

|----------------|--------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| <b>Ptolemy</b> | TSI                                              | Flot de donnée synchrone           | Découpage automatique orienté logiciel                                                           | Multi-processeur + ASIC                                                                                             |

| <b>Vulcan</b>  | Systèmes temps réel                              | HardwareC (extension de C)         | Découpage automatique orienté matériel (contrainte de temps et coût)                             | Mono-processeur, ASIC, bus et mémoire                                                                               |

| <b>Cosyma</b>  | systèmes temps réel embarqué                     | Cx (extension de C)                | Découpage automatique orienté logiciel (contraintes de temps+ coût en surface)                   | processeur+ co-processeur ou multi-processeur et Mémoire partagée pour les Coms                                     |

| <b>SpecSyn</b> | Système de contrôle et de communication          | SpecCharts                         | -pré-estimation<br>- découpage automatique ou manuel<br>- raffinement<br>- implantation          | Multi-processeur processeurs+ ASICs+ASIP + et Bus, mémoire pour lesComs                                             |

| <b>Polis</b>   | systèmes temps réel embarquées de contrôle       | CFSMs                              | - découpage manuel,<br>-ordonnancement,<br>- implantation                                        | Multi-processeur microcontrôleurs avec des RTOS + ASICs et Ports d'E/S (Automatiquement générés) pour les coms      |

| <b>Cosyn</b>   | Système temps réel embarqués                     | Graphe de tâches                   | - Estimation<br>-Découpage automatique contraintes de temps + coût en surface et en consommation | Multi-processeur processeurs+ ASICs+FPGAs et point-à-point, bus, réseaux de communication locale LAN) pour les coms |

| <b>CODES</b>   | Les systèmes de communication                    | RDP, StateCharts                   | - modélisation<br>-partitionnement<br>- simulation<br>- intégration                              | Multiprocesseur Processeurs + mémoire + ASICs + FPGA                                                                |

| <b>CoWare</b>  | Traitement de signal et système de communication | C (SystemC)<br>HDL (VHDL, Verilog) | - découpage manuel<br>- synthèse d'interface, - ordonnancement, - cosimulation                   | Multiprocesseur Processeurs + DSPs+ ASICs et des coms Point-à-point avec un protocole de rendez-vous                |

Dans ce tableau les aspects de comparaison sont :

- Les types d'applications ciblées,

- Le langage de spécification du système,

- L'approche de conception,

- L'architecture cible,

- Les types des communications logicielle/matérielle utilisées.

Dans la section suivante, on va présenter en détails d'autres outils d'exploration basse consommation ainsi que les limitations de ces environnements.

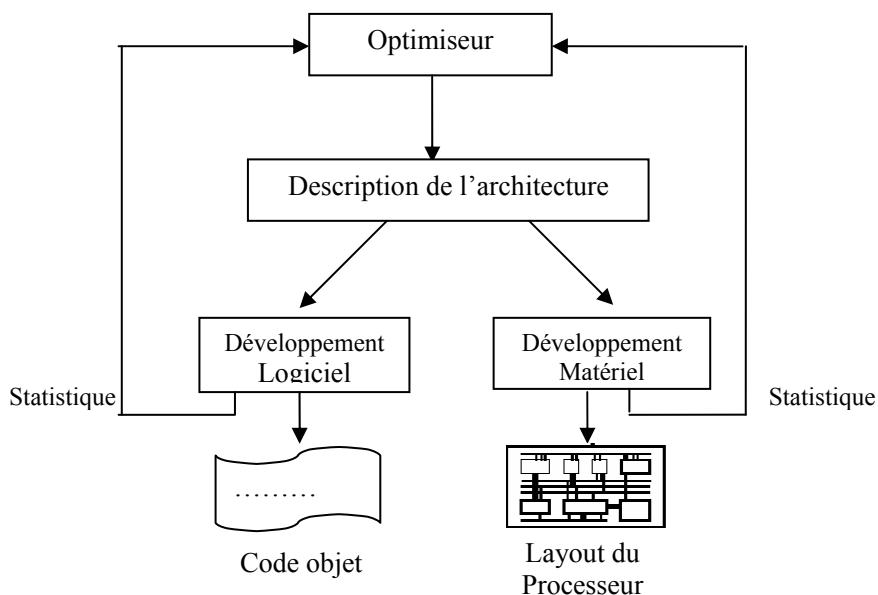

### II.4.3 L'environnement MOVE

Cet outil permet de réaliser *automatiquement* un ASIP pour le traitement d'image à partir d'une spécification haut niveau (Heikkinen *et al.*, 2002). L'architecture cible est la TTA (Transport Triggered Architecture). Son principe est semblable à l'architecture VLIW : elle permet d'effectuer plusieurs opérations en un seul cycle d'horloge en utilisant un réseau de transport (9 bus) de données, couplé à des unités fonctionnelles (multiplieurs, accumulateurs, registres...). Les avantages de cette technique sont la flexibilité, la simplicité et la facilité d'extension du système. La conception se base sur l'utilisation d'une plateforme (appelée MOVE) pour la conception automatique de processeurs, formée par un système de développement HW/SW et un optimiseur. (Figure 18).

**Figure 18 : L'architecture MOVE**

Le système explore l'espace de solutions (combinaison de plusieurs choix d'architecture) pour trouver la meilleure solution selon le critère rapport coût/performance. Le système permet ainsi d'ordonnancer l'application envisagée sur plusieurs architectures. L'aspect faible consommation n'est pas traité clairement dans cette approche.

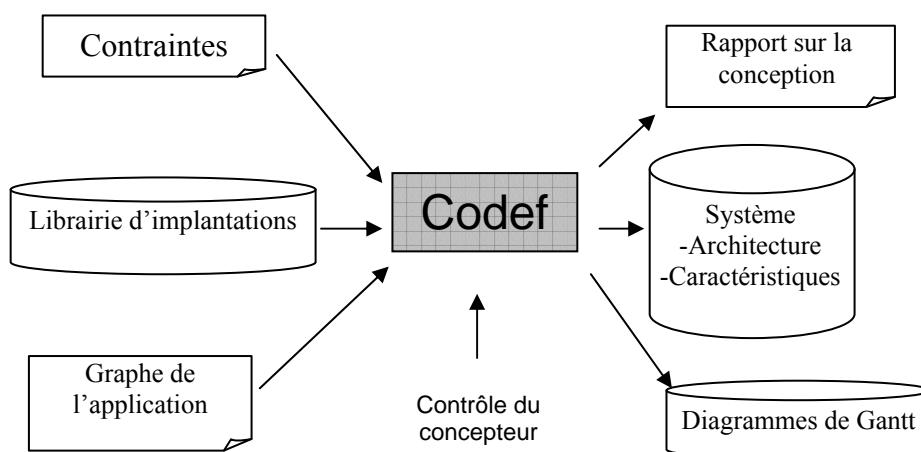

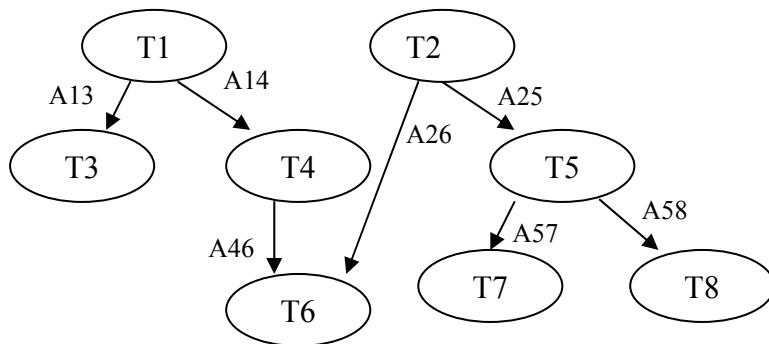

#### II.4.4 L'outil Codef-LP

Codef-LP (figure 19) (Guitton et al., 2003) développé à l'université de Nice propose une méthodologie permettant d'extraire une architecture monoprocesseur qui satisfait les contraintes temps, surface et qui minimise les pics de courants. La description de l'application en graphe de tâche ainsi que les contraintes et la librairie de modèles sont l'entrée de l'outil Codef. Ce dernier génère un *mapping* de l'application en utilisant une heuristique d'exploration basée sur le glouton. Afin d'optimiser davantage la consommation, des raffinements manuels en variant la fréquence sont faits suite à l'exploration automatique. L'estimation de la consommation des modules matériels est faite avec l'outil WattWatcher qui nécessite une synthèse. Alors que celle en logicielle est faite avec Vestim qui est basé sur la méthode d'estimation au niveau assembleur ce qui nécessite la compilation du code C. Par ailleurs, le modèle de consommation considère que la consommation suit la loi  $P=KCFreqV^2$ . L'exploration dans cette méthodologie se limite au changement manuel de la fréquence/Vcc ou au changement du processeur.

**Figure 19 : Description de l'outil Codef**

Toutefois, cet outil n'est pas disponible, il traite des architectures monoprocesseur, il ne tient pas compte de la communication. De plus, il se base sur une méthode au niveau

assembleur lors de l'estimation de la consommation de la partie logicielle, ce qui est compliqué pour les architectures VLIW. Par ailleurs, l'heuristique du glouton adoptée pour l'exploration n'est pas assez efficace vu qu'elle construit la solution pas à pas sans revenir sur ses décisions de choix. En plus, l'outil repose sur une librairie de modèles non paramétrable. En effet, une tâche peut avoir plusieurs modèles de performances selon les paramètres algorithmiques et/ou architecturales (taille de l'image, fréquence, cadence, etc.).

#### II.4.5 L'outil Mogac

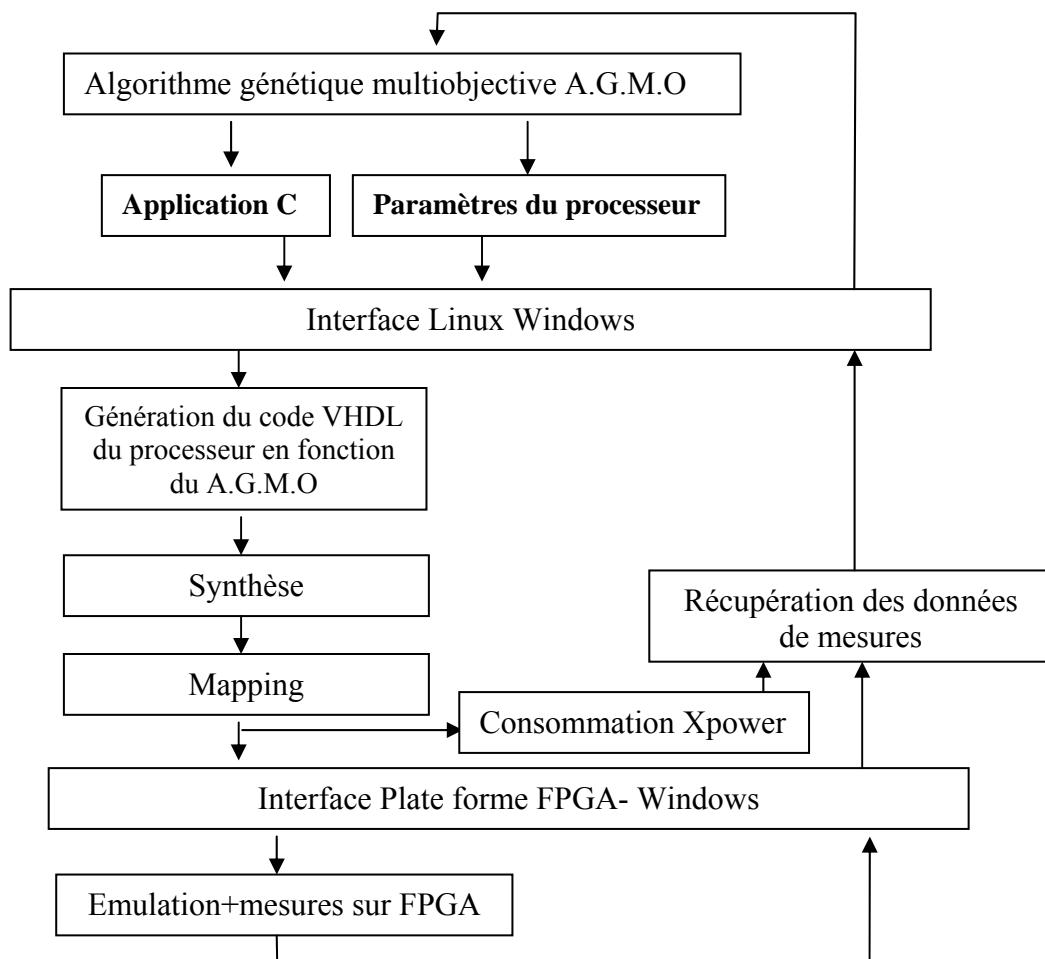

Mogac (Dick et al., 1998) développé à l'université de Princeton est un outil de co-synthèse logicielle/ matérielle. Il *partitionne* et ordonne la spécification de l'application décrite en graphe de tâche périodique. Pour cela l'outil exploite un algorithme génétique multiobjectif qui échappe des minimums locaux. Le coût et la consommation sont optimisés sous des contraintes de temps réel. Par ailleurs, l'outil tient compte de la consommation de la communication. Par contre, l'outil ne tient compte ni de l'influence de la tension d'alimentation ni de la fréquence. Par ailleurs, il ne traite ni la surface ni la consommation des mémoires. (Figure 20)

Figure 20 : Description de l'outil Mogac

Avec l'outil Mogac (Figure20), une exploration multi-objective est faite en terme de coût et de consommation. Les solutions pareto-optimales sont extraites par l'outil grâce à l'algorithme génétique. Toutefois, cet outil, conçu au départ pour optimiser essentiellement le

coût, n'est pas disponible. Aucune indication sur les méthodes d'estimation des performances n'est indiquée ni au niveau tâche ni au niveau système.

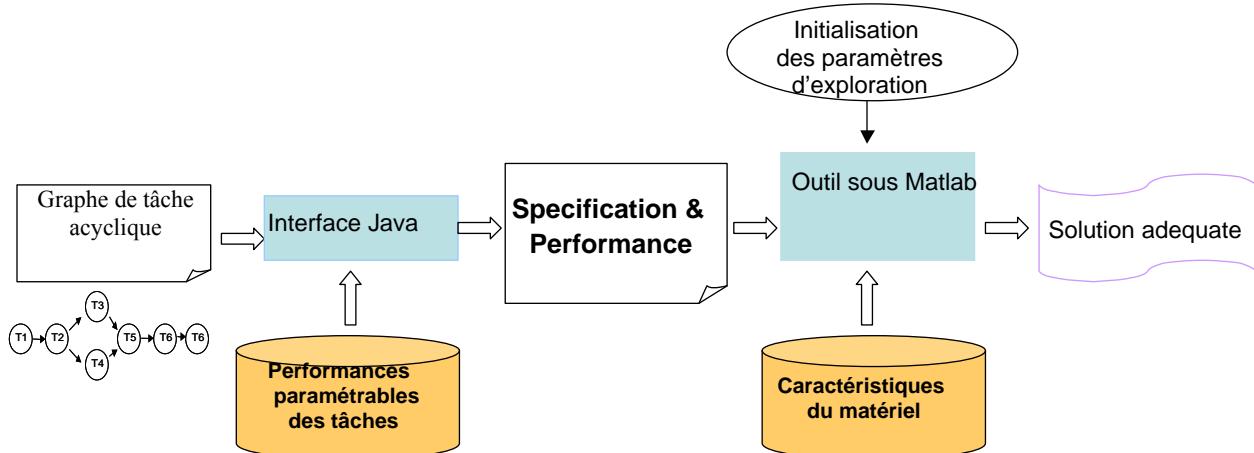

#### II.4.6 L'outil Cosyn-LP

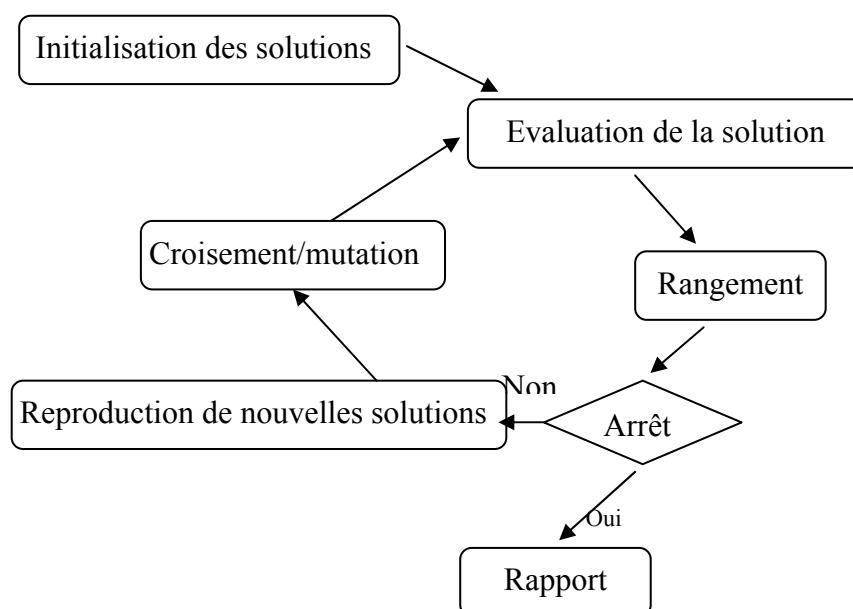

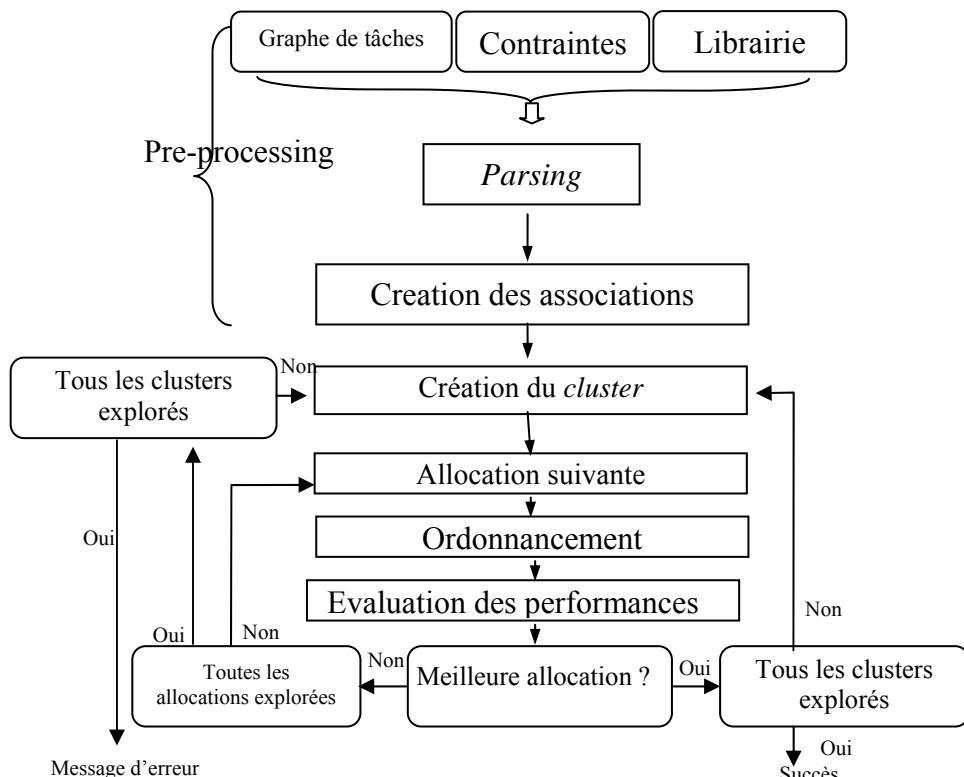

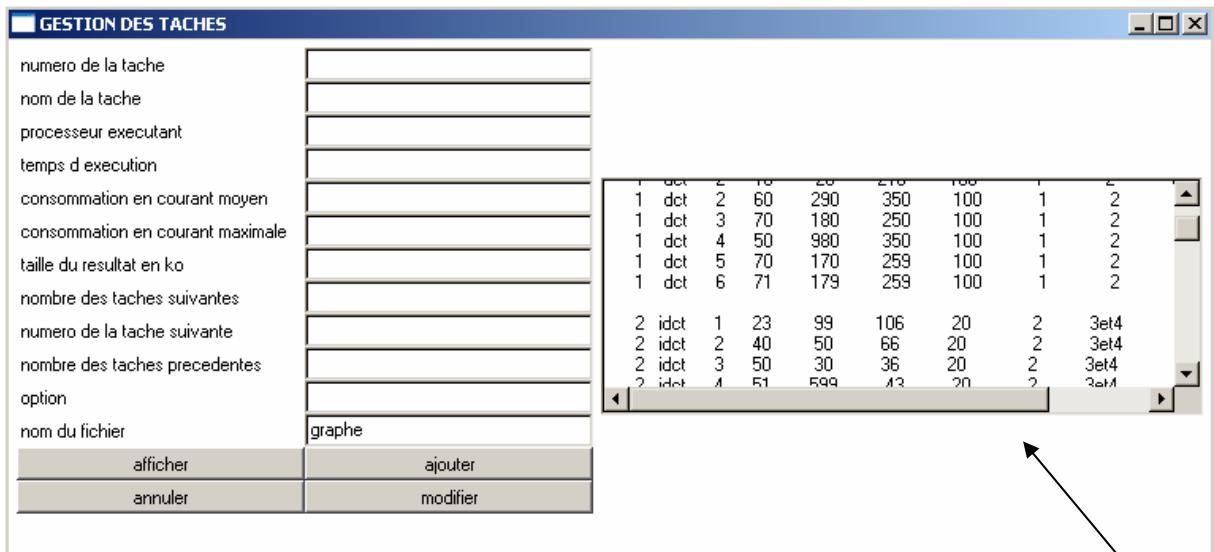

L'outil Cosyn-LP (Bharat et al., 1999) développé à l'université de Princeton est un outil de co-synthèse qui part d'une spécification en graphe de tâche périodique avec des contraintes de temps réel afin de générer une architecture à faible coût qui respecte les contraintes. Ces contraintes ainsi qu'une bibliothèque de modèles sont fournies à l'outil. L'approche se base sur une combinaison d'ordonnancement préemptif et non préemptif afin d'ordonner les tâches. La technique d'exploration se base sur le regroupement de tâches (Clustering). (Figure 21)

**Figure 21 : Description de l'outil Cosyn-LP**